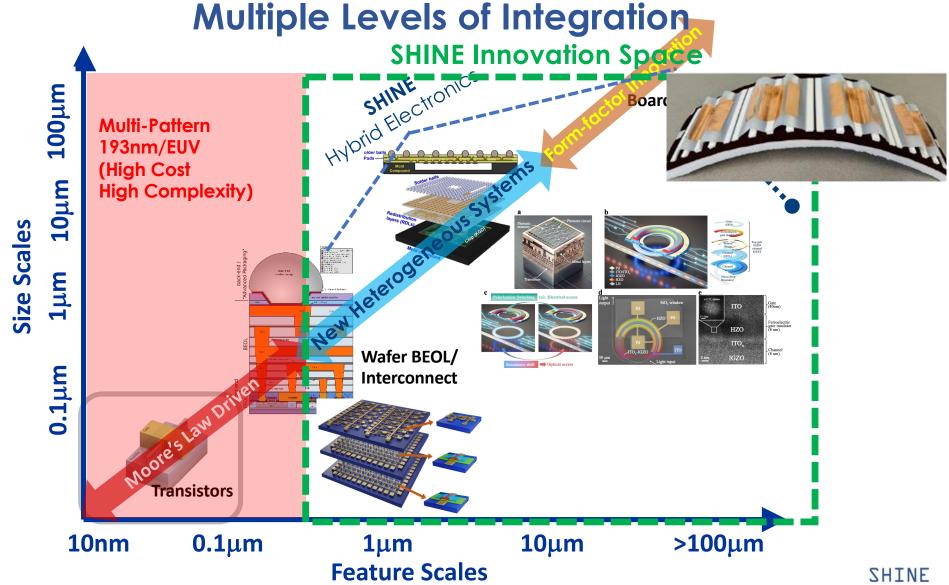

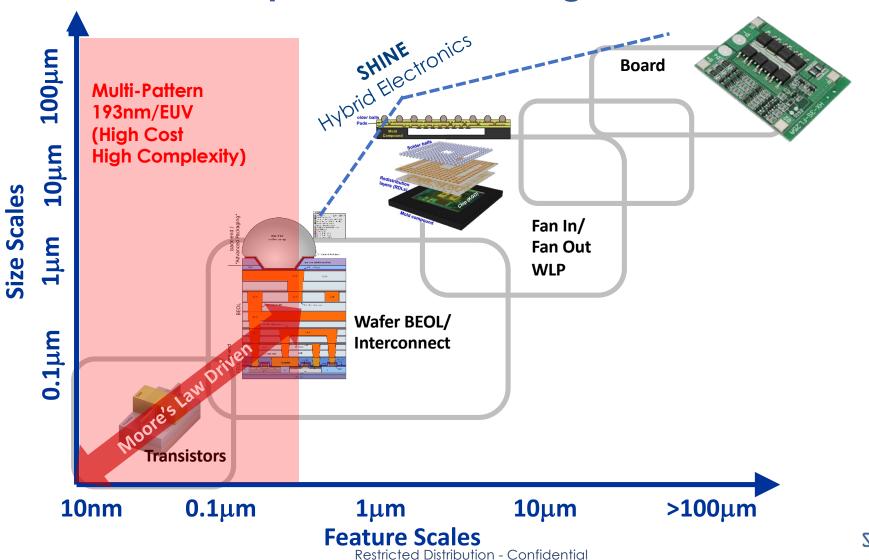

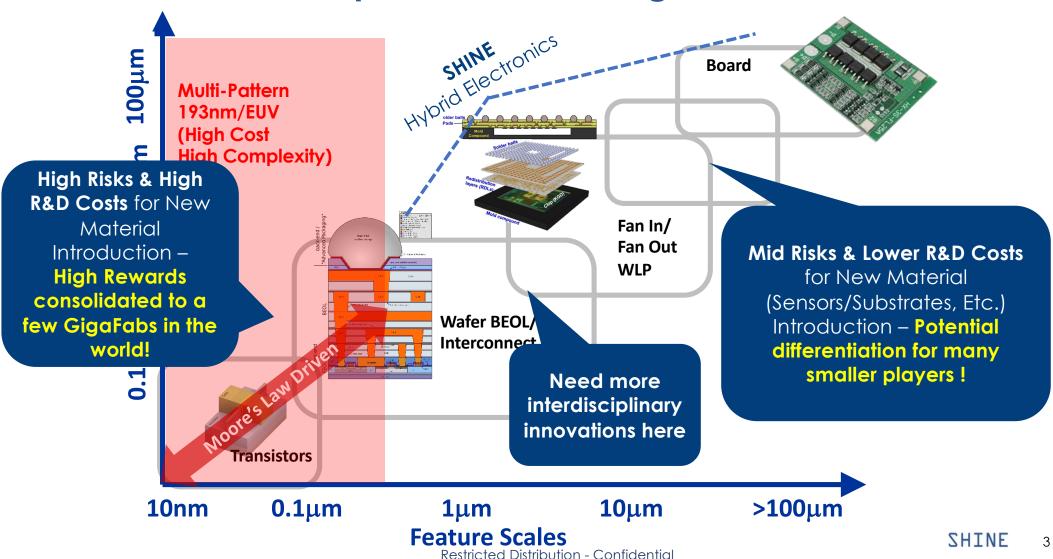

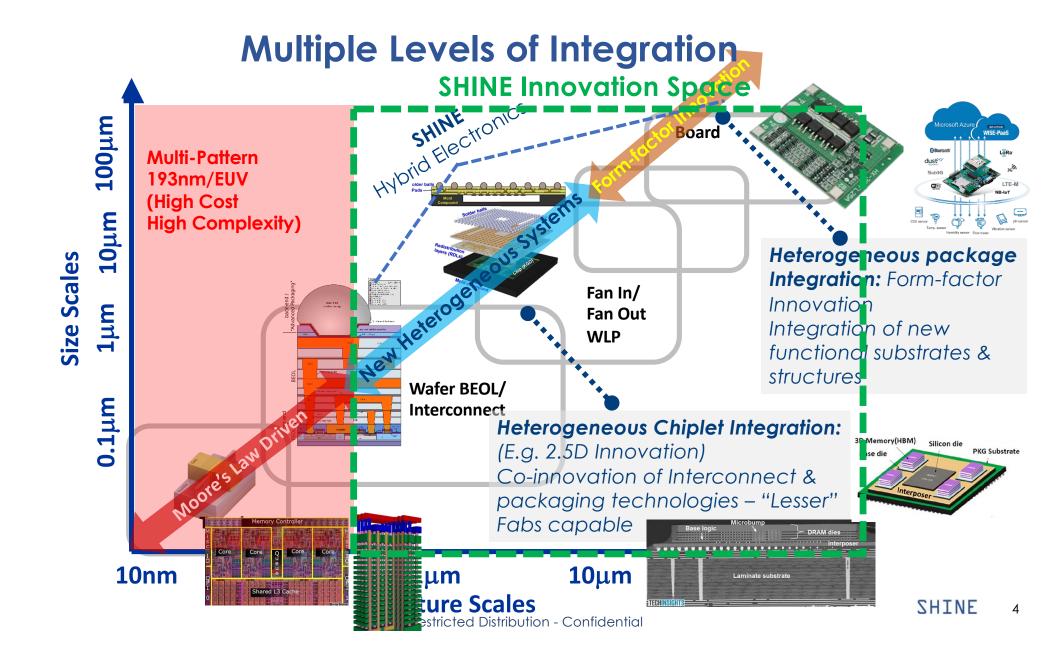

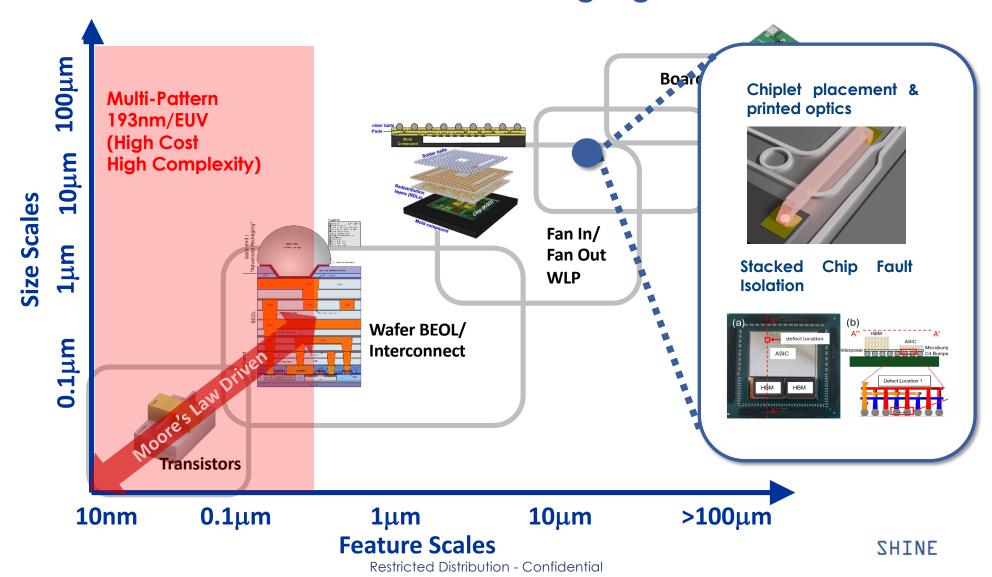

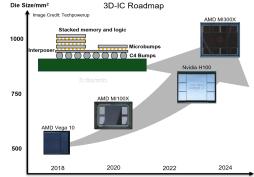

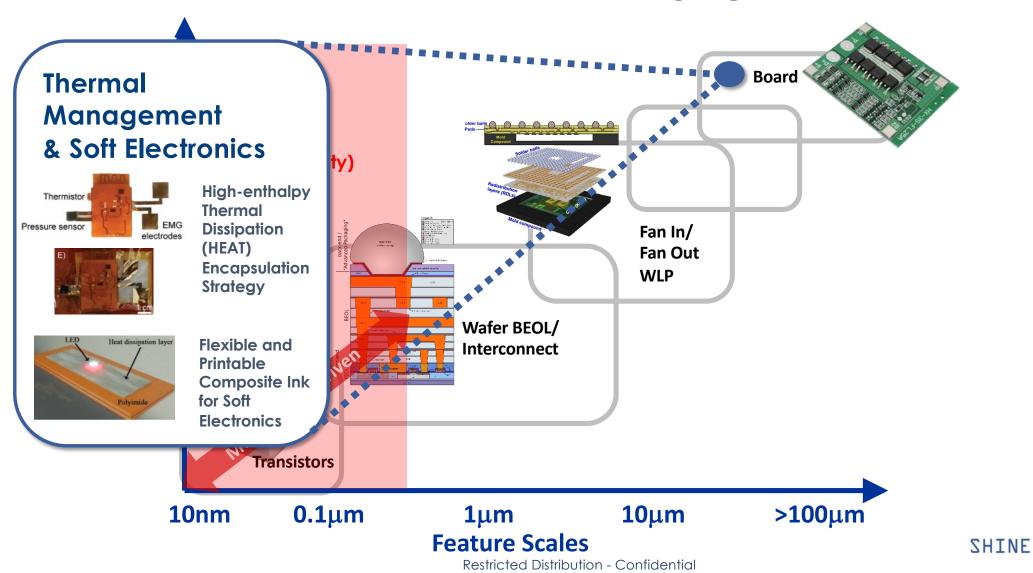

## **Multiple Levels of Integration**

## **Multiple Levels of Integration**

## SHINE Partnerships

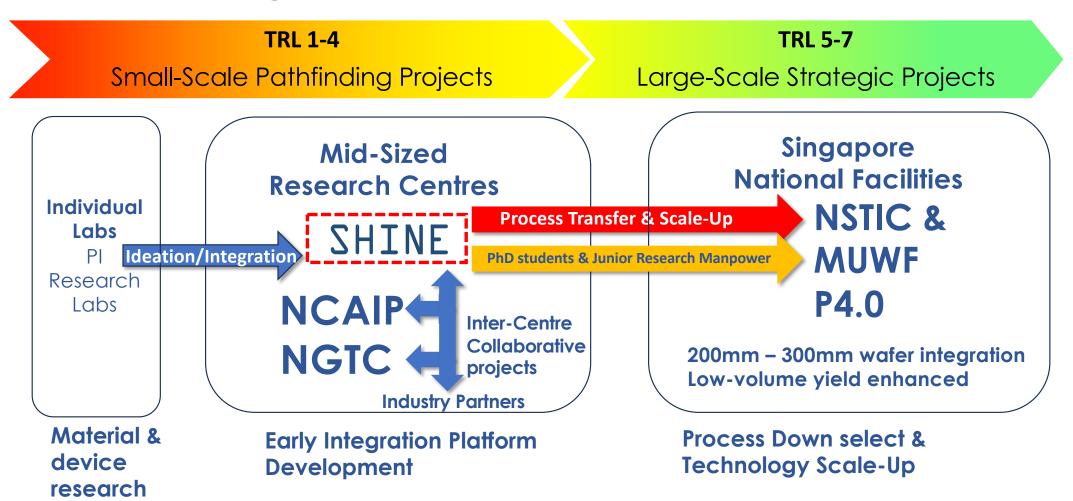

## SHINE's Alignment to National Semi R&D Pipeline

#### **Our Partners**

Material/Proce ss/Equipment Supply Chain

Design Services Supply chain

cādence

#### Technology Manufacturing Receptacle

Potential manufacturing partners

## Application Drivers/Recepta cles

#### National Beneficiari

es

- Aerospace Industry

- Heterogeneous Microelectronic s/ Packaging Industry

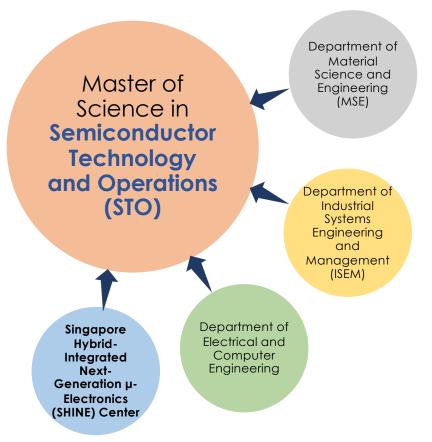

#### Bridging Academia with Industry for a Robust Talent Pipeline

Full-time Students: 1 year (min)/2 years (max)

Part-time Students: 2 years (min)/4 years (max)

100 Students

August AY2025 Intake

(YoY Growth of ~300%)

Department of Electrical & Computer Engineering College of Design and Engineering

Aug 2024

#### Industry Partners Interested in Providing Internships for SHINE Master Programme

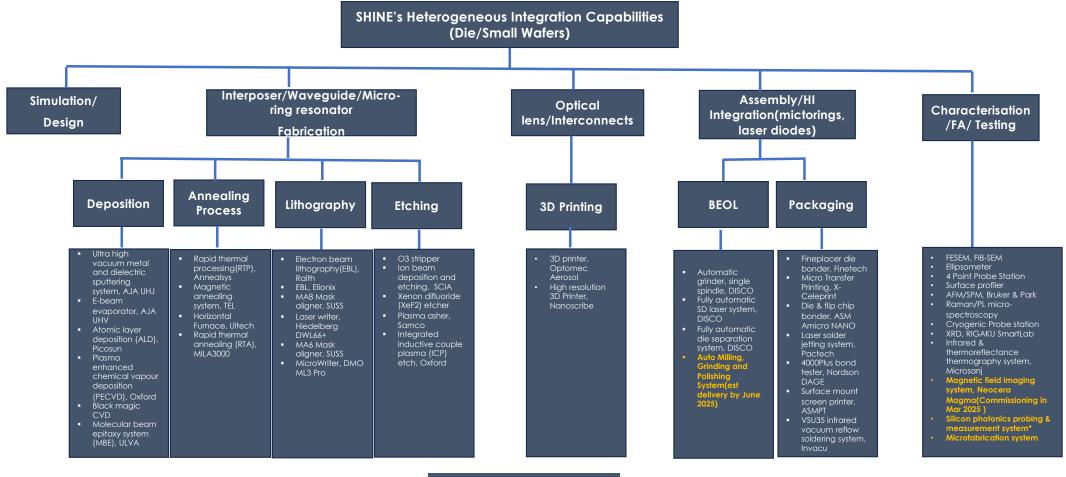

## Center Capabilities

#### SHINE's Shared Facilities & Infrastructures

## SHINE @ NTU: School of Materials Science & Engineering

- ~200 m² class 10k cleanroom

- Soft Composite Material Processing System

- Customized Flexible Circuit Board Fabrication System

- Integrated Packaging System

#### SHINE @ NUS: Expansion of E6NanoFab

- 150 m<sup>2</sup> Class 10k cleanroom: Device Level Pick-&-Place Integration, On-Chip Integration of Lenses, Back-end-of-line Processing and Packaging, Non-Destructive MFI Fault Isolation

- Dry Laboratory: Unique Thermal Effect Investigation Capability, Co-Package Photonics Measurement Capability

- Full 8" (200mm) Wafer Processing Capability

- Material and Device Characterization Labs

- Wide Range of Materials and Devices Processing Tools

- Clean Room Area: 1189 m<sup>2</sup>

- Dry Lab area: 1081 m<sup>2</sup>

- Wet Lab area: 477 m²

## SHINE's Process Capabilities

**New Capabilities in 2025**

#### Chiplet-to-Chiplet Photonics Communication and Computation

#### Si photonics interposer

#### Waveguides and MZI

- 1) PECVD deposition of Si3N4 layer on Si substrate

- 2) HSQ mask layer coating

- 3) Electron beam lithography for mask layer

- 4) ICP IRE Ar plasma etching

#### Interconnects

- 1) Ti/Al electron beam deposition

- 2) Photo litho

- 3) Dry etching

- 4) Rapid thermal annealing in N2

#### **BEOL** control circuit fabrication

- 1) Ti/Al electron beam deposition for bottom gate

- 2) Photo litho

- 3) Dry etching

- 4) ALD HfO2 gate dielectric layer

- 5) Annealing in Furnace

- 6) Photo litho

- 7) Dry etching

- 8) Sputtering of IGZO channel layer

- 9) XRD, AFM, Raman spectroscopy, EDX tests

- 10) Photo litho

- 11) Dry etching

- 12) ALD HfO2 gate dielectric layer

- 13) Photo litho

- 14) Dry etching

- 15) Ti/Al electron beam deposition for source and drain and interconnects

- 16) Photo litho

- 17) Dry etching

- 18) ALD HfZrO2 gate ferroelectric layer

- 19) Photo litho

- 20) Dry etching

- 21) Ti/Al electron beam deposition for top gate

- 22) Photo litho

- 23) Dry etching

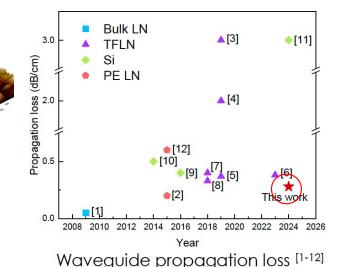

#### LiNbO3 photonics components

- 1) HSQ mask layer coating on LiNbO3 substrate

- 2) Electron beam lithography for mask layer

- 3) ICP IRE Ar plasma etching

#### Component integration on Si interposer

- 1) Laser bonding on SiC heat spreading die

- 2) SiC heat spreading bonding on Si interposer

- 3) Solder jetting on contact pads on Si interposer

- 4) Chiplets flip-chip bonding on Si interposer

- 5) Photo detector bonding on Si interposer

- 6) 2 photon polymerization of optical interconnects from chiplets, lasers, photo detectors to waveguides

- 7) Ring resonator micro transfer on Si interposer

#### Top electrode and interconnects

- 1) Ti/Al electron beam deposition

- 2) Photo lithography

- 3) Dry etching

- 4) Die shear, optical, thermal, and electrical tests

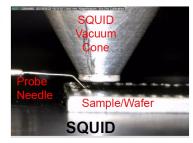

## Machine Learning Guided Failure Analysis & Diagnostic Capability Development for Next-Gen 3D-IC Packaging

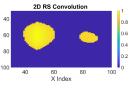

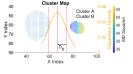

#### Machine Learning Guided FA & DCD for 3D-IC Packaging

- 1. Bz data as obtained from SQUID measurement

- Calculate fundamental period by 1D convolution of

Ramanujan Sum vector with MFI vector

- Generate magnetic cluster pair by 2D convolution of Ramanujan Sum circulant matrix with MFI

- 4. Calculation of Mahalanobis dispersion distance, DD, multiplied by pixel size gives Z height

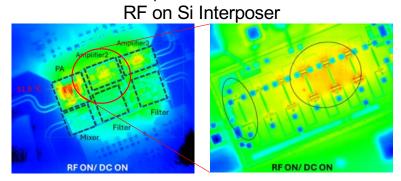

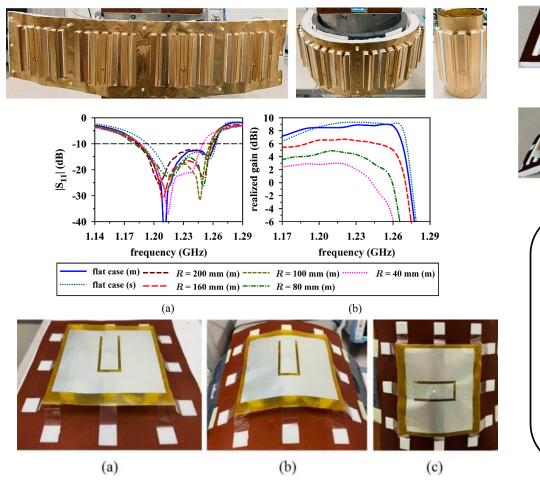

#### Hybrid Flexible RF System for the next generation communication

#### SiC interposer

#### CPW/interconnects

- 1) PECVD SiO2 dielectric layer

- 2) Ti/Al electron beam deposition

- 3) Photo litho

- 4) Dry etching

- 5) Rapid thermal annealing in N2

#### BEOL control circuit fabrication

- 1) Ti/Al electron beam deposition for bottom gate

- 2) Photo litho

- 3) Dry etching

- 4) ALD HfO2 gate dielectric layer

- 5) Annealing in Furnace

- 6) Photo litho

- 7) Dry etching

- 8) Sputtering of IGZO channel layer

- 9) XRD, AFM, Raman spectroscopy, EDX tests

- 10) Photo litho

- 11) Dry etching

- 12) ALD HfO2 gate dielectric layer

- 13) Photo litho

- 14) Dry etching

- 15) Ti/Al electron beam deposition for source and drain and interconnects

- 16) Photo litho

- 17) Dry etching

#### Interposer singulation

- 1) Back side grinding

- 2) Chemical mechanical polishing (CMP)

- 3) Stealth dicing

- 4) Die separation

#### Component assembly on interposer

- 1) Solder ball jetting

- 2) Flip chip bonding of RF power amplifier, phase shifter

- 3) Die shear, electrical, and thermal tests

- 4) Wire bonding and packaging

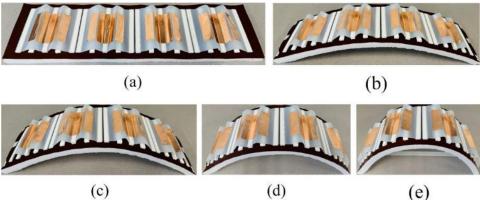

#### Component integration on flexible substrate

#### Integration of interposer

- 1) Plasma treatment

- Aerosol jet printing of flexible metallic interconnects

- 3) Infrared vacuum reflow sintering

- 4) Surface mount screen printing of contact pads

- 5) Surface mounting of SiC interposer

- 6) Infrared vacuum reflow soldering

#### Integration of strain sensors

- 1) Plasma treatment

- 2) Aerosol jet printing of adhesive layer

- 3) Sensor transfer on flexible substrate

- 4) Aerosol jet printing of flexible metallic interconnects

- 5) Curing in Oven

#### Integration of antenna array

- 1) Plasma treatment

- 2) Aerosol jet printing of adhesive layer

- 3) Sensor transfer on flexible substrate

- 4) Aerosol jet printing of flexible metallic interconnects

- 5) Curing in Oven

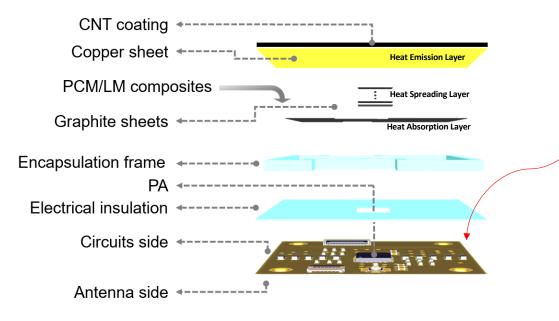

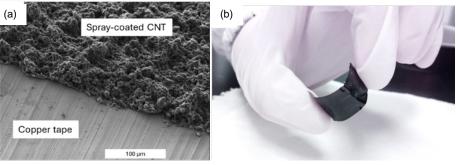

#### Thermal management structure integration

- 1) Plasma treatment

- 2) 3D printing of heat spreading polymer

- 3) Curing in Oven

- 4) 3D printing of polymer frame for PCM

- 5) Injection of PCM

- 6) Spray coating of carbon nanotubes layer on copper subtrate

- 7) Transfer of CNT layer

- 8) Thermal, RF, leakage, electrical tests

Special Additive Processing Capabilities

## Strategic Packaging Capability Development:

## **Advanced BEOL-Packaging Capabilities**

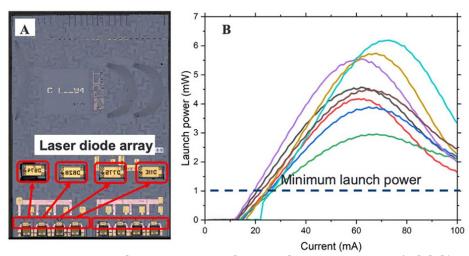

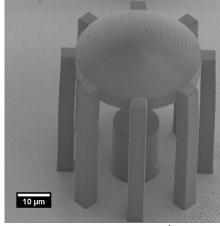

**AMICRA Nano Ultra-Precision Die** & Flip Chip Bonder

**Highest Placement Accuracy in Its Class**

Support ±0.3 µm @ 3 sigma placement accuracy

Cross-section of bonded die-substrate

Bonded laser bank of eight diodes & measured optical performance of the mounted diodes

2022 European Conference on Optical Communication (ECOC).

Restricted Distribution - Confidential

28/7/25

## Strategic Co-Packaged Optics Capability Development:

## **Micro Transfer Printing**

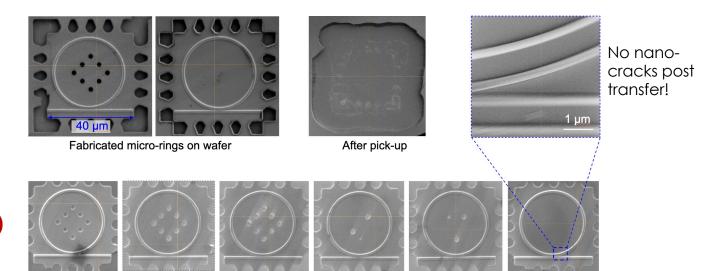

# **AMICRA Nano Micro Transfer Printing**

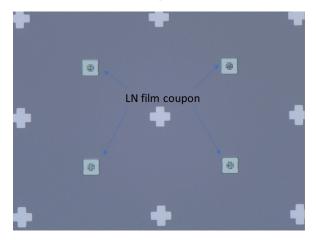

Micro-Transfer Printing of Lithium Niobate (LN) on Silicon Photonic Integrated Circuits (PICs)

- Tight integration of large arrays of compound semiconductors (e.g., GaN, GaAs, SiC, SiGe, InP) with CMOS semiconductors and passive components (inductors and capacitors)

- Lower I/O density and higher current density interconnects.

- Ultra-thin, small footprint three-dimensional integrated circuits (3D ICs) versus a large footprint system-in-package (SiP).

Unpublished and confidential results.

## Pick-&-Place Integration Scaling

**AMICRA NANO Die Bonder & Flip** 500 µm **Chip Bonder** 1cm Placement accuracy  $\pm 0.3 \, \mu m$  @ 3 sigma Component Size & Thickness and bonding of semiconductor Chips & components **Chiplets** Operational @ 100 µm **5mm E6NanoFab** (2023) Sub-Die Microcontact printing Layers MSB 50 nm Sub-Die Components  $0.1 \mu m$ Lithography iTexel (At the Fragility Limit of Transfer) Limited Fragility Limited  $0.1 \mu m$  $0.3 \mu m$ 1µm  $0.5\mu m$

**Alignment Accuracy**

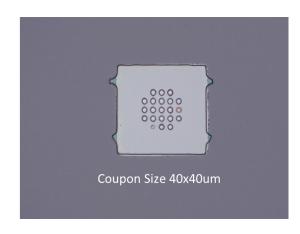

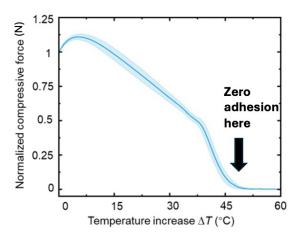

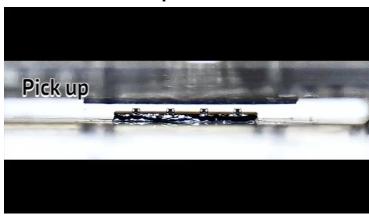

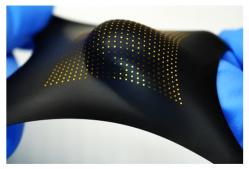

#### Next-Generation Micro-Contact Printing (in Research) iTEXEL

Breakthrough Dry Mass Transfer Printing Technology (By Assoc. Prof. Benjamin Tee)

#### **Key Features**

- Ability to Pick&Place Sub-100nm thick components!

- Real-time Programmable Photonics driven actuators

- Precise Sub-100 micron resolution of pickup and placement

- Consistency Multi-use, zero-adhesion capable transfers for micro/nano thin films

Low thermal budget (< 50C)

Transfer process video

**Transfer SMD components**

**Transfer onto Elastic substrate**

#### iTEXEL: Next-Generation Micro-Contact Printing (in Development)

Demonstrated successful transfers of Fragile Thin-Film (300nm-600nm thick) lithium niobate photonic components (patterned)!

No Shearing Needed for Microtransfers

High-speed Photonic Driven Actuations

Scalable to 300mm (Goal)

Transfer < 100nm thick films (Goal)

Released micro-rings on silicon substrate

## Strategic Co-Packaged Optics Capability Development:

## Metallic Interconnect Printing for 2D & 3D Substrates

Optomex Aerosol

Jet 3D Printing

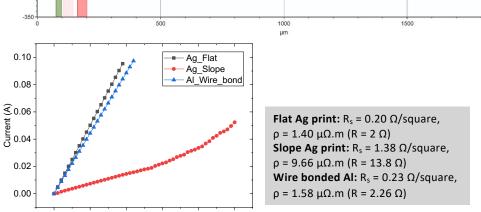

\*parasitic limit practised by industry is 5 Ω/square

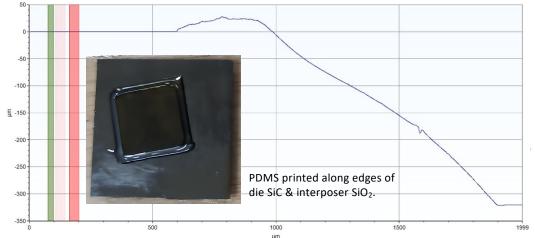

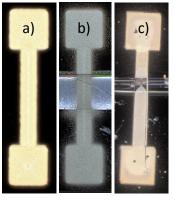

Printed Ag on a) flat SiO<sub>2</sub> (hotplate sintered), b) PDMS slope (furnace sintered), c) Al wire bonded

Demonstrated metallic interconnects along the edges of die SiC and interposer SiO<sub>2</sub> with a resistance of 1.38 Ω/square, which meets industry standards for parasitic limits

Unpublished and confidential results.

Restricted Distribution - Confidential

V (v)

## Strategic Co-Packaged Optics Capability Development:

On-Chip Hybrid Integration of Photonics using Lenses and PWB

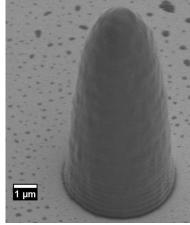

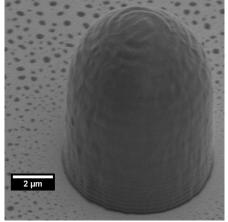

3D Two-photon Lithography Printer -**NANOSCRIBE GT2** (E6NanoFAB & Tee's Research Group)

3 µm

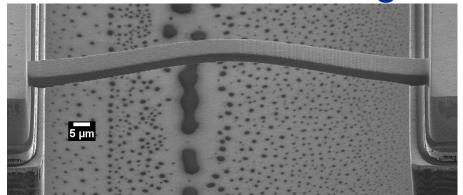

Chip-chip: Bridged PWB, 112x7x3.5 (µm)

Lens at waveguide facet, dia 12µm

- Finest XY resolution 400 nm

- Finest vertical resolution 1µm

Parabolic High NA Lens (dia  $5\mu m$  and h=  $10\mu m$ )

Hemispherical lens (dia  $7\mu m$ , h=  $12\mu m$ )

Beam Expander  $(dia=40\mu m, h=60\mu m)$

## Low-Temperature Soldering Capability – Laser Integration

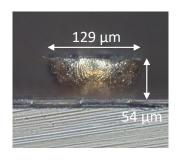

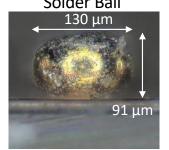

## Advanced Laser Solder Jet Packaging Capabilities

- Support ±0.3 μm @ 3 sigma placement accuracy

- High solder alloy flexibility: Eutectic SnPb, high-lead SnBb, lead-free SnAg, SnAgCu, etc.

- Up to 10 balls/sec

Commercial Solder Ball

Replacement Laser-jetted Solder Ball

| shear strength | Commercial (g) | Laser-jetted (g)      |  |

|----------------|----------------|-----------------------|--|

| Min            | 33.40          | 34.60                 |  |

| Max            | 43.86          | 48.74<br>43.25 ± 4.71 |  |

| Mean           | 39.23 ± 3.59   |                       |  |

| Median         | 40.59          | 43.10                 |  |

| Range          | 10.47          | 14.14                 |  |

Extrapolation from AEC-Q100-010A standard:

If diameter = 90  $\mu$ m  $\rightarrow$  shear strength = 20 g

Special Test Capabilities

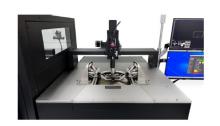

# Strategic Co-Packaged Optics Capability Development: Silicon Photonics Measurement and Probe System

Integrates the functionalities and advantages of both measurement and probe systems into a single,

efficient platform

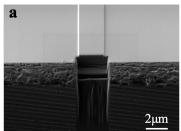

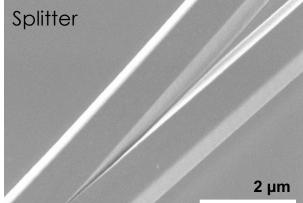

SEM images of critical areas of micro ring resonator (MRR)

- Perfect for analyzing intricate photonic components like modulators, waveguides, and multiplexers.

- The futureC SIPH software ensures a user-friendly experience with its integrated control panel that manages both measurement and probing functionalities.

## Strategic Metrology Capability Development:

## **Unique Thermal Effect Investigation Capability**

Enable full spectrum thermal imaging and the study of heat conduction path.

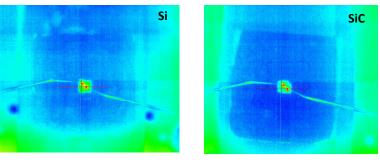

# Infrared & Thermoreflectance Thermography

Nanosecond Transient Thermal Imager for topside thermal imaging is a lock-in thermoreflectance-based (TR) system optimized in the visible band with diffraction-limited spatial resolution.

Thermal failure analysis of through-silicon interposer for GaN and GaAs chips.

In-situ heat spreading analysis of Si and SiC substrate

Unpublished and confidential results.

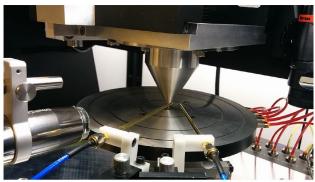

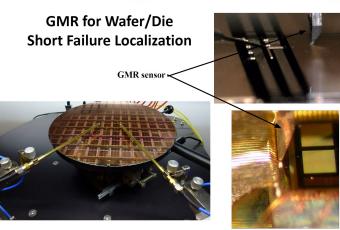

#### Non-Destructive Stacked-Chip Fault Isolation Capability (In development)

#### **Magnetic Field Imaging**

Fault Isolation Solution using a single tool for all static electrical failures, opens, shorts, leakages

## SQUID for Packaged/assembled devices Short Failure Localization

Research Activities/ Project Highlights

#### **SHINE Research Activities**

|                            |                                                                 |                   |                                          |                                           |                                                    |                                                                   | ,                                                           |

|----------------------------|-----------------------------------------------------------------|-------------------|------------------------------------------|-------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|

| Low-Power                  |                                                                 |                   |                                          | Capacitance<br>Sensing Circuit            |                                                    | Low-Power Chiplet                                                 |                                                             |

| Chiplet Platform           | One-Wire Inter-Chiplet Signaling  Over-the-chip HI of Harvester |                   | Self-powered<br>System-on-Wire           | Battery-less<br>Walking Step<br>Counter   | Power Modulation                                   |                                                                   |                                                             |

| Flexible                   | Resistive Strain<br>Sensor                                      |                   | Wheatstone Bridge<br>Sensing Circuit     | Capacitive Bending<br>Sensor              | Topological Adhesion Conductor-Substrate           |                                                                   |                                                             |

| Hybrid<br>Electronics      | Flexible Capacitive Sensor                                      |                   | Ultrathin<br>Stretchable<br>Conductors   | Low-hysteresis<br>Tactile Sensor          | Universal Nano-<br>Anchor for LM                   | Morphology-Adaptive Conductor                                     | Silk Fibroin Film With Engineered Rigid-island<br>Structure |

| Novel and                  | l and                                                           |                   | CNT Transistor                           | 3D-1T1R                                   | 2D Materials                                       |                                                                   |                                                             |

| Nano-Materials Integration | SiC-Si Dire                                                     | ect Bonding       | SiC-Si Low-T<br>Bonding                  | Hybrid MonoC-<br>PolyC SiC Interposer     | BEOL FeFET                                         | FeFET                                                             | In-Memory Computing                                         |

| Thermal                    |                                                                 | Radiative Cooling | Integration of<br>Heat Spreader /<br>PCM | Thermal Mapping with TRIR                 | Integration of Heat<br>Pipe                        | Interposer- and package-level active + passive thermal management | On-chip thermal characterization / modelling                |

|                            | TIM Ink Formation Stretchab                                     |                   |                                          | Board-level TM<br>Antenna System          | 3D-printable TM Ink                                | 3D-printable thermoelectric ink                                   | Integrated laser diode thermal management                   |

| mmWave                     |                                                                 |                   | Tx / Rx<br>Architecture<br>Design        | L-band 4x4 Dipole<br>Array                |                                                    | Highly flexible active phase arrays                               | Smart sensing surface                                       |

| and RF                     | Flexible Patch Antenna with Springs /<br>Spacers                |                   | Flexible Phased<br>Array Antenna         | L-band 8x1 Patch<br>Array                 | X-band Phased<br>Arrays                            | Active reconfigurable intelligent surface                         |                                                             |

| Packaging                  |                                                                 | Stealth Dicing    | Through-SiC-<br>Interposer               | Rework of UBM                             |                                                    | EIC + PIC Packaging                                               | Optical Interconnect On Flexible Substrate                  |

| r dendging                 |                                                                 | D2D PnP           | Solder Ball Jet                          | Micro-Transfer-<br>Printing               | SiC Interposer<br>Fabrication                      | Flexible FOWLP platform                                           |                                                             |

| Advanced                   | LN Process  LNOI Modulator                                      |                   | Freeform PWB                             | Silicon Photonics<br>Testing Capabilities | LNOI Integration                                   |                                                                   |                                                             |

| Photonic Device            |                                                                 |                   | Freeform Lens                            | Surface-to-Edge<br>Coupler Printing       | Modelling and design of vertical adiabatic coupler |                                                                   |                                                             |

|                            |                                                                 |                   |                                          |                                           |                                                    |                                                                   | ,                                                           |

2021 > 2022 > 2023 > 2024 > 2025

2026 and Beyond

College of Design SHINE and Engineering Cap

SHINE 2.0 Key Focus

SHINE 30

### SHINE's 2024 Research Highlights

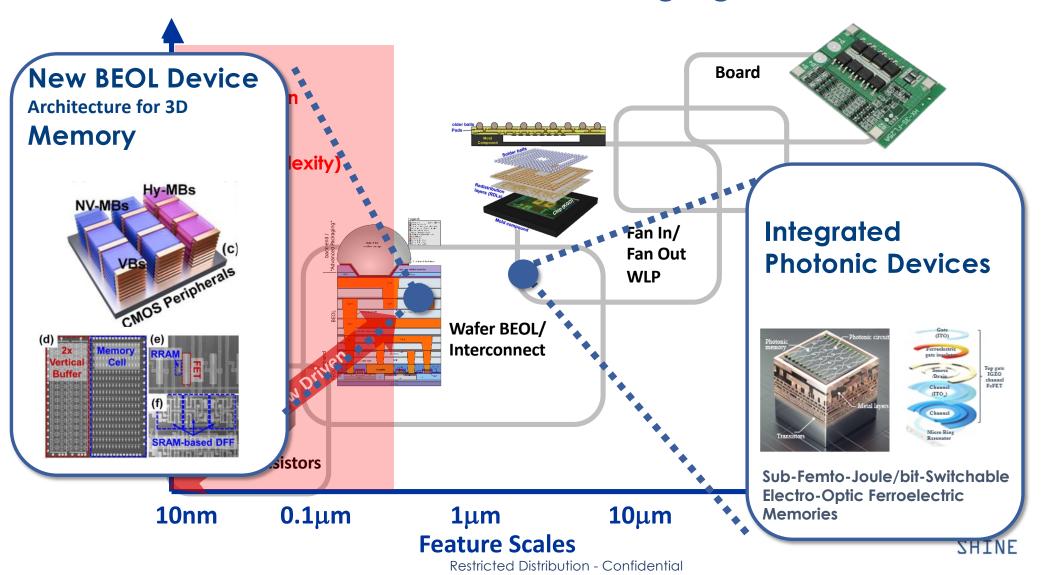

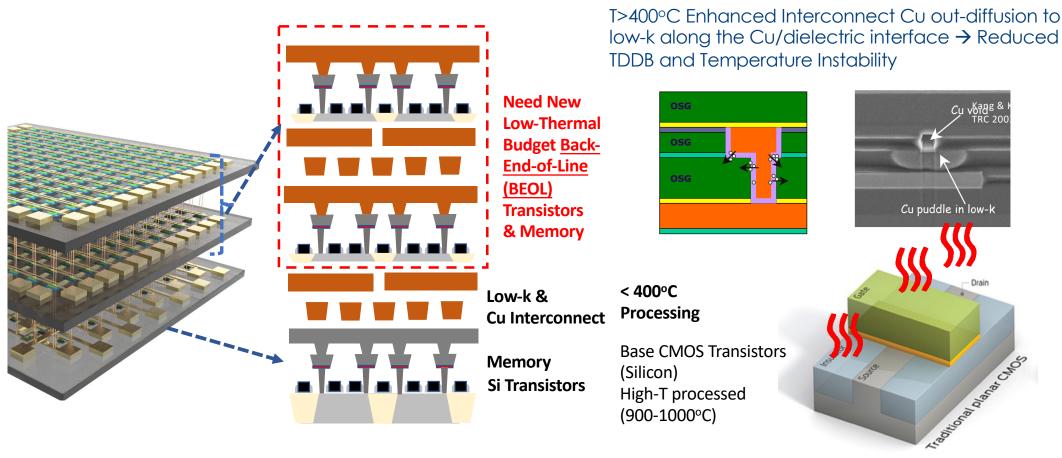

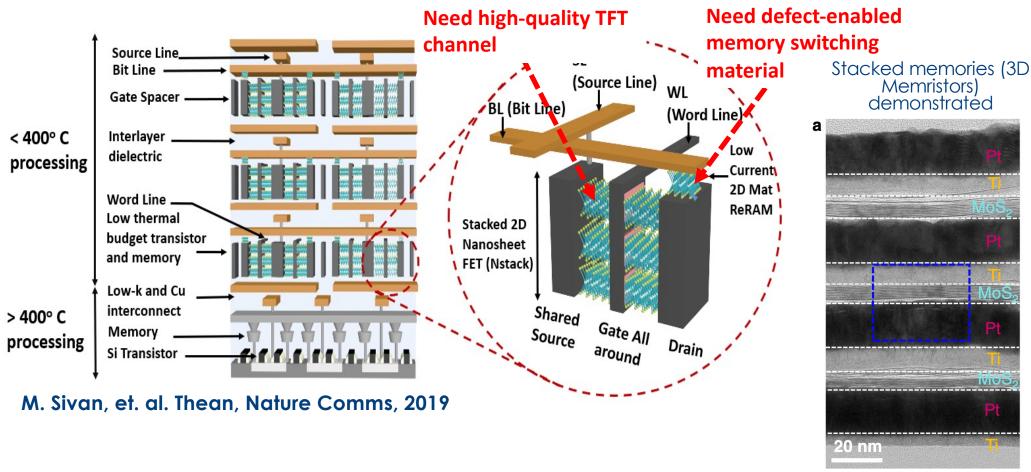

## M3D-IC: BEOL Transistor-Interconnect Thermal Budget Dilemma

A. Thean et al., "Low-Thermal-Budget BEOL-Compatible Beyond-Silicon Transistor Technologies for Future Monolithic-3D Compute and Memory Applications," 2022 International Electron Devices Meeting (IEDM), pp. 12.2.1-12.2.4, doi: 10.1109/IEDM45625.2022.10019511.

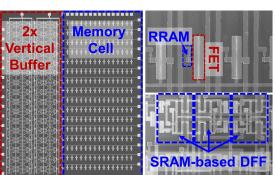

### Monolithically-stacked 3D 1T1R ACiM for 100TOPS/W

**NV-MBs and VBs**

Accomplishments in this project:

Achieved wafer-scale, low-temperature (<400 °C) monolithic 3D integration of chief</li>

and 2D materials with strong device performance.

- Developed low-voltage, CMOS-compatible 1T1R memory cells with IGZO FETs and MoS2 RRAMs, requiring <100 µA and <1 V for switching.

- Proposed a 2TOC1R DRAM-RRAM hybrid with dual-gated IGZO FETs to improve RRAM endurance.

- Designed an all-IGZO buffer enabling 3D data pipelining for efficient multi-stack operations.

- Demonstrated 3D analog compute-in-memory with 121 TOPS/W efficiency and 4.73 TOPS throughput, reducing ADC energy overhead.

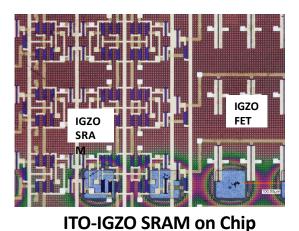

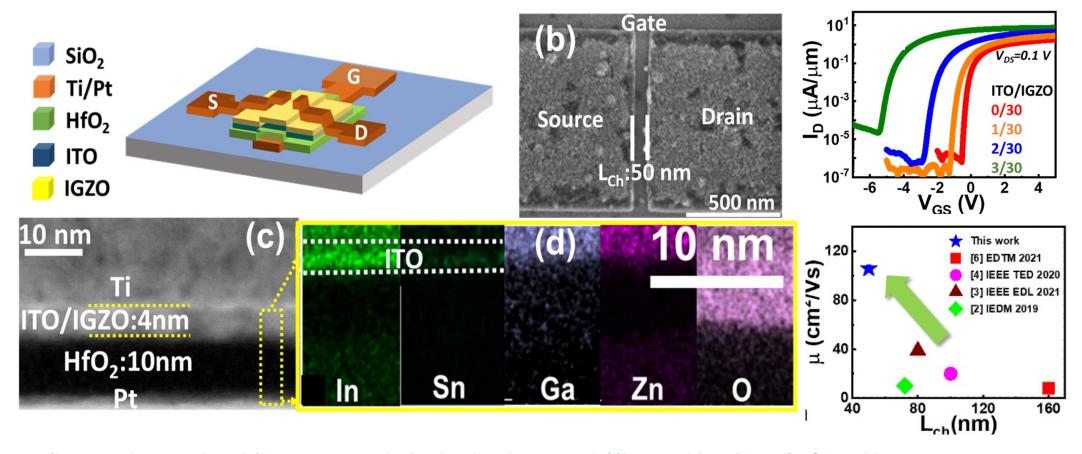

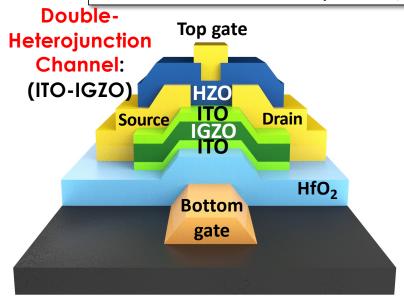

### Bilayer Heterojunction Oxide Channel (ITO-IGZO) Enhancement

Bilayer channel achieves record IGZO electron mobility and hysteresis-free SS performance,  $I_{DS}$  = 800  $\mu$ A/ $\mu$ m (1.0V  $V_{DS}$ ) with  $\mu$  = 106 cm²/V-s

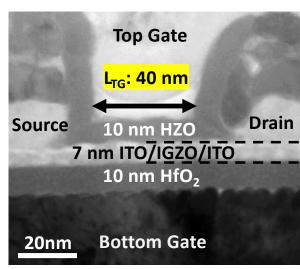

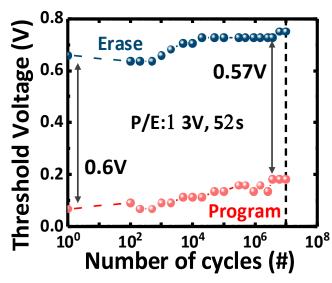

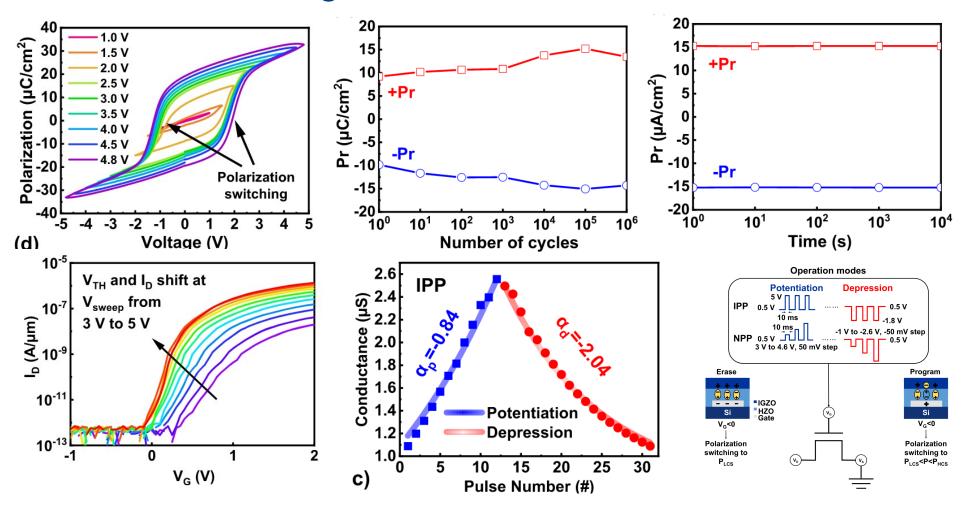

#### **Double-Gated** Ferroelectric IGZO Memtransistor

First Demonstration of Ultra-low D<sub>it</sub> Top-Gated Ferroelectric Oxide-Semiconductor Memtransistor with Record Performance by Channel Defect Self-Compensation Effect for BEOL-Compatible Non-Volatile Logic Switch

Chun-Kuei Chen<sup>†</sup>, Zihang Fang<sup>†</sup>, Sonu Hooda<sup>†</sup>, Manohar Lal, Umesh Chand, Zefeng Xu, Jieming Pan, Shih-Hao Tsai, Evgeny Zamburg, and Aaron Voon-Yew Thean\*

Department of Electrical and Computer Engineering, National University of Singapore (NUS), Singapore 117583 †Equal contribution; Email: <u>Aaron.Thean@nus.edu.sg</u>

2022 International Electron Devices Meeting (IEDM), 6.1. 1-6.1. 4

2022 San

**Francisco**

- Overcome a fundamental issue of top-gated interface Dit by heterojunction engineering

- Enables new multi-gated devices with new system application possibilities

#### Low-Thermal Budget Ferroelectric HZO-IGZO Memtransistor

Stress-Memorized HZO for High-Performance Ferroelectric Field-Effect Memtransistor SH Tsai, Z Fang, X Wang, U Chand, CK Chen, S Hooda, M Sivan, J Pan, ... ACS Applied Electronic Materials 4 (4), 1642-1650 (2022)

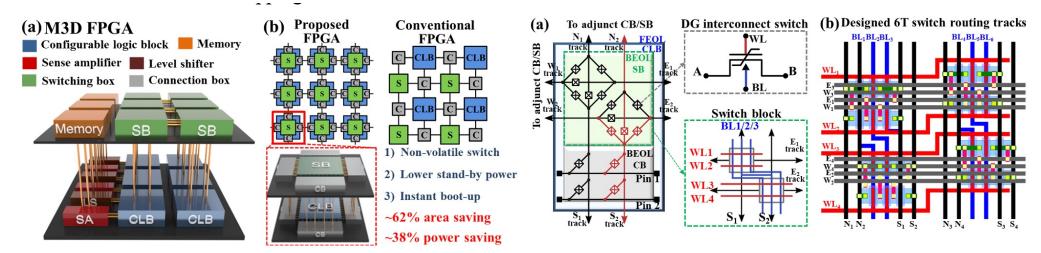

## Dynamic Reconfigurable Interconnect by M3D Nonvolatile Switch

First Demonstration of Ultra-low D<sub>it</sub> Top-Gated Ferroelectric Oxide-Semiconductor Memtransistor with Record Performance by Channel Defect Self-Compensation Effect for BEOL-Compatible Non-Volatile Logic Switch

Chun-Kuei Chen<sup>†</sup>, Zihang Fang<sup>†</sup>, Sonu Hooda<sup>†</sup>, Manohar Lal, Umesh Chand, Zefeng Xu, Jieming Pan, Shih-Hao Tsai, Evgeny Zamburg, and Aaron Voon-Yew Thean\*

Department of Electrical and Computer Engineering, National University of Singapore (NUS), Singapore 117583 †Equal contribution; Email: <u>Aaron.Thean@nus.edu.sg</u>

2022 International Electron Devices Meeting (IEDM), 6.1. 1-6.1.4

Dynamically-Reconfigurable Interconnect with M3D-compatible Double-Gated FeFET

CK Chen, S Hooda, Z Fang, M Lal, Z Xu, J Pan, SH Tsai, E Zamburg, ...IEEE Transactions on Electron Devices 70 (4), 2098-2105

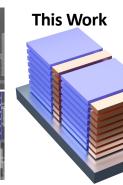

# Vision of 2-D Material Monolithic 3D Memory Systems

B. Tang, et. al. Thean, ...

Nature Communications 13 (1), 1-9, 2022

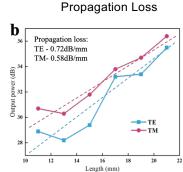

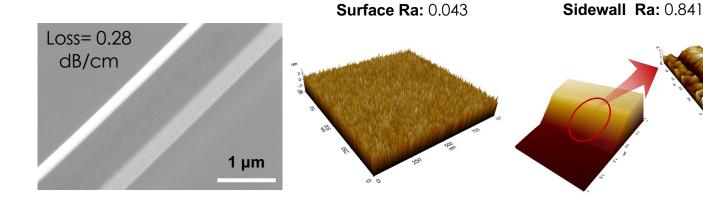

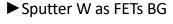

# Ultra-Low Loss (Record) Lithium Niobate Photonic Waveguides & Modulators Photonics

(CLEO 2025)

Developed New Dry etch technique to achieve Lithium Niobate sidewall roughness about 1 nm for record ultralow propagation loss (0.28 dB/cm)

Unpublished and confidential results.

# Low-voltage Hybrid Ferroelectric Photonic Memories

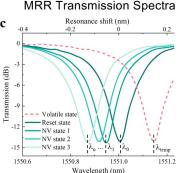

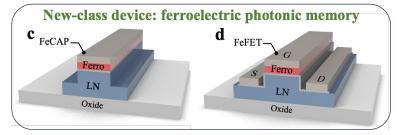

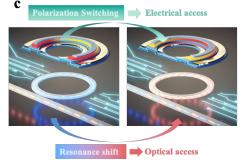

Femto-Joule/bit-Switchable Electro-Optic Ferroelectric Multi-State Photonic Memories

Zefena Xu, Chun-Kuei Chen, Hona-Lin Lin, Maheswari Sivan, Evgeny Zamburg, James Yong-Meng Lee, Suresh Venkatesan, Aaron Danner, Aaron Voon-Yew Thean

#### **Under Review Nature Photonics**

Ferroelectric gate insulator

- Offers a 100× reduction in switching energy

- Achieve switchable and non-volatile multiple optical memory states (5 states minimum) with ultra-low energy cost of 0.6 fJ/bit, while achieving robust 10-year data retention and read-write endurance exceeding 10<sup>7</sup> cycles

### **New Hybrid Integrated Optoelectronics Capabilities**

#### IEEE International Electron Devices Meeting (IEDM) 2023

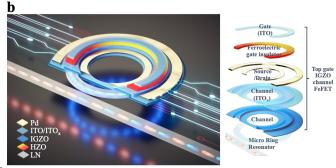

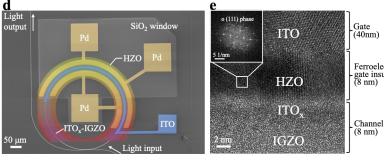

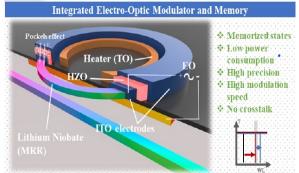

First Demonstration of HZO-LNOI Integrated Ferroelectric Electro-Optic Modulator and Memory to Enable Reconfigurable Photonic Systems

Zefeng Xu<sup>1,2,6†,</sup> Chun-Kuei Chen<sup>1,6†</sup>, Hong-Lin Lin<sup>1†</sup>, Yuan Gao<sup>1</sup>, Wei Ke<sup>3</sup>, Baochang Xu<sup>1,6</sup>, Pavel Dmitriev<sup>4</sup>, Arbiz Carlan<sup>5</sup>, Evgeny Zamburg<sup>1,6</sup>, Steven Touzard<sup>4</sup>, Xinlun Cai<sup>3</sup>, James Lee<sup>5</sup>, Suresh Venkatesan<sup>5</sup>, Aaron Danner<sup>1</sup>, Aaron Voon-Yew Thean<sup>1,2,6†</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, National University of Singapore (NUS), <sup>2</sup>Integrative Sciences and Engineering Program, NUS Graduate School, <sup>3</sup>School of Electronics and Information Technology, Singapore 117583, Sun Yat-Sen University, China 510275, <sup>4</sup>Centre for Quantum Technologies, NUS, <sup>5</sup>POET Technologies, <sup>6</sup>Singapore Next-Generation Hybrid μ-Electronics Center (SHINE), Singapore 117583. <sup>†</sup>Equal contribution.

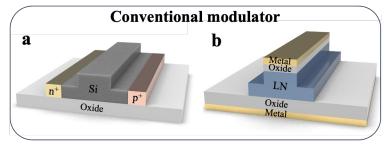

Traditional Modulators

Non-volatile Memory

HZO

Lithium Niobate

(MRR)

\* High power consumption

\* No memorized state

\* High speed modulation

\* Low modulation precision

Benchmark of LNOI EOMM against state-of-the-art non-volatile photonic memory.

| Ref.         | Waveguide<br>material          | Method                                        | Q-factor | Extinction<br>ratio | Efficiency | Multi-<br>Level | Retention | Endurance  | No-crosstalk<br>modulation |     | BEOL<br>compatibility | Thermal stability |

|--------------|--------------------------------|-----------------------------------------------|----------|---------------------|------------|-----------------|-----------|------------|----------------------------|-----|-----------------------|-------------------|

| [11]         | Si <sub>3</sub> N <sub>4</sub> | GST: absorption                               | 104      | 1.55 dB             | N/A        | Yes             | N/A       | N/A        | No                         | No  | No                    | Low               |

| [12]         | Si                             | Poly-Si: floating<br>gate                     | 104      | 12.7 dB             | 15 pm/V    | Yes             | N/A       | N/A        | No                         | No  | Yes                   | Low               |

| [13]         | Si                             | Sb <sub>2</sub> Se <sub>3</sub> : phase shift | $10^{3}$ | 7 dB                | N/A        | No              | N/A       | N/A        | No                         | No  | No                    | Low               |

| [14]         | Si                             | ITO: floating gate                            | N/A      | 10 dB               | N/A        | No              | N/A       | N/A        | No                         | No  | Yes                   | Low               |

| [7]          | SOI                            | HAO: charge<br>trapping                       | 103      | 8.9 dB              | 34 pm/V    | No              | 10 years  | 108 cycles | No                         | No  | No                    | Low               |

| [8]          | Si                             | BTO: phase shift                              | 105      | 12 dB               | 8 pm/V     | Yes             | 10 years  | 107 cycles | No                         | No  | No                    | High              |

| [9]          | $Si_3N_4$                      | HZO: absorption                               | N/A      | 9.4 dB              | N/A        | Yes             | N/A       | N/A        | No                         | No  | No                    | Hight             |

| This<br>work | LNOI                           | HZO: Pockels<br>effect                        | 105      | 13.3 dB             | 66 pm/V    | Yes             | 10 years  | 10º cycles | Yes                        | Yes | Yes                   | High              |

Schematics and comparison of traditional thermo-optical (TO)/electro-optic (EO) modulator, LNOI non-volatile memory, and LNOI Integrated EOMM.

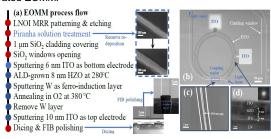

(a) The key process steps of fabricating LONI EOMM. The SEM images of (b) LNOI EOMM, (c) micro-ring resonator (MRR) coupling region, (d) ferroelectric Hafnium Zirconate (HZO) memory capacitor integrated on MRR.

#### Highlights of this work

- ☐ Record-high photonic memory efficiency of 66 pm/V

- ☐ High extinction ratio of 13.3 dB and full width at half maximum of 0.10 nm

- ☐ At least stable 9 memorized states @ driving voltage 2-4 V

- ☐ Record-high endurance >10<sup>9</sup> cycles; retention >10 years

- First Lithium Niobate on Insulator (LNOI) electro-optic memory based on 2<sup>nd</sup> order nonlinear effect, Pockels effect

- ☐ First electro-optic modulator and memory all-in-one solution

- Low thermal budget process <400°C</p>

- ☐ Integration of electro-optic modulator and memory (EOMM) with POET 400G Tx/Rx engines

- Simulated chiplet-interposer photonic interconnect system with low power consumption demonstrated

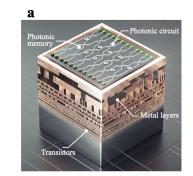

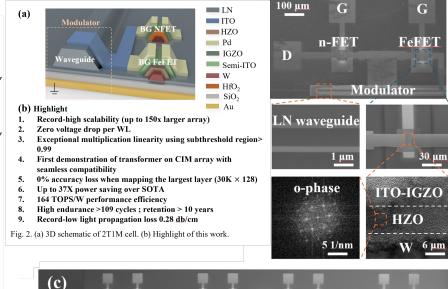

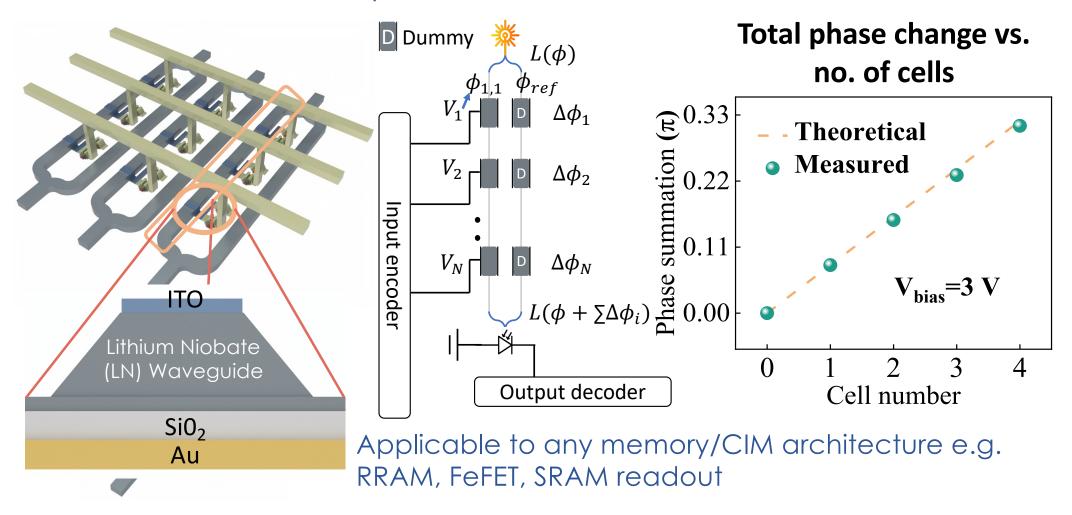

Lithium-Niobate-IGZO Based Photonic-Electronic Integrated Compute-In Memory Systems (Fine-Pitch LN-Electronics Integration) VLSI 2025

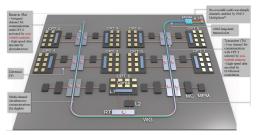

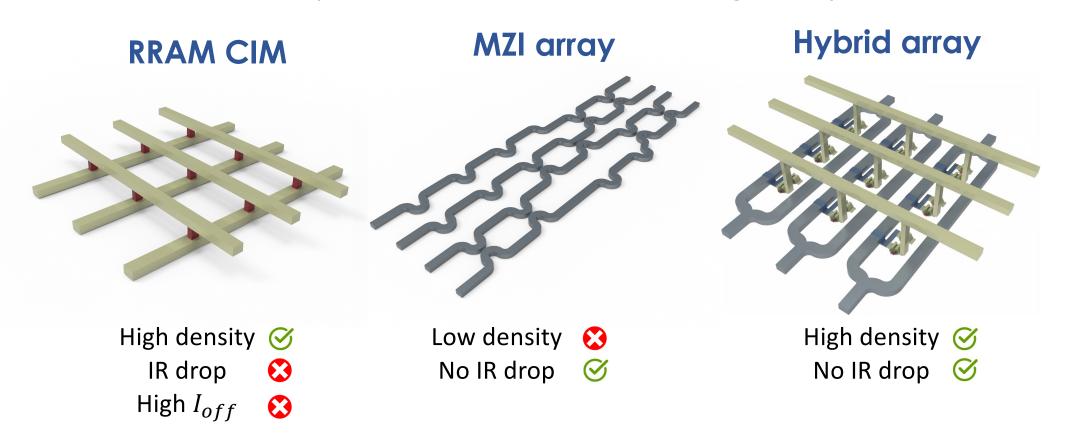

### Lithium-Niobate-IGZO Based Photonic-Electronic Integrated Compute-In Memory Systems VLSI 2025

#### Problem Statement:

• The scalability is often hindered by escalating IR losses caused by the increasing wire resistance in larger arrays and advanced nodes.

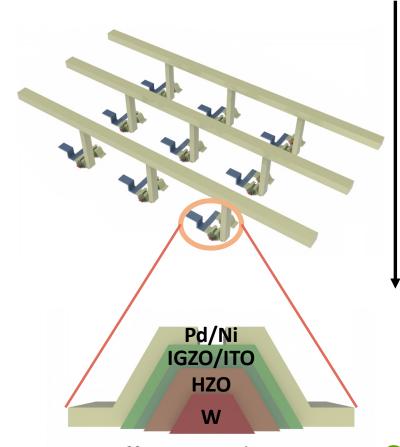

#### Innovation:

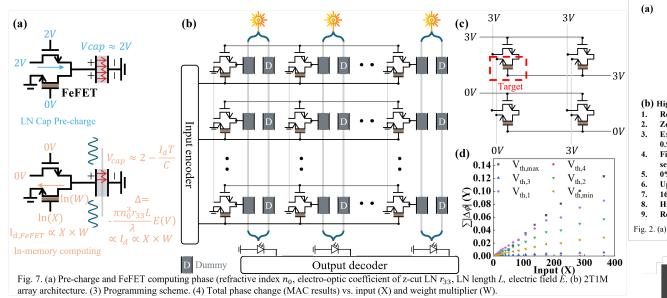

• A novel two-transistor-one-modulator photonic-electronic hybrid architecture using an NFET for initialization, a FeFET operating at sub-threshold region for in-memory multiplication with enhanced linearity and ultra-low-loss lithium niobate on insulator photonic modulator for phase-domain summation.

Cell #2

Cell #1

Cell #3

Cell #4

### FeFET-based in-memory computing

Lower off-current than RRAM

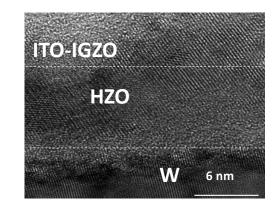

- ► ALD-grown 8 nm HZO at 280°C

- ► HZO etching using diluted HF

- ► ALD-grown 10 nm HfO<sub>2</sub> at 250°C

- ► HfO<sub>2</sub> etching using diluted HF

- ► Sputtering 2 nm ITO / 5 nm IGZO as FETs channel

- ► Channel etching using diluted HCl

- ► E-beam growing Ti / Pd as FETs S/D electrodes

- ► Annealing in O<sub>2</sub> at 380 °C

Linear multiplication in subthreshold region

47

# Photonic "lossless" in-phase summation

28/7/25

### SHINE's 2024 Research Highlights

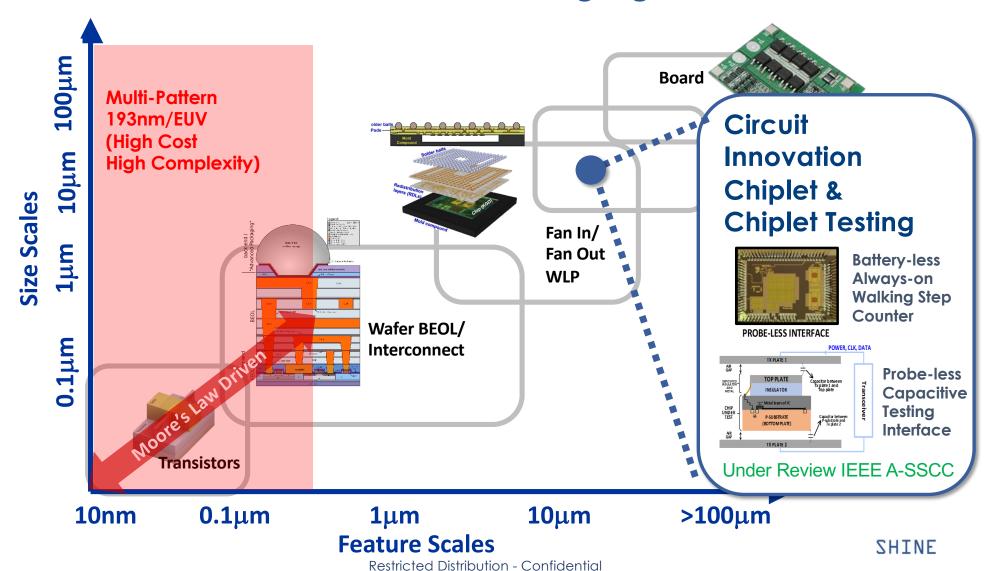

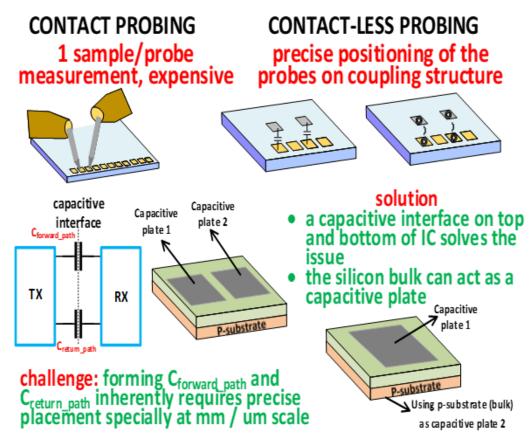

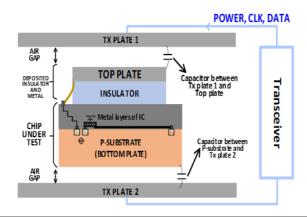

### Probe-less Capacitive Testing Interface. (Prof. Massimo Alioto)

Submitted to IEEE A-SSCC

#### PROBE-LESS INTERFACE

#### **Highlight of This Work**

- □ Successfully tested probe less/touch-less massive chiplet testing setup with placement invariant capacitive coupling interface

- ☐ No packaging or probing needed (Cost Reduction)

- ☐ Probe-less testing at speed including power consumption demonstrated

- Multi die testing with uniques chip ID and random backoff transmission (Clock recovery, forward, and backward data communication with BER<10-7 demonstrated experimentally.

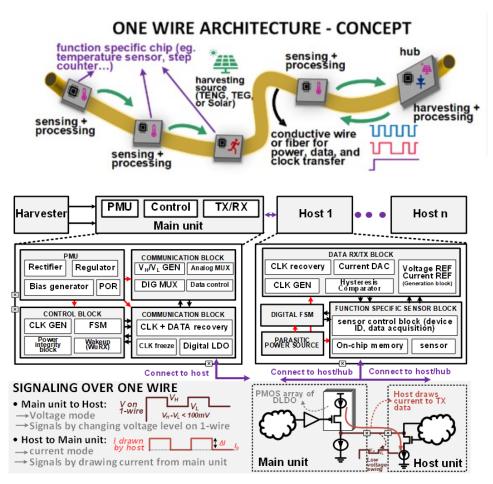

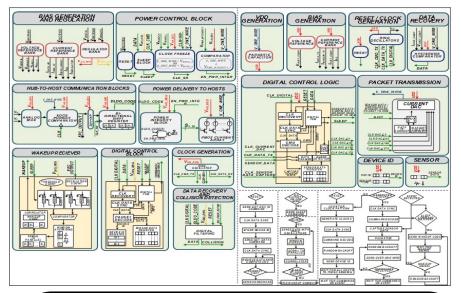

### Thrust 1: Self-Powered System-on-wire (On-going Work, Prof. Massimo Alioto)

#### **Highlight of This Work**

- ☐ Fully autonomous, self-powered system on a single wire.

- ☐ This system can be distributed along a conformable fiber and is capable of simultaneously harvesting energy, transferring power, transmitting data, and synchronizing clocks over this single wire within a distributed network.

- ☐ Introduces an architecture for a chiplet-based system where functional units (hosts) with sensing capabilities connect to a central chiplet (hub) using a single-wire protocol.

- This approach simplifies the design of a low-power, low-bandwidth multi-modal system by combining power delivery and communication on the same wire.

## SHINE's 2024 Research Highlights

### **New Hybrid Integrated Optoelectronics Capabilities**

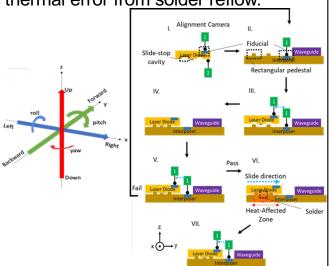

#### Problem statement

Passive alignment is cost effective for laser diode alignment, however, coupling loss with respect to misalignment must be taken care of.

#### **Journal of Lightwave Technology**

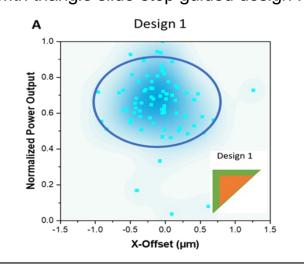

Multi-axial Elastic Averaging for Sub-micron Passive Alignment of Photonic Components

\*¹Simon Chun Kiat Goh, \*²Chun Fei Siah, \*²Baochang Xu, ²Yu Zhang, ²Mei Er Pam, ¹Enrico Guevarra, ¹Edwin Sze Ping Goh, ¹Lin Wang, ¹Brian Pile, ¹Arbiz Carlan, ¹James Yong Meng Lee, ¹Suresh Venkatesan, ²Yeow Kheng Lim, ²Aaron Voon-Yew Thean

<sup>1</sup>POET Technologies, <sup>2</sup>Singapore Hybrid-Integrated Next-Generation μ-Electronics Centre, National University of Singapore

#### Innovation

Develop pedestal-cavity pair for multiaxial elastic averaging to eliminate thermal error from solder reflow.

#### Result

Narrower optical power output distribution of P-down bonded lasers with triangle slide-stop guided design .

Advanced Freeform Optical Waveguide Coupled with Facet Microlens

Development and Testing

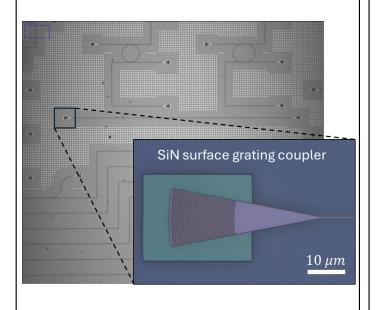

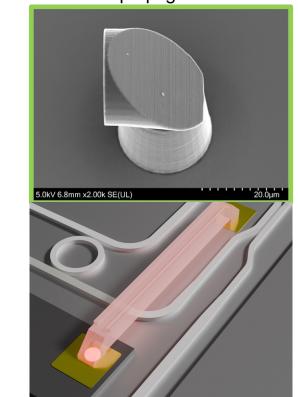

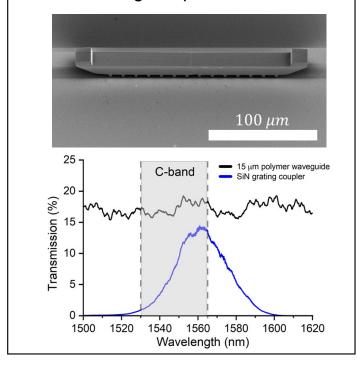

#### Problem statement

Conventional optical interconnect relies on silicon nitride (SiN) is based on planar fabrication methods. Alignment of external light source to SiN waveguide can be time consuming.

#### Innovation

Freeform lens can be printed using 2photon polymerization to divert light to another axis of propagation.

#### Result

Fabricated and characterized low loss broadband multimode surface-surface coupling waveguide which aims at reducing the complexity of coupling surface emitting components

### Thrust 4: Machine Learning Guided Failure Analysis & Diagnostic Capability Development for Next-Gen 3D-IC Packaging (Cont'd)

#### IEEE Electronic Components and Technology Conference (ECTC) 2025

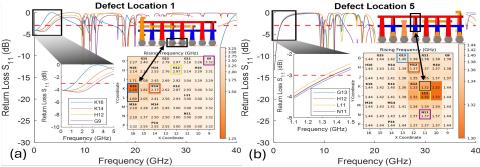

First Proof of 3D-IC Power Plane Defect Localisation via Frequency Domain Spatial Heat Mapping

Z.S. Shi, L. Lum, B. Zee, J.M. Chin, Y.K. Lim

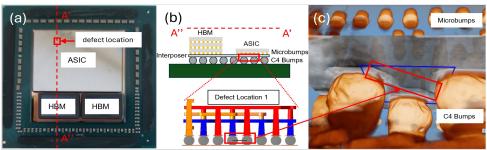

(a) A stacked graphics processing unit consisting of two high bandwidth memory (HBM) stacks and an application specific integrated circuit (ASIC) on a silicon interposer. (b) Defect location 1 in simulation corresponds to the actual published defect location, (c) where 3D XRM reveals an actual defect between two solder balls.

(a) Increased impedance from increased defect distances increases the resonant frequency. (b) The pins closest to the defects have the lowest impedance and lowest resonant frequency.

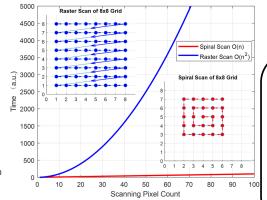

Big-O time complexity of raster scan versus spiral scan

Rearrange simulated return loss data from Ansys Electronic Desktop output (.csv) to readable format (.xlsx)

Find adjacent pairs pass the threshold value

Use a linear approximation to obtain the frequencies at threshold value

Taking the rising frequency for each offset and pincount, fill in the matrix (with avg. or max.)

Plot the 8 x 8 heat map

Flowchart of Python program extracting and parsing the simulated return loss data into a heat map by recording frequencies of individual pins past a threshold value.

#### Highlights of this work

- First proof solution of a challenging problem in 3D-IC power plane FA

- A novel signal processing method using heatmap to visualise return loss data to readily localise power plane defects

- A new spiral scanning method is proposed in place of conventional raster scanning to improve NDT scan time by one order of magnitude

- This work paves the way to predict defect locations using advanced frequency domain analysis

55

# SHINE's 2024 Research Highlights

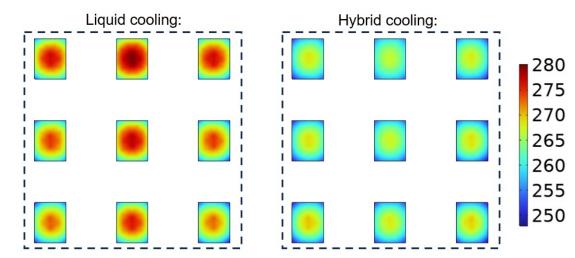

### Integrate Thermal Solution for Flexible Antenna System (On-going Work)

#### Advanced Heat Spreaders and Sinks with TIM

- Temperature distribution becomes more uniformed

- Overheating is delayed by 4.6 times and the equilibrium temperature is reduced to below 150 °C

- PA continued operating for more than 5 minutes

# **Proposed Flexible Antenna** Antenna Cu 35 µm ← GND Cu 17.5 µm Signal Cu 35 µm **Without Thermal Management With Proposed Thermal Management** Haven't stabilized 79 °C

Time (s)

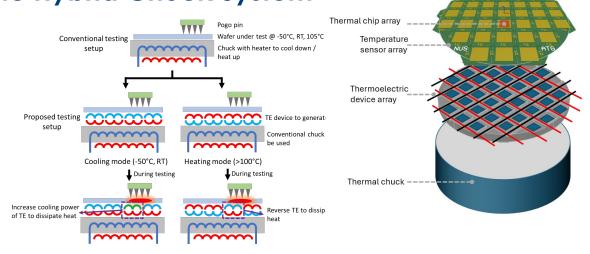

High-Speed Die Temperature control for GPU Wafer-level Testing Through Liquid-Thermoelectric Hybrid Chuck System

Wafer-level testing is a critical stage in the semiconductor manufacturing process, involving the testing of multiple ICs on a single wafer before the devices are separated into individual chips.

**Problem:** Advanced chip wafer testing generates significant localized heat, causing thermal stress and potential cracking of the wafer.

**Innovation:** Cutting-edge combination of speed, precision, and adaptability positions thermoelectric systems as a game-changing solution for advanced thermal management at wafer or chip scale, where performance outweighs cost and energy concerns.

- •Smart Heat Control: Thermoelectric systems offer precise, programmable thermal management by controlling heat flow via DC current, allowing for dynamic heat transfer and real-time adjustments in direction and intensity.

- •Ultra-Fast Thermal Response: Leveraging the Peltier effect, these devices provide rapid and efficient heating and cooling, enabling quick thermal stabilization with minimal lag.

- •Adaptive Localization: Thanks to their flexible design, thermoelectric devices can be custom-shaped to target and cool specific micro-areas, offering ultraprecise thermal control for advanced testing scenarios.

SHINE

### Flexible Antenna Design: Flexible L-band Phased Array

#### Highlight of This Work

- □ Various L-band flexible and foldable antennas have been designed and tested, enabling low-cost experimentation and selected candidates will be translated to C-band and X-band in the future.

- ☐ Highly Flexible and Foldable Antenna Array using Corrugated CCPM-based Patches is designed and tested. Accepted for ISAP 2024.

- Multilayer and Lightweight Conformal Antenna Using U-Slotted Patch and Stacked Polyimide Films is designed and tested. Accepted for ACAP 2024.

- Highly Flexible and Deployable Antenna Array Using Doublearch-shaped PTFE Films is designed and tested. Accepted for APMC 2024.

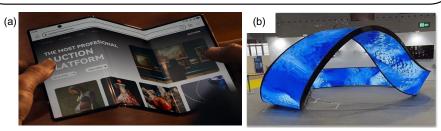

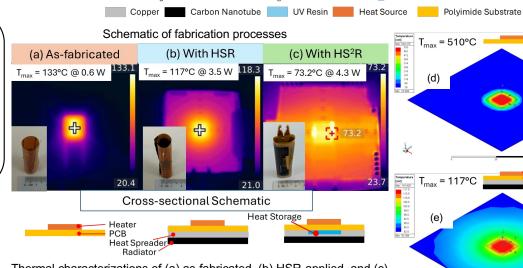

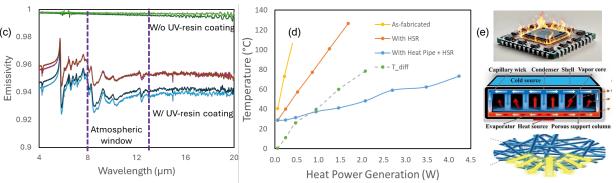

A Heat-Spreader, Storage & Radiator (HS2RTM) for Flexible Electronics: First

**Demonstration**

#### Highlights of this work

- ☐ First demonstration of passive thermal management solution for flexible electronics (up to 4.5 W, power consumption of phone: 0.2 W (idle) 1 W (making call)

- □ Passive thermal management is achieved through integration of heatspreader, heat storage, and printed radiator

- ☐ Heat-spreader & radiator (HSR) are shown to be scratch- and water-resistant

- □ Substrate can be rolled up to a **bend radius of 0.5 cm**

- ☐ It opens the possibilities for high power applications on flexible substrate

Flexible electronics ranging from (a) foldable phone to (b) outdoor LED display

Thermal characterizations of (a) as-fabricated, (b) HSR-applied, and (c)  $\rm HS^2R$ -applied PCB (inset: stowed mode at 1cm diameter); Simulation comparison of PCB (d) w/ and (e) w/o thermal solution at 3.5 W

(a) Morphology of CNT-based radiator under SEM; (b) Flexible fabricated HSR; (c) Emissivity of HSR; (d) Thermal performance under various conditions; (e) Stacked layers of HS<sup>2</sup>R Restricted Distribution - Confidential

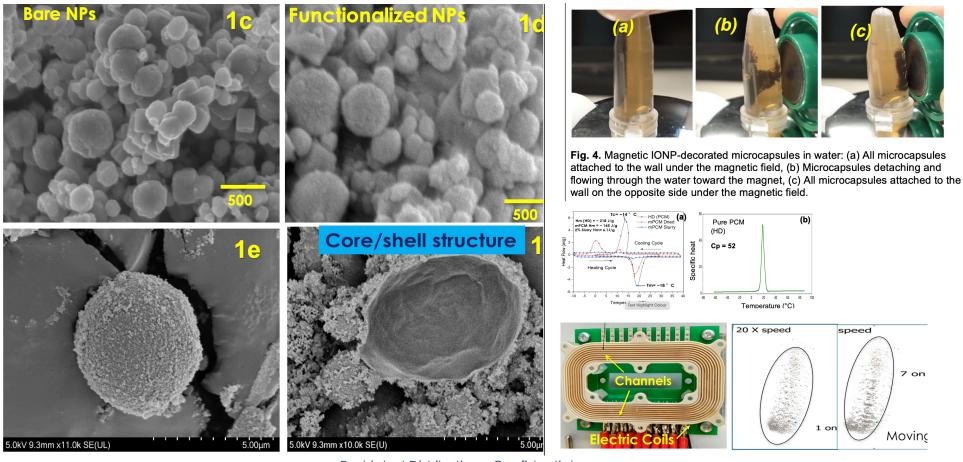

# (New)Engineered Magnetic Nanoparticle Suspension with thermal phase-change property – For Magnetic actuated Liquid Cooling

Restricted Distribution - Confidential