Advanced packaging and heterogeneous integration via fan-out, 2.5D interposer and 3D stacking

Navab Singh, PhD Deputy Executive Director (Research), IME, A\*STAR, Singapore

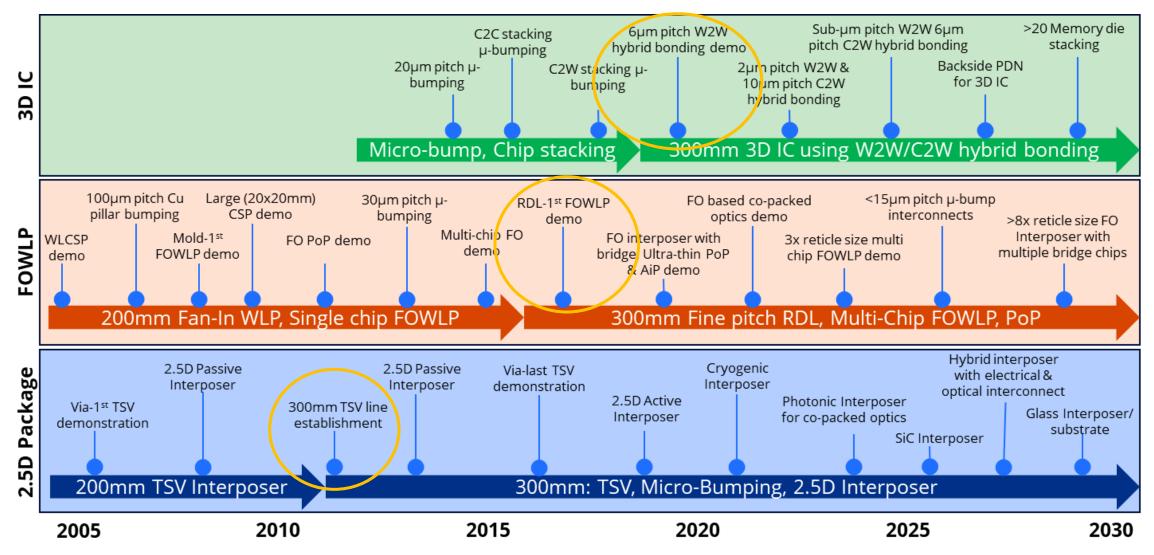

### **Our Advanced Packaging Journey**

• Driving the interconnect roadmap over the years through more than 50 consortia projects with >100 companies across the value chain.

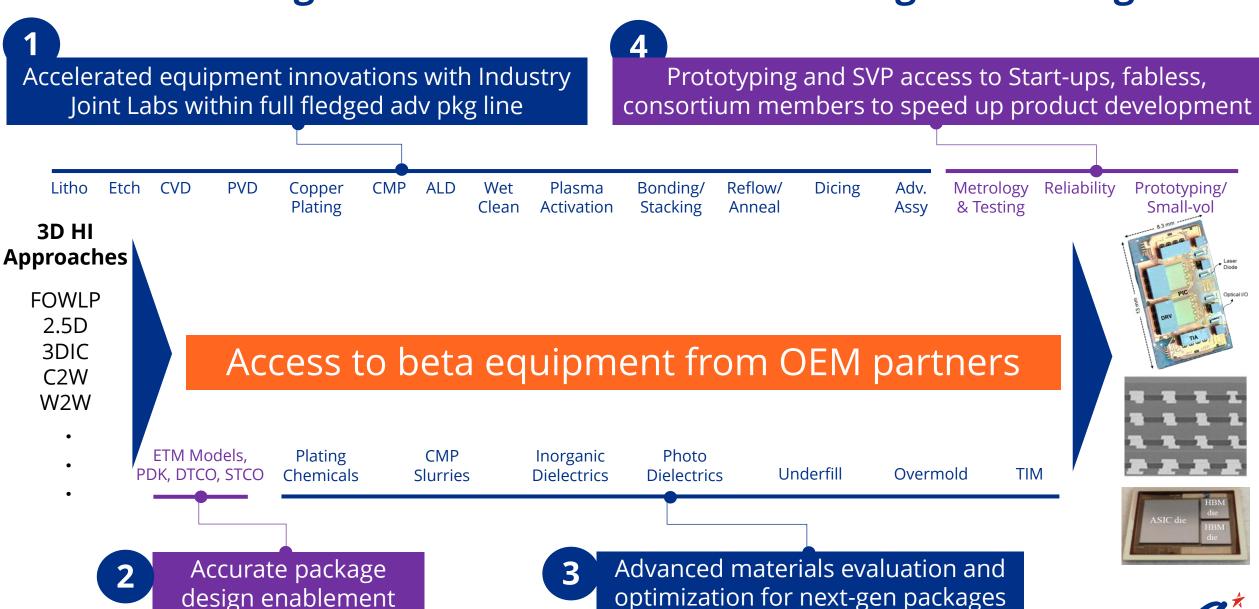

## Our Methodologies to Accelerate R&D in Heterogenous Integration

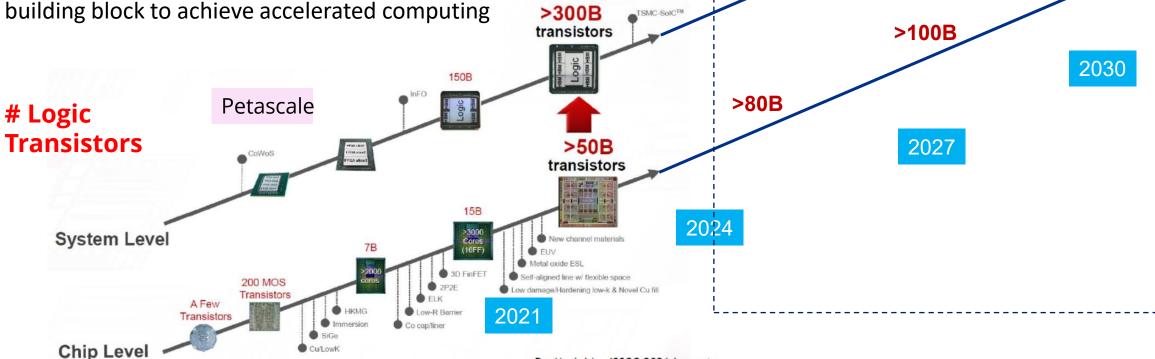

## **Compute Performance Drives Package System Scaling**

Zettascale (HPC)

>1T

>150B?

Future of System Scaling

Driven by Advanced Packaging

>500B

750B

- Generative AI demands increasing compute system performance (2X every year) to reach Zetta Scale Computing

- Exascale to Zetta-Scale Compute performance drives

Package integration to reach >1T transistors in Advanced

Package

- Ultra Large Multi-chiplet System in Package the key building block to achieve accelerated computing

Dr. Mark Liu, ISSCC 2021 keynote

Exascale(HPC)

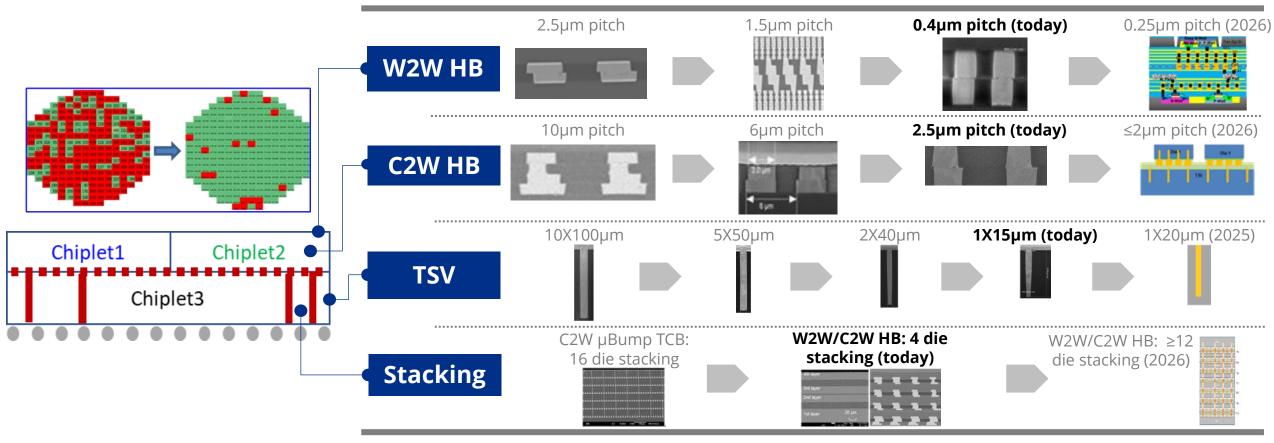

# Interconnect scaling for 3D packaging using Hybrid Bonding

#### Challenges

- Yield for hybrid bonding

- Access to 3D HI technology for product path-finding

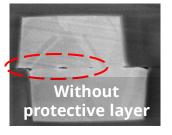

**Novel protective layer** to significantly improve bond yield & quality for fine pitch hybrid bonds

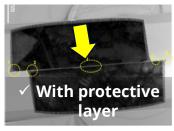

## **Interconnect Scaling for High Density Fan-Out Interposer**

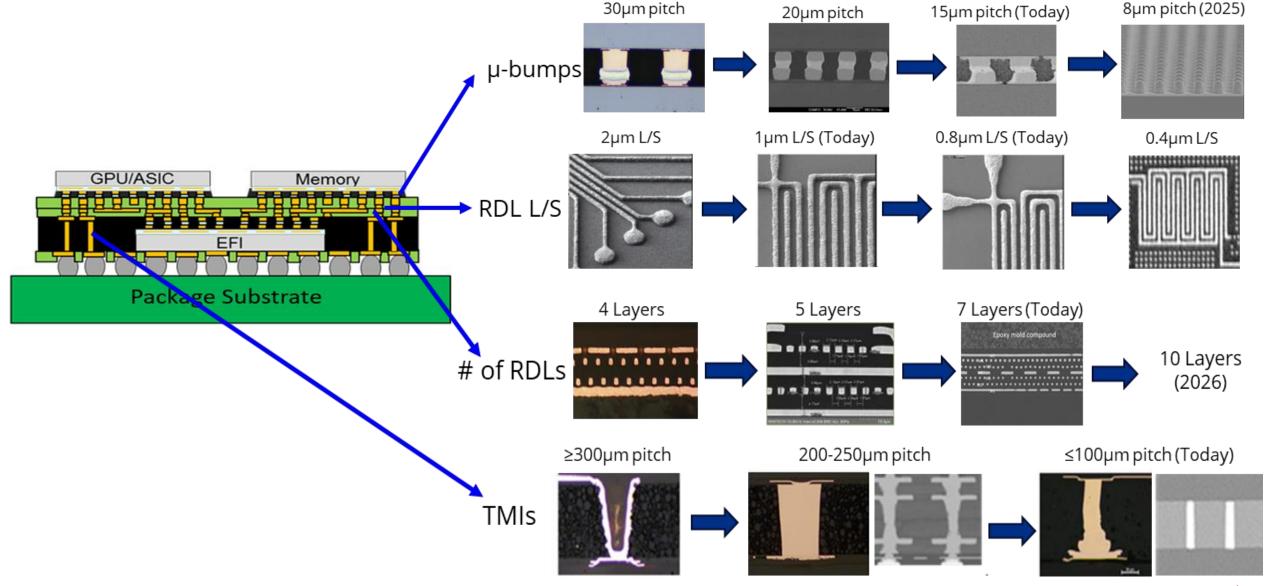

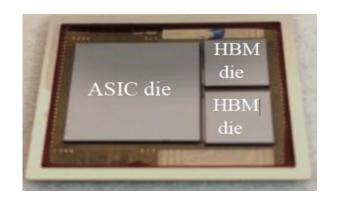

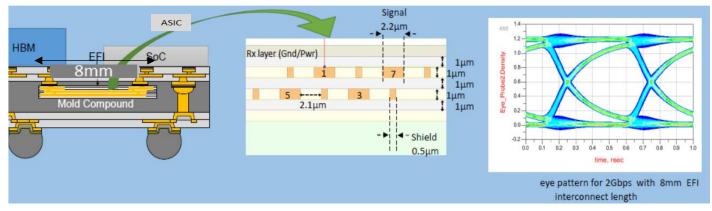

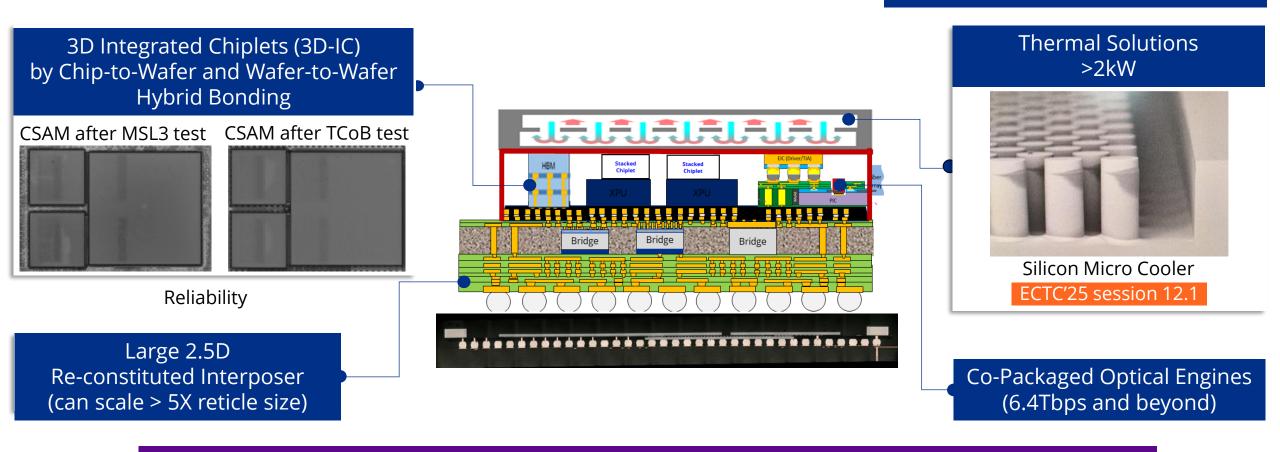

## **Embedded Fine-pitch Interconnect (EFI) Bridge 2.5D Interposer**

- Silicon interposers have been a go-to but expensive option for 2.5D integration.

- We developed cost-effective wafer level bridge interposer package in 2018.

- Embedded Fine-pitch Interconnect (EFI) Bridge Interposer Features

- EFI bridge for dense short fine-pitch interconnections (pitch= $1\mu$ m).

- RDL for long coarse interconnects.

- Can be scaled up to >6X reticle size >5000mm2 interposer size and beyond.

### **EFI Bridge Interposer Performance and Reliability**

CSAM after MSL3 test

CSAM after TCoB test

|       |            | TCOB testing (Board level) |         |        |         |

|-------|------------|----------------------------|---------|--------|---------|

| Group | Wafer info | 250 cyc                    | 500 cyc | 750cyc | 1000cyc |

| 1     | Material A | 0/7                        | 0/7     | 0/6    | 0/6     |

| 2     | Material B | 0/5                        | 0/5     | 0/4    | 0/4     |

Cross-section verification after TCOB testing

EFI bridge interposer is a scalable platform for large 2.5D Interposers for Ultra Large HPC/AI systems (>5X reticle size).

### From Components to Systems for AI Hardware

#### Challenge

Access to 1-stop shop to integrate heterogeneous components for energy efficient adv packages

Solution: Full-fledged Advanced Packaging line at IME to bridge gaps in integration of heterogeneous components into energy efficient systems

### Development through consortiums: 2.5D/3D Chiplets-HI Consortia

- Pre-competitively address industry needs

- More than 20 member companies across supply chain Fabless, IDM, foundries, OSAT, materials and equipment.

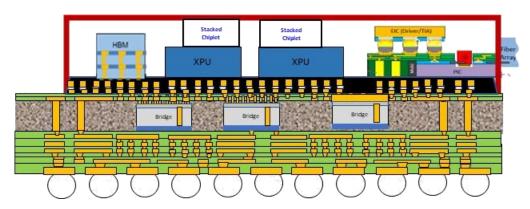

## HPC and CPO Chiplets Integration Consortium

Heterogenous Integrated Chiplet package

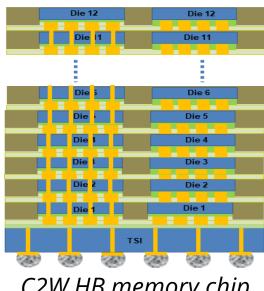

## **Chip-to-wafer Hybrid Bonding Consortium For 3D Stacking**

C2W HB memory chip stacked modules

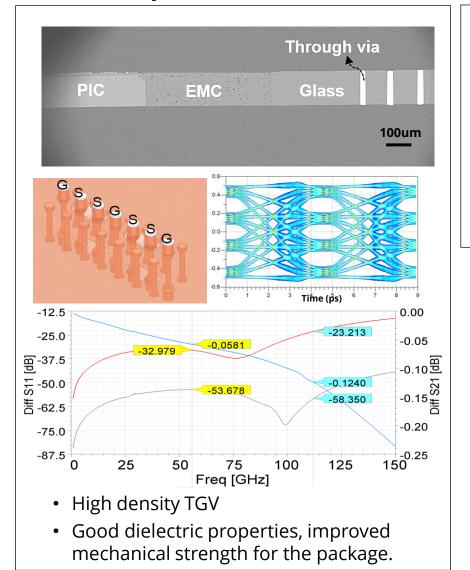

### **Next-Generation Interconnects for Optical Engines**

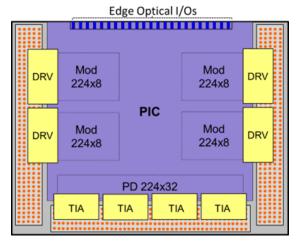

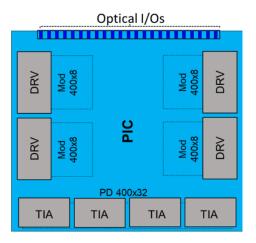

### **400 Gbps OE interconnects**

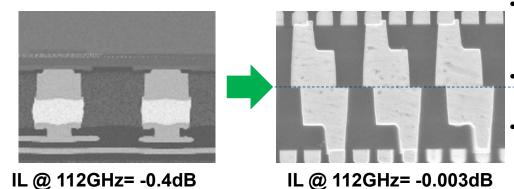

### **Hybrid Bonded OE**

- High density interconnects between EIC- PIC - Interposer

- Reduced EIC-PIC interconnect parasitics

- Very-low insertion loss at high frequency -Support higher bandwidth

6.4Tbps optical engine package design

12.8Tbps optical engine package design

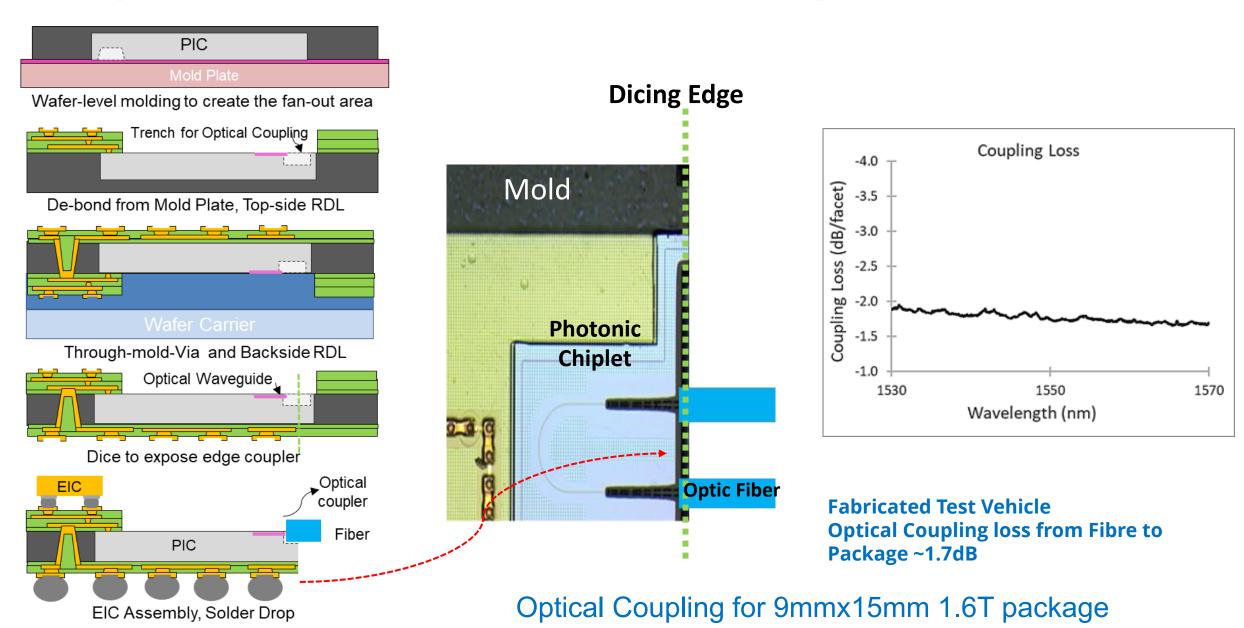

## **Optical Engine Process Flow & Edge Coupler Performance**

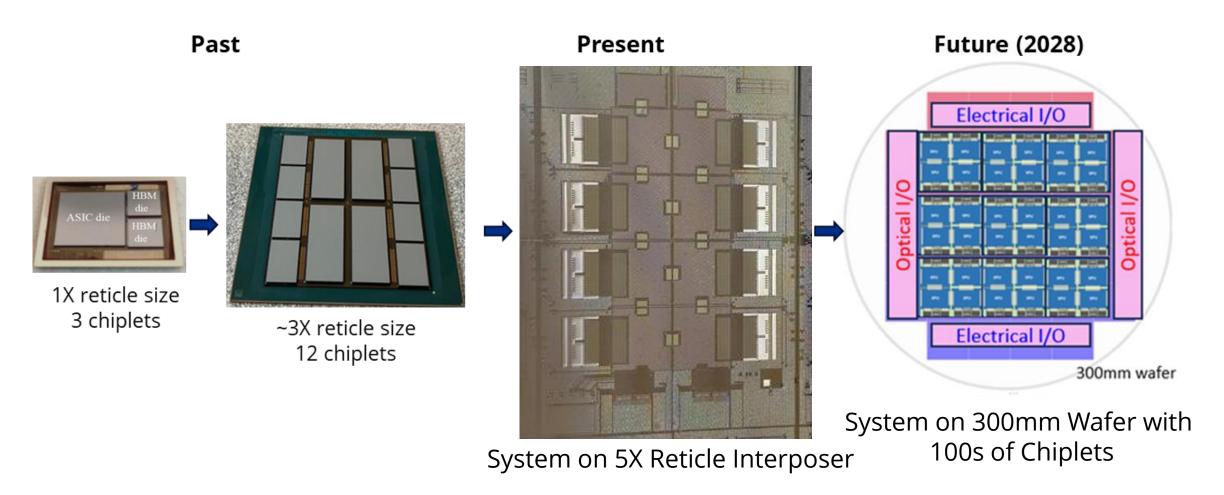

## 2.5D Interposer Scaling Up for AI and HPC

Key Challenge: Wafer Scale Interposer with Electrical and Optical wiring to integrate XPUs, HBMx, IVR, peta-scale optical I/O, Thermal Cooling.

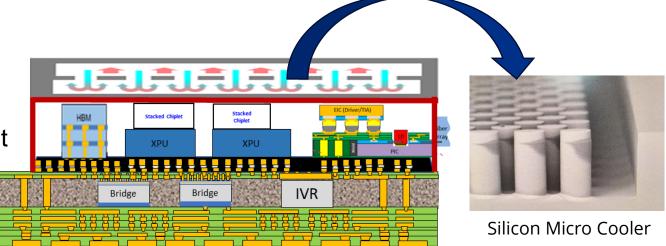

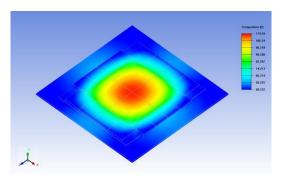

## System Thermal solution for Heterogeneous Integration

### **Thermal Challenges**

- High power dissipation requirement

- Limited space for cooling structure arrangement

- Severe in-package temperature gradient

### **Approach**

- Thermal performance evaluation and improvement

- Si Micro cooling technology targeting main heat cores

- Package integrated cooling for effective heat dissipation

- IVR integrated within interposer

### **Typical Specs**

- ✓ To achieve heating power dissipation >2000W

- ✓ To handle thermal issue of large Interposer >70mm x 70mm

Schematic image of micro-fluid cooling solution for high power dissipation

Package power > 2000W

Tmax\_xPU < 110°C

$Tmax\_HBM < 90^{\circ}C$   $Tmax\_OE < 80^{\circ}C$

### **Summary**

- AI-HPC hardware drive Package Level System Scaling enabled by Multi-Chiplet Heterogeneous Integration packaging for Compute, Memory, OE, IVR and Thermal Cooling.

- IME's Advanced packaging line provides ready access to Heterogeneous Integration Technologies to Industry and Academia.

- We cherish deep collaborations across the advanced packaging ecosystem - critical to develop broad, deep new capabilities to address current/next generation AI hardware challenges.

- ✓ Consortia to address pre-competitive challenges facing Industry

- ✓ Product prototyping and Tech-transfer.

- ✓ Working with Academia to accelerate exploration and pathfinding in heterogeneous integration

Looking forward to expanding our ecosystem of partnerships to accelerate innovations in Heterogeneous Integration!

**ASTAR-SG**