WORKSHOP – May 12-13, 2025 - Warsaw

### **International Cooperation on Semiconductors**

EU and Non-EU Strengths, Weaknesses, Dependencies, Opportunities for International Collaboration

### Francis Balestra (CNRS/Grenoble INP-UGA/Sinano Institute)

ICOS INTERNAL WORKSHOP – May 12-13<sup>th</sup> 2025 - Warsaw Name

• ICOS Project starts in January 2023 for three years, it is funded by the Horizon Europe research program.

Coordinator

**Technical co-Coordinator**

• An ambitious project in the framework of the European strategy for semiconductors

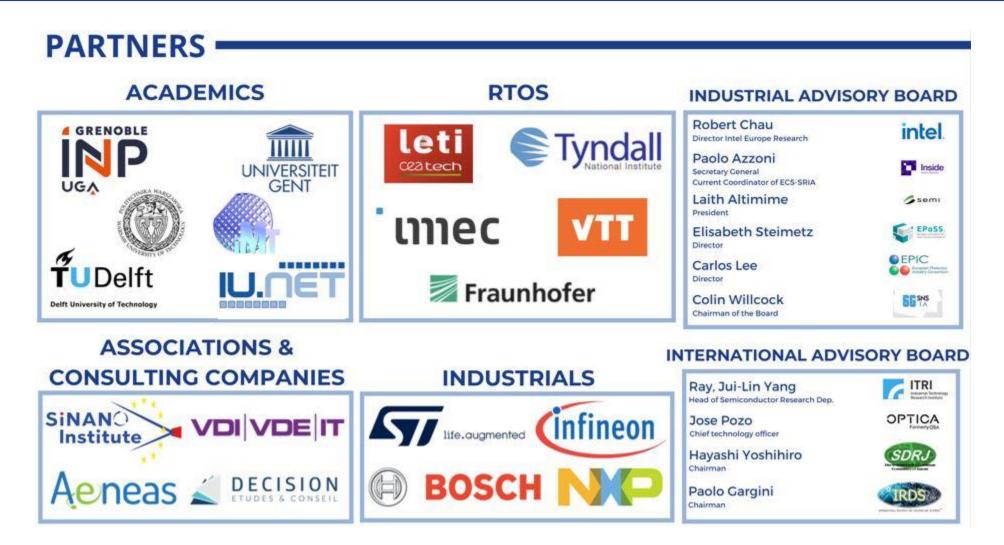

# PARTNERS & ADVISORY BOARDS

## **Motivation & Objectives**

- Semiconductors & Semiconductor-based photonics are pivotal technologies for almost all existing industrial sectors, as demonstrated by the recent chips shortages

- International cooperation is key for speeding up technological innovation (e.g. ITRS/IRDS, IPSR-I, ECS-SRIA, NEREID), reducing cost by avoiding duplicated research, strengthening complex supply and value chains, and is encouraged by the new strategies of leading semiconductor countries

- => To build **balanced semiconductor partnerships** with like-minded countries

- => To set out cooperative framework on *initiatives of mutual interest*

- => To identify and support the establishment of the most promising scientific international collaborations

- => To support the growth of the European Semiconductor industry through **focused research alliances** based on awareness of advanced research activities

- => To strengthen **Europe's and partner Country's positions** in global value chains in this area and to contribute to the **EU Chips Act, Green deal and Digital Agenda**

# **Objectives of ICOS**

### Investigated countries:

- Japan

- The United States of America

- India

- The Republic of Korea

- Taiwan

- Singapore

- China

- Canada, Malaysia (for some analysis)

# **Main scientific topics**

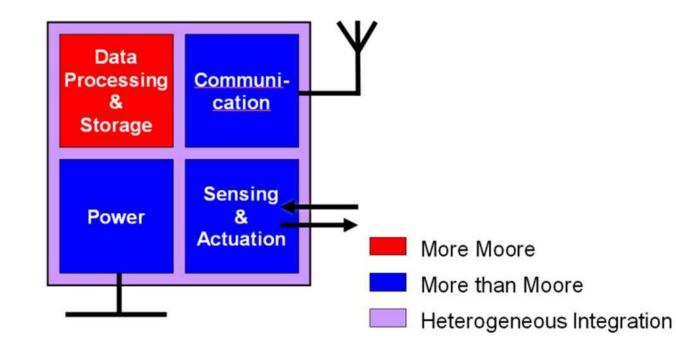

Advanced computing & Advanced functionalities: sensing, RF & optical communications, optical devices, energy harvesting, power devices, ...

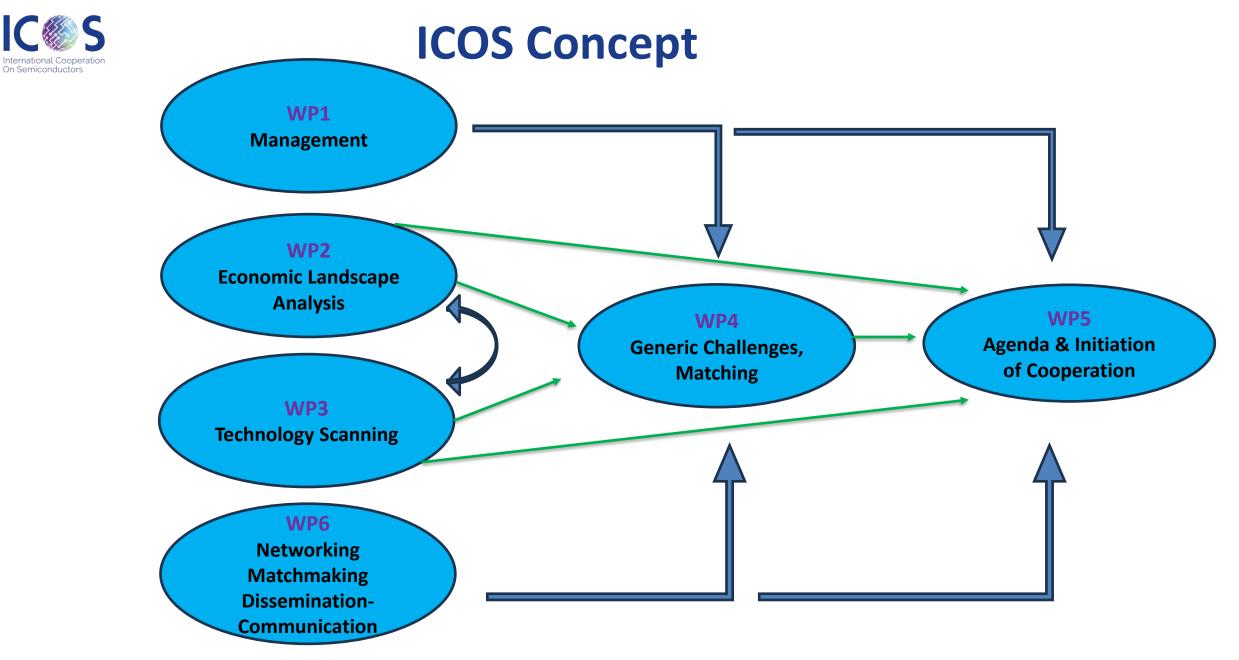

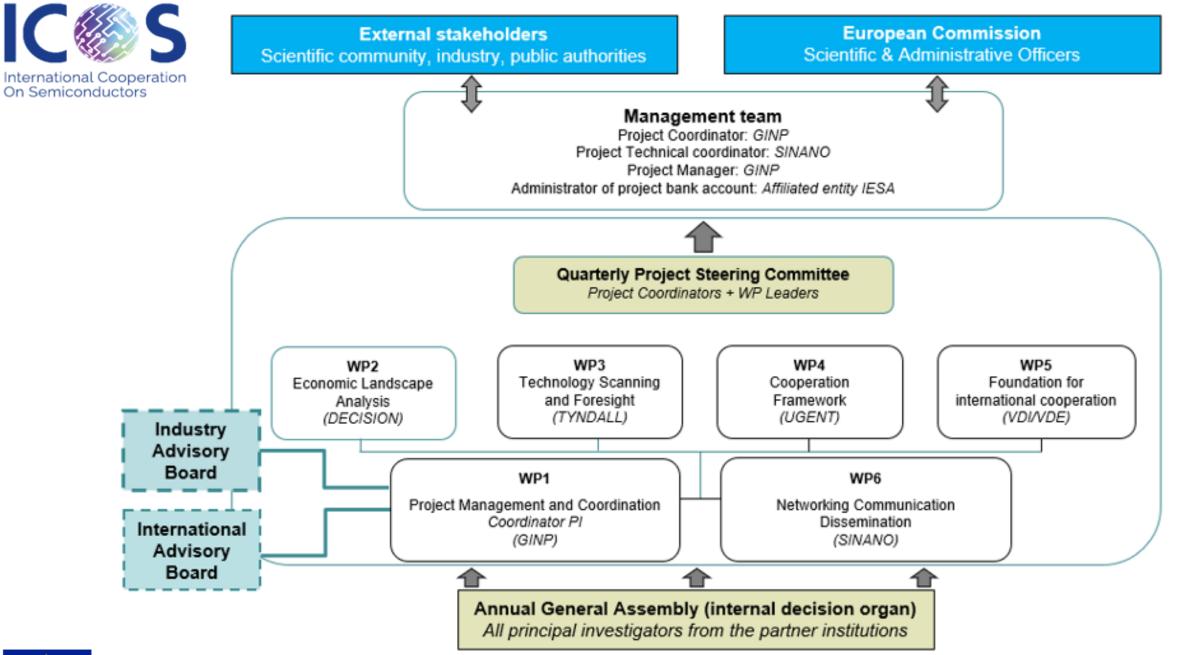

#### Structure of ICOS project & stakeholders

# **IMPLEMENTATION**

#### **IMPLEMENTATION** -

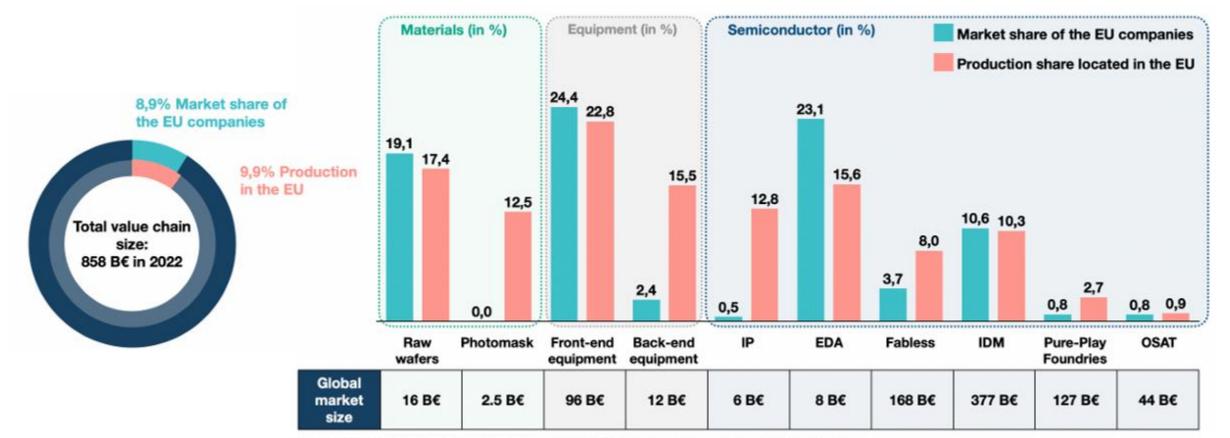

#### EXHAUSTIVE ANALYSIS OF SEMICONDUCTORS' VALUE CHAINS, FOR ELECTRONICS & PHOTONICS

Identification of :

- EU's economic and industrial strengths & weaknesses

- Strategic dependencies

- Market and cooperation opportunities

#### IDENTIFICATION OF RESEARCH AREAS FOR INTERNATIONAL COOPERATION

Identification of next generation & emerging technologies, especially in advanced computation and functionalities.

DETERMINATION OF MOST INTERESTING COUNTRIES FOR INTERNATIONAL COOPERATION

Identification of challenges for which international cooperation is critically important.

#### AGENDA FOR AND INITIATION OF INTERNATIONAL COOPERATIONS

- Dialogue with actors of existing cooperation

- International collaboration with non-EU national authorities

- Define standardisation needs and activities

- Support the European Commission

International Cooperation On Semiconductors

In comparison, the EU account for 17% of the global GDP in 2022<sup>29</sup>.

Source: DECISION Etudes & Conseil

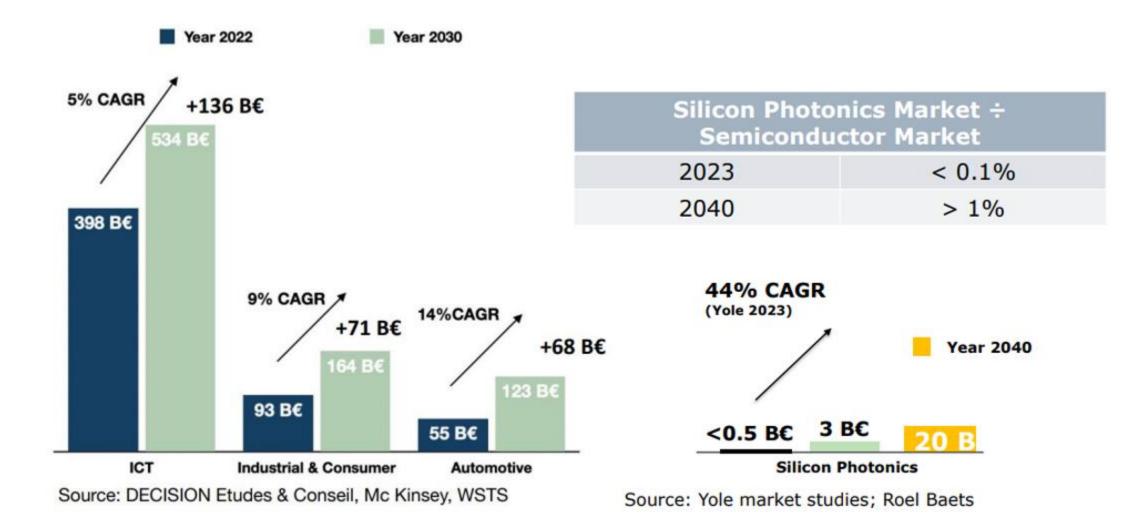

## **Growth in Electronic and Photonic Chips**

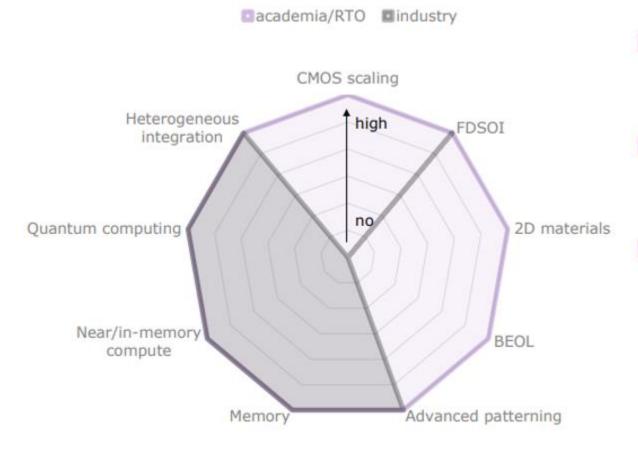

## Main technologies: EU & non-EU / EU

- R&D very strong in all areas of compute

- Unique strong position in EUV lithography

- In general, industrial EU players lacking to take up R&D

# Challenges, possibles solutions & Collaboration opportunities: "Advanced computing"

- Classical' Logic Scaling Roadmap beyond FinFET technology that extends devices structures through sub nm nodes (e.g., GAA and CFET architectures)

- Exploration of 'Fully Depleted SOI' technology for Power Efficient Analog and RF applications

- Exploration of alternative channel materials (e.g., 2D materials)

- Extension of the scaling of BEOL technologies, through the use of Ru, Airgap or Graphene-based metallization, by reducing the associated RC network

- Added BEOL functionality through the introduction of new materials such as 2D, oxide semiconductors and ferroics

- Exploration of the use of BEOL Non-Volatile Memories (using for example resistive RAM such as FeRAM, MRAM, PCRAM) to supplement/replace charge-based memories, for in-memory computing (eNVM), and for Power Efficient Neuromorphic-based architectures

- Photonic chips for optical interconnects and quantum information processing

- Demonstration of the capability of the 'Buried Power Rail delivery' to decongest the interconnection density that is becoming the most limiting factor for the scaling at 2nm and below

- Enablement of the **High-NA EUV lithography** for the patterning of 2nm nodes and beyond

- Usage of 3D integration to desegregate the classical large area chips into chiplets that will be much more power efficient when reconstruct using 3D integration design flow and associated toolbox

- Cryogenic electronics for power saving and quantum computing

### Challenges & possible solutions & collaborations opportunities: "Advanced functionalities"

- Innovation in new, highly sensitive and more versatile sensors requiring more advanced sustainable (bio)materials innovation and integration

- For energy harvesters the improvement of the performance/ efficiency is as important as the development of "green" materials

- Wide band gap (e.g. SiC, GaN) and ultrawide band gap materials (e.g. AlN, GaOx, diamond) for power

- Flexible, Printable, Wearable Electronics: Future Hybridization of Flexible & Si-based electronics

- Heterogeneous integration of best materials for target application

- Advanced design tools, including multi-physics simulation for first-time-right modelling capabilities

- **Rapid prototyping** to bypass long chip iteration cycles (e.g. PDK, ADK availability)

- Packaging that meets multiple design requirements such as optical, electrical, mechanical, thermal, RF, (bio-)fouling etc.

- Webinars

- Workshops

- Contribution to Regional & International Technology Roadmaps (IRDS)

- International R&D&I cooperation on topics of mutual interests

- Exchange of researchers

- Access to Research Infrastructures

- Standardisation needs for emerging technologies

This project has received funding from the European Union's Horizon Europe research and innovation programme under GA N° 101092562

# Thank you for your attention

### icos-semiconductors.eu

### Contact:

Francis Balestra < Francis.balestra@grenoble-inp.fr>

Funding from Horizon Europe under grant agreement 101135568