#### WORKSHOP

# Key Emerging Technologies for future

**Industrial Applications**

The first iteration

Salahuddin Nur and Ryoichi Ishihara

Delft University of Technology

#### Semiconductor standards

#### Why do we analyze?

- Growing importance of semiconductors for European industry and society

- Strengthen EU's position in global value chains in semiconductor: EU Chips Act

- Semiconductor standardization = Critical to ensure interoperability, efficiency and technical leadership

- Identify and map the gaps in existing value chains potentially induced by a lack of international standards

- provide a set of recommendations for standardization activities

- Identify needs of new standards for emerging technologies, for which value chains are under construction

- provide specification of these needs and potential recommendations

- Recommendation on Standardisation (July 2025)

- Now it is working in progress!

## Approach

- List devices and process steps

- Aeneas, input from ICOS WP3

- Form a technical working group (TWG)

- ICOS, StandICT.eu and AllPROS.eu

- Identify standard development organizations (SDOs) and working groups

- List and classify the standards (~2500!) into types of devices, process steps and applications

- Analyse the statistics and identity and map the gaps

## Original classifications

|                          |          |             |            |           |          |       | Front-End | <u> </u> | Software |       |

|--------------------------|----------|-------------|------------|-----------|----------|-------|-----------|----------|----------|-------|

|                          | Material | Equipment   |            | IC Design |          |       | Fab.      | Services | provider | tech. |

|                          |          | Front-End   | Back-End   |           |          |       |           |          |          |       |

|                          |          | Equipment & | Equipment  |           | IP       | Whole |           |          |          |       |

| <u>Devices</u>           |          | Services    | & Services | EDA       | Blocks   | IC    |           |          |          |       |

| Al                       |          |             |            | Χ         | Χ        | Χ     |           |          | Χ        |       |

| Chiplets / Advanced      |          |             |            |           |          |       |           |          |          |       |

| packaging                | Χ        |             | Χ          | Χ         |          | Χ     | Χ         | Χ        | Χ        |       |

| Energy efficiency        |          |             |            |           |          |       |           |          |          |       |

| and sustainability       | Χ        | X           | Χ          | Χ         |          | Χ     | Χ         | Χ        |          | Χ     |

| Sub-5nm                  | Χ        | Χ           |            | Χ         |          | Χ     | Χ         |          |          |       |

| Advanced Litho.          | Χ        | X           |            | Χ         |          | Χ     | Χ         |          |          |       |

| <b>Quantum computing</b> | Χ        | X           | Χ          | Χ         |          | Χ     | Χ         | Χ        | X        | Χ     |

| Neuromorphic/ReRA        |          |             |            |           |          |       |           |          |          |       |

| M/AI chip                | Χ        |             |            | Χ         | Χ        | Χ     | Χ         |          |          |       |

| Edge computing           | Χ        |             | X          | Χ         | <u>X</u> | Χ     | Χ         | Χ        | X        | Χ     |

| Photonics                | Χ        |             | X          | Χ         | Χ        | Χ     | Χ         | Χ        | X        | Χ     |

Cybersecurity

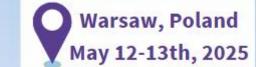

## SDOs Classifications: Applications

### **New Classifications**

| E C                                   | Mate<br>rials | Equipment<br>Front-End<br>and services | Equipment Back-End and services | IC Design EDA tools and services | IC<br>Design<br>Blocks | IC Design<br>Whole IC | Front-End<br>Fabrication |

|---------------------------------------|---------------|----------------------------------------|---------------------------------|----------------------------------|------------------------|-----------------------|--------------------------|

| Sub-5nm                               |               |                                        |                                 |                                  |                        |                       |                          |

| Photonics                             |               |                                        |                                 |                                  |                        |                       |                          |

| Quantum computing                     |               |                                        |                                 |                                  |                        |                       |                          |

| Neuromorphic/ReRAM/AI Chip            |               |                                        |                                 |                                  |                        |                       |                          |

| AI - Applications                     |               |                                        |                                 |                                  |                        |                       |                          |

| Edge & Cloud computing - Applications |               |                                        |                                 |                                  |                        |                       |                          |

| Wide bandgap                          |               |                                        |                                 |                                  |                        |                       |                          |

| Flexible hybrid electronics           |               |                                        |                                 |                                  |                        |                       |                          |

| MEMS                                  |               |                                        |                                 |                                  |                        |                       |                          |

| Generic                               |               |                                        |                                 |                                  |                        |                       |                          |

Advanced Lithography, Chiplets/advanced packaging and Energy efficiency & sustainability are included in the process steps

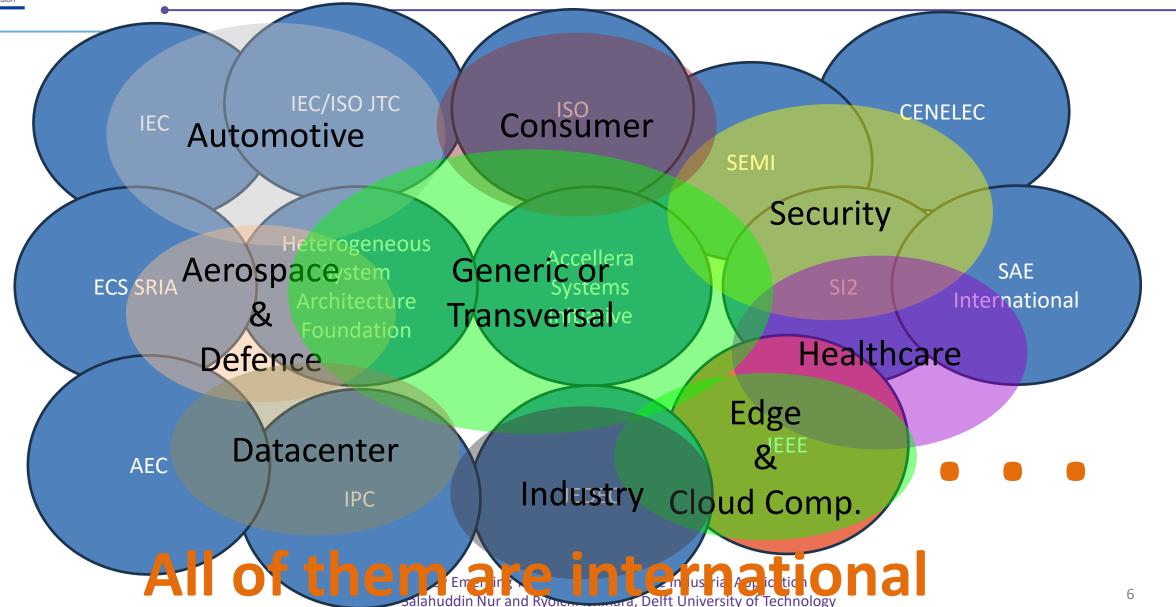

#### # standardizations vs devices

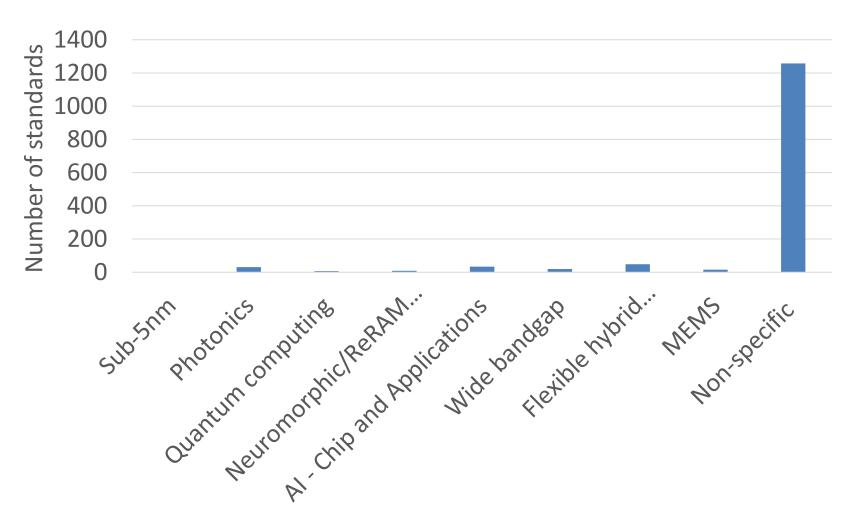

#### # standardizations vs devices

#### w.o. non-specific devices

#### **Observation: Devices**

- Moderately covered for photonics/AI/Flexible-hybrid electronics/Wide-bandgap/MEMs devices.

- Lack in emerging devices (sub-5nm, quantum, neuromorphic)

- Did not analyze IEEE yet

- Difficult to identify from abstract

- Needs deep dive in Non-specific devices

- SDOs not identified

- Potentially the gap

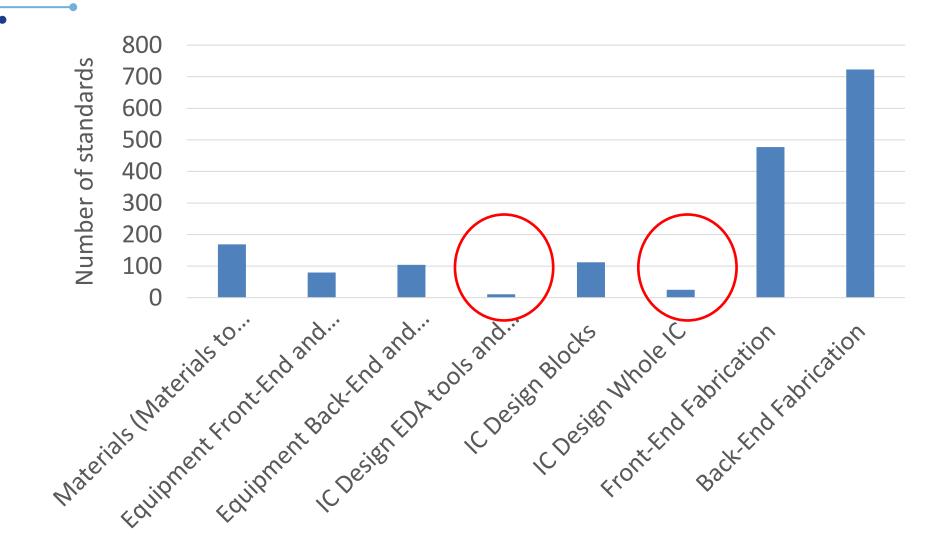

## Observation: Process Steps

- Well covered for Front/backend fabrication

- Somewhat limited for Front/backend equipment

- Difficult to distinguish between Equipment and Fabrication

- Very few for IC design tool and IC whole design

- Did not analyze IEEE yet

- Potentially the gap

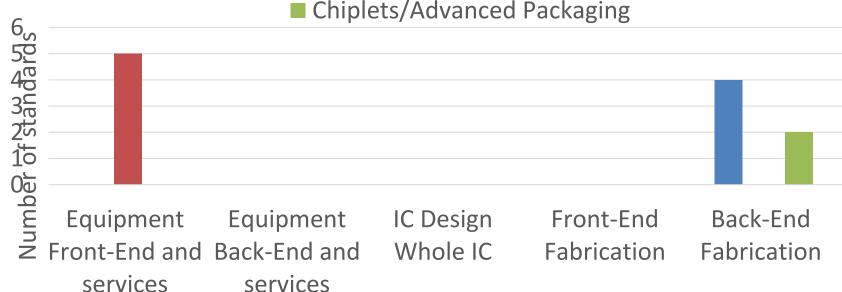

## # standardizations vs process steps for emerging technologies

- Energy efficiency & Sustanability

- Advanced Lithography

- Chiplets/Advanced Packaging

# Observation: Process steps for emerging technologies

- Very limited numbers of standardization for Energy efficiency & sustainability, Advanced lithography, and Chiplet/Advanced Packaging

- No IEEE analysis yet

- Missing SDOs

- Hidden in the generic process steps

- Potentially the gap

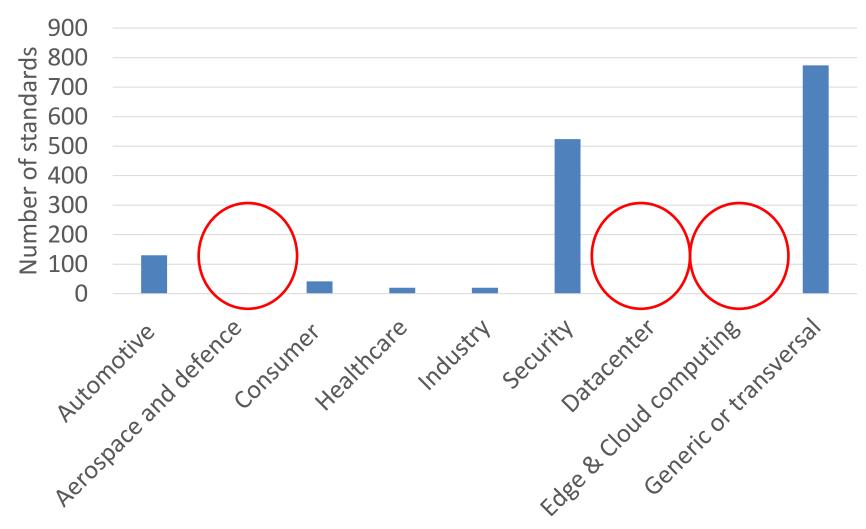

## # standardizations vs applications

## Observation: Applications

- Well covered for Generic/Transversal and Security

- Limited for Automotive/Consumer/Health/Industry

- Included in Generic/Tranversal

- None for Aerospace&Defense/Data center/Edge

- No IEEE analysis yet

- Included in Generic/Transversal

#### Conclusions

- The first round of semiconductor standardization landscape analysis has been performed.

- AI/Photonics/Flexible devices and Front/Backend fabrication process seem to be covered moderately well.

- Coverages in sub-5nm/quantum/neuromorphic devices, advanced litho./chiplet/energy efficiency and sustainability/advanced packaging, and IC design tool/whole design steps are very limited.

- Hidden in IEEE standards and/or generic devices/process steps

- Missing SDOs

- Potentially the gaps

#### Outlook

- Find SDOs/WG for the emerging devices/process steps and potential national activities

- Interview with experts

- Organize a webinar

- 2<sup>nd</sup> iteration

- Analyze the IEEE standards (~2500 entries)

- Deep dive into Non-specific devices/process standards

- Add new (sub) classifications, e.g., energy harvester

- Increase granularity of the analysis map (device vs. process steps) and identify the gaps

- Produce specifications and recommendations

- Finalize the report in July

## Acknowledgement

- Silvana Muscella, Barbara Iryde, XiaoRui Zhang, Maria Giuffrida (StandICT.eu)

- Karim Tobich (Cyber Security & Technology Consultancy)

- Thomas Reibe (EU)

- Patrick Cogaz and Vincent Le Meau (Aneas)

- Abhishek Ramanujan Analog devices

- Gianluca Milano Intrim

- Richard Pitown ResolutePhotonics

- AllPROS.eu, VLC Photonics, Grenoble-inp, IMT, ADAPT Centre and others

This project has received funding from the European Union's Horizon Europe research and innovation programme under GA  $N^{\circ}$  101092562

www.icos-semiconductors.eu