# **Recommendations for International Research Cooperation**

Project Number: 101092562 Project Acronym: ICOS Project Title: International Cooperation On Semiconductors Responsible: IUNET Submission date: 03 March 2025

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|--------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                        | Authors | , , , , , , , , , , , , , , , , , , , ,                | Version | 11 |

|                                                        |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                        |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                        |         | Georgios Fagas                                         |         |    |

#### **Deliverable Information**

| Project Title:                 | International Cooperation on Semiconductors (ICOS) |

|--------------------------------|----------------------------------------------------|

| Project Number:                | 101092562                                          |

| Deliverable Number:            | D3.3                                               |

| Responsible Partner:           | IUNET                                              |

| Work Package Number and Title: | WP3 – Technology Scanning and Foresight            |

| Version:                       | 10                                                 |

| Revision Date:                 | 28/02/2025                                         |

#### Type of deliverable: Report

#### Dissemination Level: Public

#### Revisions

| Version # | Date     | Type of Change                                    | Lead Author     |

|-----------|----------|---------------------------------------------------|-----------------|

| V1        | 30/12/24 | First Draft                                       | Paolo Motto Ros |

| V2        | 29/01/25 | Updates with contributions from the partners      | Paolo Motto Ros |

| V3        | 30/01/25 | First internal review                             | Danilo Demarchi |

| V4        | 01/02/25 | Second draft                                      | Paolo Motto Ros |

| V5        | 04/02/25 | Updates with feedback from the partners           | Danilo Demarchi |

| V6        | 07/02/25 | Second internal review                            | Danilo Demarchi |

| V7        | 12/02/25 | Updates with last contributions from the partners | Paolo Motto Ros |

| V8        | 17/02/25 | Third internal review                             | Paolo Motto Ros |

| V9        | 21/02/25 | Fourth internal review and minor corrections      | Danilo Demarchi |

| V10       | 27/02/25 | Fifth internal review and minor corrections       | Georgios Fagas  |

| V11       | 28/02/25 | Final version                                     | Paolo Motto Ros |

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|--------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                        | Authors | , , , , , , , , , , , , , , , , , , , ,                | Version | 11 |

|                                                        |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                        |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                        |         | Georgios Fagas                                         |         |    |

#### Approvals

| Name, Organisation | Role        | Validation date |

|--------------------|-------------|-----------------|

| F.Balestra         | Coordinator | 28/02/2025      |

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|--------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                        | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                        |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                        |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                        |         | Georgios Fagas                                         |         |    |

# **Table of Contents**

| TABL  | E OF CONTENTS                                                                                            | 4  |

|-------|----------------------------------------------------------------------------------------------------------|----|

| EXEC  | UTIVE SUMMARY                                                                                            | 7  |

| 1 C   | OVERVIEW                                                                                                 | 7  |

| 1.1   | Purpose                                                                                                  | 7  |

|       | IRST OBJECTIVE: INVESTIGATION AND EVALUATION METHODOLOGY/<br>/IEWORK                                     | 8  |

| 2.1   | Proposed Approach                                                                                        | 8  |

|       | ECOND OBJECTIVE: QUANTITATIVELY ASSESS THE KEY POINTS ABOUT<br>INTERNATIONAL RESEARCH COOPERATION TOPICS | 13 |

| 3.1   | Logic                                                                                                    | 14 |

| 3.1.  | 1 EDA & IP                                                                                               | 14 |

| 3.1.  | 2 Chip Design                                                                                            | 14 |

| 3.1.  | 3 System Design                                                                                          | 15 |

| 3.1.4 | 4 Materials Integration                                                                                  | 15 |

| 3.1.  | 5 Components                                                                                             | 16 |

| 3.1.  | 5 Manufacturing (front-end)                                                                              | 16 |

| 3.1.  | 7 Manufacturing (back-end)                                                                               | 17 |

| 3.1.  | B Equipment & Tools (front-end)                                                                          | 17 |

| 3.1.9 | 9 Equipment & Tools (back-end)                                                                           | 18 |

| 3.2   | Memory                                                                                                   | 18 |

| 3.2.  |                                                                                                          | 18 |

| 3.2.  |                                                                                                          | 19 |

| 3.2.  |                                                                                                          | 19 |

| 3.2.4 | 5                                                                                                        | 20 |

| 3.2.  |                                                                                                          | 20 |

| 3.2.  |                                                                                                          | 21 |

| 3.2.  |                                                                                                          | 21 |

| 3.2.  |                                                                                                          | 22 |

| 3.2.9 | 9 Equipment & Tools (back-end)                                                                           | 22 |

| 3.3   | Mixed-Signal Processing                                                                                  | 23 |

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|--------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                        | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                        |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                        |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                        |         | Georgios Fagas                                         |         |    |

| 3.3.1  | EDA & IP                                                 | 23 |

|--------|----------------------------------------------------------|----|

| 3.3.2  | Chip Design                                              | 23 |

| 3.3.3  | System Design                                            | 24 |

| 3.3.4  | Materials Integration                                    | 24 |

| 3.3.5  | Components                                               | 24 |

| 3.3.6  | Manufacturing (front-end)                                | 25 |

| 3.3.7  | Manufacturing (back-end)                                 | 25 |

| 3.3.8  | Equipment & Tools (front-end)                            | 25 |

| 3.3.9  | Equipment & Tools (back-end)                             | 25 |

| 3.4 Pc | owering                                                  | 26 |

| 3.4.1  | EDA & IP                                                 | 26 |

| 3.4.2  | Chip Design                                              | 26 |

| 3.4.3  | System design                                            | 27 |

| 3.4.4  | Materials integration                                    | 28 |

| 3.4.5  | Components                                               | 29 |

| 3.4.6  | Energy Storage Devices (solid state thin film solutions) | 30 |

| 3.4.7  | Manufacturing (front-end)                                | 30 |

| 3.4.8  | Manufacturing (back-end)                                 | 31 |

| 3.4.9  | Equipment & Tools (front-end)                            | 32 |

| 3.4.10 | Equipment & Tools (back-end)                             | 32 |

| 3.5 Se | ensing                                                   | 33 |

| 3.5.1  | EDA & IP                                                 | 33 |

| 3.5.2  | Chip Design                                              | 34 |

| 3.5.3  | System Design                                            | 35 |

| 3.5.4  | Materials Integration                                    | 35 |

| 3.5.5  | Components                                               | 36 |

| 3.5.6  | Manufacturing (front-end)                                | 36 |

| 3.5.7  | Manufacturing (back-end)                                 | 37 |

| 3.5.8  | Equipment & Tools (front-end)                            | 38 |

| 3.5.9  | Equipment & Tools (back-end)                             | 39 |

| 3.6 Co | ommunicating                                             | 39 |

| 3.6.1  | EDA & IP                                                 | 39 |

| 3.6.2  | Chip Design                                              | 40 |

| 3.6.3  | System Design                                            | 40 |

| 3.6.4  | Materials Integration                                    | 40 |

| 3.6.5  | Components                                               | 41 |

| 3.6.6  | Manufacturing (front-end)                                | 41 |

| 3.6.7  | Manufacturing (back-end)                                 | 41 |

| 3.6.8  | Equipment & Tools for test/metrology                     | 42 |

| 3.6.9  | Equipment & Tools (front-end)                            | 42 |

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|--------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                        | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                        |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                        |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                        |         | Georgios Fagas                                         |         |    |

#### 3.6.10 Equipment & Tools (back-end) 3.7 **Photonics** 3.7.1 EDA & IP 3.7.2 Chip Design 3.7.3 System Design 3.7.4 Materials Integration 3.7.5 Components 3.7.6 Manufacturing (front-end) 3.7.7 Manufacturing (back-end) 3.7.8 Equipment & Tools (front-end) 3.7.9 Equipment & Tools (back-end)

#### 4 CONCLUSIONS

42

43

43

43

43

44

44

44

45

45 45

46

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|--------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                        | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                        |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                        |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                        |         | Georgios Fagas                                         |         |    |

# **Executive Summary**

The deliverable aims to evaluate the strengths and weaknesses of seven countries (Japan, South Korea, USA, Singapore, Taiwan, India, China) in the semiconductor value chain and propose recommendations for international research cooperation.

The first aim is to establish a comprehensive evaluation methodology by defining strengths/weaknesses and opportunities/challenges within the semiconductor value chain, ensuring all scenarios are non-overlapping and fully cover the ecosystem.

The second aim is a quantitative validation through expert surveys, providing insights into each country's positioning across defined axes. The analysis partitions the semiconductor field into categories like logic, memory, mixed-signal processing, and stages like chip design, manufacturing, and equipment tools.

Results of the analysis are recommendations and suggested topics for international research cooperation. These will be shared with international (EU and, most importantly, non-EU) experts, contributing to actionable insights for international research collaboration.

# **1** Overview

#### 1.1 Purpose

The purpose of this deliverable is to present the work done towards identifying strengths and weaknesses of each country under consideration (Japan, South Korea, USA, Singapore, Taiwan, India, China), by leveraging insights from previous studies, knowledge from the consortium and partner network, desk research, and brainstorming sessions, and therefore to propose corresponding recommendations for international research cooperation.

• The first objective is to establish the investigation and evaluation methodology/ framework: strengths/weaknesses and opportunities/challenges should be clearly defined with respect to a specific context/aspect, with the set of all the scenarios not overlapping and covering the entire semiconductor value chain and ecosystem. The main objective of this activity is to obtain a qualitative evaluation of the scenario.

• The second objective is to quantitatively assess the key points previously identified by asking and collecting information from international (non-EU and working in the countries of interest) experts in the field so as to have the needed feedback and validate the proposed recommendations. The work is based on a survey to be sent to the experts; the obtained results

| International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                |         | Georgios Fagas                                         |         |    |

will give the quantitative indication of the different strengths and weaknesses of each country of interest.

# 2 First Objective: Investigation and Evaluation Methodology/ Framework

#### 2.1 Proposed Approach

For the evaluation framework, two complementary perspectives have been taken into consideration:

- The *first one, "Across the value chain"*, has the aim of grouping all the possible applications (from the research, design, development, and fabrication point of view, not from a final end-user/consumer one), independently of which segment of the value chain is mostly involved.

- The *second one, "Through the value chain",* has the aim of partitioning the value chain into subsets of homogeneous related activities, major research fields, or major steps/processes in the overall semiconductor industry, independently of the intended target application of the final product.

It is very clear that, since the goal is to evaluate the strengths and weaknesses of a country, considering only one of those approaches would not be enough to give a clear picture of the scenario according to the scope of the overall project. Indeed, it is better to consider them as complementary or, better, as two (somehow orthogonal) axes (even if categorical and not necessarily ordered), along which quantitatively estimate strengths and weaknesses.

As a result, the proposal for the partitioning of the semiconductor field has been the following:

- Across the value chain:

- Logic

- Memory

- Mixed-signal processing

- Powering

- Sensing

- Communicating

- Photonics;

| ICCOP S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|-----------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                           | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                           |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                           |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                           |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                           |         | Georgios Fagas                                         |         |    |

- Through the value chain:

- EDA & IP

- Chip design

- System design

- Material integration

- Components

- Manufacturing (front-end)

- Manufacturing (back-end)

- Equipment & Tools (front-end)

- Equipment & Tools (back-end).

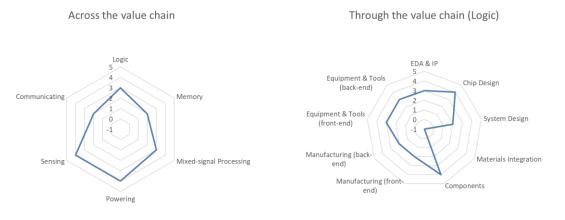

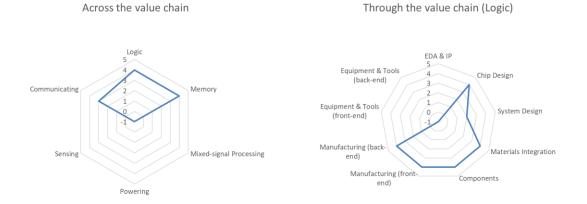

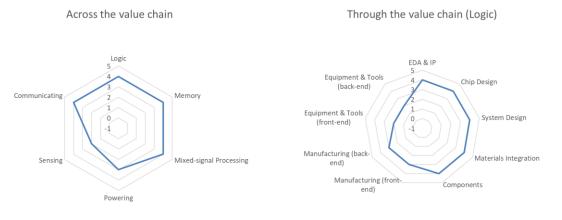

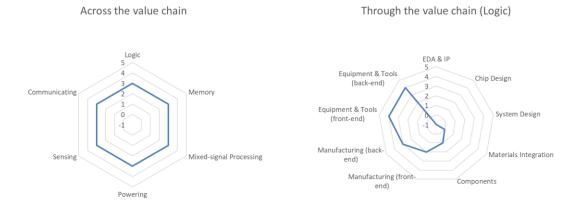

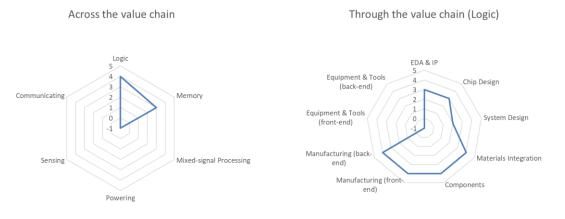

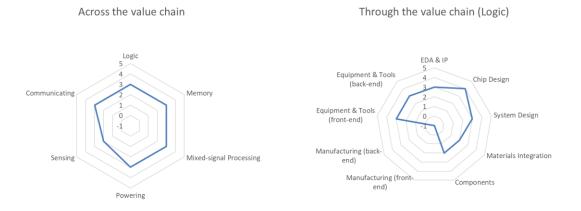

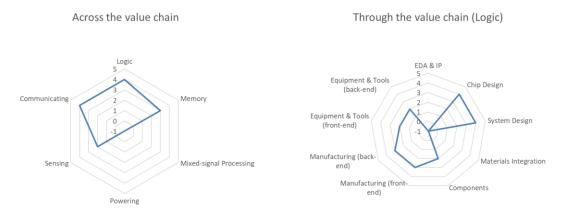

Concurrently, an interesting exercise done (not with the full set of applications) has been to estimate quantitatively, for each country, each point "indexed" by the two previously defined axes. In order to understand and validate the effectiveness of the proposed methodology itself, we preferred to focus on the industry ecosystem initially; therefore, we did not consider, at this stage, RTOs and universities (whose impact on the overall ecosystem is more complex to evaluate). We therefore collected, analysed and ordered (according to the proposed framework), for each country, a fairly representative set of actors in the semiconductor field, and then scored the overall impact of the country (given the target application and the value chain segment) with values between 1 (very weak) and 5 (very strong/leading position), and -1 indicating the possibility of not having yet enough information in the related case.

Very preliminary results have been thus obtained and synthesized as a pair of two spider maps (for providing a better visual idea as well, other than quantitative information) for each country (see Figures 1–7), presented and discussed with the other partners and experts in the field involved in the project.

The selected target countries are:

- Japan

- South Korea

- USA

- Singapore

- Taiwan

- India

- China

|                                                | Title   | Recommendations for International F | Research C | ooperation |

|------------------------------------------------|---------|-------------------------------------|------------|------------|

| International Cooperation<br>On Semiconductors | Authors | Paolo Motto Ros, Danilo Demarchi,   | Version    | 11         |

|                                                |         | Nadine Collaert, Markus Pfeffer,    |            |            |

|                                                |         | Gustavo Ardila, Alan O'Riordan,     |            |            |

|                                                |         | Wim Bogaerts, Roel Baets and        |            |            |

|                                                |         | Georgios Fagas                      |            |            |

Figure 1 Japan strengths and weaknesses in the semiconductor industry — preliminary analysis.

# South Korea

Figure 2 South Korea strengths and weaknesses in the semiconductor industry — preliminary analysis.

|                                                | Title   | Recommendations for International F | Research C | ooperation |

|------------------------------------------------|---------|-------------------------------------|------------|------------|

| International Cooperation<br>On Semiconductors | Authors | Paolo Motto Ros, Danilo Demarchi,   | Version    | 11         |

|                                                |         | Nadine Collaert, Markus Pfeffer,    |            |            |

|                                                |         | Gustavo Ardila, Alan O'Riordan,     |            |            |

|                                                |         | Wim Bogaerts, Roel Baets and        |            |            |

|                                                |         | Georgios Fagas                      |            |            |

Figure 3 USA strengths and weaknesses in the semiconductor industry - preliminary analysis.

Figure 4 Singapore strengths and weaknesses in the semiconductor industry - preliminary analysis.

|                                                | Title   | Recommendations for International F | Research C | ooperation |

|------------------------------------------------|---------|-------------------------------------|------------|------------|

| International Cooperation<br>On Semiconductors | Authors | Paolo Motto Ros, Danilo Demarchi,   | Version    | 11         |

|                                                |         | Nadine Collaert, Markus Pfeffer,    |            |            |

|                                                |         | Gustavo Ardila, Alan O'Riordan,     |            |            |

|                                                |         | Wim Bogaerts, Roel Baets and        |            |            |

|                                                |         | Georgios Fagas                      |            |            |

Figure 5 Taiwan strengths and weaknesses in the semiconductor industry - preliminary analysis.

Figure 6 India strengths and weaknesses in the semiconductor industry — preliminary analysis.

|                                                | Title   | Recommendations for International Research Cooperation |         |    |

|------------------------------------------------|---------|--------------------------------------------------------|---------|----|

| International Cooperation<br>On Semiconductors | Authors | , , , , , , , , , , , , , , , , , , , ,                | Version | 11 |

|                                                |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                |         | Georgios Fagas                                         |         |    |

Figure 7 China strengths and weaknesses in the semiconductor industry — preliminary analysis.

# **3** Second Objective: Quantitatively Assess the Key Points about the International Research Cooperation Topics

The further important activity carried out as a part of the Task 3.3 has been first to detail, to map the research cooperation topics on the proposed framework, and then to design a questionnaire for non-EU experts (at the country level). The final goal will be to collect evaluations, feedback, and comments on the strengths and weaknesses, across and through the semiconductor value chain (as previously recommended and proposed), of each of the target countries. To this end, for each research field, for each segment of the value chain, specific research cooperation challenges and opportunities have been identified and proposed, asking to the recipients to score them depending on the specific country strength on the matter; the opportunity to suggest further cooperation points has been made available as well. In two cases (Powering and Communicating) further specific aspects of, or closely related to, the semiconductor value chain, Energy Storage Devices (solid state thin film solutions) and Equipment & Tools for test/metrology, respectively, have been deemed fundamental and therefore added to the survey. The target audience of the survey has been selected based on available contacts inside the consortium and partner network, renowned leading experts in the fields, available lists of established experts with roles and responsibilities in the related scientific communities, all operating in, or with a solid knowledge and experience about, one or more target countries.

| International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                |         | Georgios Fagas                                         |         |    |

After brainstorming sessions, meetings, and revisions among the involved partners, the suggested international cooperation topics have been proposed and categorised in the following sections.

# 3.1 Logic

#### 3.1.1 EDA & IP

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the EDA & IP segment of the semiconductor value chain for the Logic research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Development of AI-enhanced EDA tools for optimizing logic designs across power, performance, area, cost and sustainability (PPACE).

- Tools for advanced node design enablement (e.g., 3 nm and beyond), addressing challenges like variability, aging, and lithography limitations.

- Techniques for RTL-to-GDSII automation in increasingly complex designs.

- High-quality, scalable IPs for standard cells, memory compilers, and other foundational components.

- IPs optimized for heterogeneous integration in multi-die and chiplet-based solutions.

- Development of secure logic IPs with built-in cryptographic and anti-tampering capabilities.

- EDA solutions for comprehensive design-for-testability strategies in logic designs.

- Simulation and formal verification tools for error-free complex logic circuits at extreme scales.

- Leveraging machine learning for adaptive synthesis and layout generation in complex logic chips.

- Al-driven tools for predictive failure analysis during logic design and manufacturing.

#### 3.1.2 Chip Design

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Chip Design segment of the semiconductor value chain for the Logic research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Design of general-purpose processors, AI accelerators, and GPUs with cutting-edge performance.

- Techniques for optimizing pipeline depth, clock speeds, and instruction-level parallelism in logic chips.

| ICCOS S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International F | Research C | ooperation |

|-----------------------------------------------------------|---------|-------------------------------------|------------|------------|

|                                                           | Authors | Paolo Motto Ros, Danilo Demarchi,   | Version    | 11         |

|                                                           |         | Nadine Collaert, Markus Pfeffer,    |            |            |

|                                                           |         | Gustavo Ardila, Alan O'Riordan,     |            |            |

|                                                           |         | Wim Bogaerts, Roel Baets and        |            |            |

|                                                           |         | Georgios Fagas                      |            |            |

- Development of ultra-low-power logic designs for mobile devices, IoT, and wearable applications.

- Techniques for dynamic voltage and frequency scaling and other power-saving mechanisms.

- Chip designs optimized for chiplet-based architectures, integrating logic with memory, analog, and other components.

- Architectures enabling co-packaged optics for high-bandwidth data transmission in logic-intensive applications.

- Logic designs featuring error correction codes and redundancy mechanisms for improved reliability.

- Designs focused on self-repairing logic circuits and real-time fault detection for missioncritical applications.

#### 3.1.3 System Design

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the System Design segment of the semiconductor value chain for the Logic research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- System-level designs for multi-core processors, optimized for scalability and parallelism in high-performance computing.

- Architectures for edge computing systems, requiring low latency and high energy efficiency.

- System designs incorporating AI-optimized processors, such as TPUs and NPUs.

- Architectures for AI at the edge, leveraging compact and efficient logic designs.

- System-level designs focusing on energy-efficient data centers and cloud computing environments.

- High-bandwidth logic subsystems optimized for interconnects in network-on-chip architectures.

- System-level solutions for trusted execution environments and secure boot mechanisms in logic-centric systems.

- Integration of logic encryption techniques to protect intellectual property and user data.

#### 3.1.4 Materials Integration

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Materials Integration segment of the semiconductor value chain for the Logic research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|--------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                        | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                        |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                        |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                        |         | Georgios Fagas                                         |         |    |

- Research into new materials for transistor scaling (e.g., 2D materials, nanosheet and CFET compatible materials).

- Research into novel high-k dielectrics and metal gates for further scaling logic transistors.

- Innovations in contact materials and dielectrics for low-power logic devices.

- Integration of materials for heterogeneous 2D/3D logic systems.

- Techniques for integrating logic layers in monolithic 3D architectures (e.g. CFET), addressing thermal and interconnect challenges.

- Materials enabling vertical integration of logic chips with minimal performance degradation.

- Advanced thermal interface materials for efficient heat dissipation in high-density logic architectures.

- Stress-resilient materials for mechanical stability during manufacturing and operation of logic chips at advanced nodes.

# 3.1.5 Components

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Components segment of the semiconductor value chain for the Logic research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Research and development of advanced transistor technologies such as FinFETs, nanosheets and CFET transistors for sub-3 nm nodes.

- Exploration of alternative materials for the channel (e.g. SiGe, 2D materials).

- Development of integrated passive components (e.g., capacitors, resistors, inductors) for System-on-Chip (SoC) and heterogeneous integration.

- R&D into passive components for power integrity and signal integrity in high-frequency and low-power logic circuits.

- Development of components enabling neuromorphic computing and quantum logic devices.

- R&D into materials and devices for beyond-CMOS technologies, including spintronics and carbon nanotubes.

#### 3.1.6 Manufacturing (front-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the front-end Manufacturing segment of the semiconductor value chain for the Logic research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

|                                                | Title   | Recommendations for International F | Recommendations for International Research Cooperation |    |  |

|------------------------------------------------|---------|-------------------------------------|--------------------------------------------------------|----|--|

| International Cooperation<br>On Semiconductors | Authors | Paolo Motto Ros, Danilo Demarchi,   | Version                                                | 11 |  |

|                                                |         | Nadine Collaert, Markus Pfeffer,    |                                                        |    |  |

|                                                |         | Gustavo Ardila, Alan O'Riordan,     |                                                        |    |  |

|                                                |         | Wim Bogaerts, Roel Baets and        |                                                        |    |  |

|                                                |         | Georgios Fagas                      |                                                        |    |  |

- Development of advanced lithography techniques (e.g., EUV and beyond) to achieve feature sizes for sub-3nm nodes.

- R&D into process optimization for reducing variability and managing layout-dependent effects in advanced nodes.

- Implementation of high-k/metal gate materials and low-resistance interconnects for next-generation logic devices.

- Exploration of new doping techniques and materials for ultra-thin channel layers.

- Manufacturing processes for stacked nanosheet and CFET transistors and other novel device geometries.

- Techniques for addressing power-density challenges in high-performance computing logic chips.

- Substrate thinning processes and back-side processing for new power and backside passive and active functionalization.

# 3.1.7 Manufacturing (back-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the back-end Manufacturing segment of the semiconductor value chain for the Logic research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Manufacturing techniques for low-resistance, high-reliability interconnects at sub-3 nm nodes (e.g., alloys, alternative conductors).

- R&D into air-gap dielectric technologies to reduce RC parasitics.

- Processes for integrating logic cores with accelerators and memory using chiplets and 2.5D/3D packaging.

- High-precision assembly techniques for heterogeneous system integration.

- Back-end processes for integrating advanced thermal management materials, such as TIMs (Thermal Interface Materials).

# 3.1.8 Equipment & Tools (front-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the front-end Equipment & Tools segment of the semiconductor value chain for the Logic research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Development of advanced lithography tools (e.g., EUV lithography) and metrology equipment for sub-3 nm nodes.

- Innovations in defect detection and critical dimension measurement tools to ensure high yields in logic chip production.

| ICCOS S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International F | Recommendations for International Research Cooperation |    |  |

|-----------------------------------------------------------|---------|-------------------------------------|--------------------------------------------------------|----|--|

|                                                           | Authors | Paolo Motto Ros, Danilo Demarchi,   | Version                                                | 11 |  |

|                                                           |         | Nadine Collaert, Markus Pfeffer,    |                                                        |    |  |

|                                                           |         | Gustavo Ardila, Alan O'Riordan,     |                                                        |    |  |

|                                                           |         | Wim Bogaerts, Roel Baets and        |                                                        |    |  |

|                                                           |         | Georgios Fagas                      |                                                        |    |  |

- Tools for electrical and thermal characterization of transistors at advanced nodes (e.g., FinFETs, nanosheets and CFET).

- Development of equipment for measuring variability in nanoscale devices and creating reliable early device models for design enablement.

- Equipment for deposition, etching, and doping processes for highermobility/alternative channel materials like SiGe and 2D materials.

- R&D into ALD and ALE tools for precise control of material layers in leading-edge process technologies.

# 3.1.9 Equipment & Tools (back-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the back-end Equipment & Tools segment of the semiconductor value chain for the Logic research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Tools for processing advanced materials, such as copper-alternative conductors and low-k dielectrics, to reduce interconnect resistance and capacitance.

- Development of high-precision equipment for TSV and micro-bump bonding in 3D integration of logic chips.

- Equipment for integrating logic cores with high-bandwidth memory or other accelerators in chiplet-based systems.

- R&D into advanced redistribution layer tools for improved signal and power integrity.

# 3.2 Memory

#### 3.2.1 EDA & IP

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the EDA & IP segment of the semiconductor value chain for the Memory research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Development of EDA tools for modelling and simulation of 3D NAND and DRAM architectures at extreme scaling.

- Tools to address variability, defect tolerance, and yield optimization for high-density memory arrays.

- Custom EDA solutions for emerging memory technologies (e.g., MRAM, RRAM, PCM), including reliability and performance modelling.

- Creation of standardized memory controller IPs for heterogeneous architectures.

- IP design for novel memory hierarchies in data-centric computing, including persistent memory IPs for in-memory computing.

| ICCOS S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International F | Recommendations for International Research Cooperation |    |  |

|-----------------------------------------------------------|---------|-------------------------------------|--------------------------------------------------------|----|--|

|                                                           | Authors | Paolo Motto Ros, Danilo Demarchi,   | Version                                                | 11 |  |

|                                                           |         | Nadine Collaert, Markus Pfeffer,    |                                                        |    |  |

|                                                           |         | Gustavo Ardila, Alan O'Riordan,     |                                                        |    |  |

|                                                           |         | Wim Bogaerts, Roel Baets and        |                                                        |    |  |

|                                                           |         | Georgios Fagas                      |                                                        |    |  |

- Design methodologies for secure memory architectures, focusing on encryption and anti-tampering.

- Incorporation of machine learning models into EDA tools for predictive yield analysis and optimization in memory manufacturing.

- AI-based solutions for automated layout generation and verification of advanced memory designs.

#### 3.2.2 Chip Design

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Chip Design segment of the semiconductor value chain for the Memory research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Design of high-speed and high-capacity DRAM and NAND chips for next-generation computing systems.

- Architectures for improving latency, bandwidth, and energy efficiency in traditional memory systems.

- Chip designs leveraging emerging memory types (e.g., FeRAM, MRAM, RRAM, PCM) for specific applications like AI accelerators and edge computing.

- Design of hybrid memory/storage chips, combining traditional and non-volatile memory technologies to reduce data movement.

- Development of logic-in-memory designs to enable compute capabilities within memory chips.

- Architectures for monolithic 3D integration of memory and logic to achieve ultra-highdensity and reduced latency.

- Memory chip designs with advanced error correction codes to improve reliability in scaled and stacked architectures.

- Circuit designs for mitigating soft errors, wear levelling, and endurance issues in emerging memory technologies.

#### 3.2.3 System Design

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the System Design segment of the semiconductor value chain for the Memory research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- System-level architectures for tiered memory hierarchies, combining DRAM, NAND, and emerging memory technologies.

- Designs for heterogeneous memory systems that optimize for workload-specific requirements (e.g., HPC, AI, IoT).

| ICCOS S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|-----------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                           | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                           |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                           |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                           |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                           |         | Georgios Fagas                                         |         |    |

- Development of system-level designs for in-memory computing architectures, enabling data processing directly within memory.

- Architectures for accelerating AI/ML workloads through memory-optimized system designs.

- System designs focusing on reducing power consumption in memory subsystems for edge and mobile devices.

- HBM integration into chiplet-based systems for HPC and cloud applications.

- System-level solutions for memory integrity verification and protection against data corruption and hacking.

- Integration of advanced secure memory technologies for critical applications like autonomous vehicles and defence.

#### 3.2.4 Materials Integration

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Materials Integration segment of the semiconductor value chain for the Memory research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Research into new dielectric materials for improving capacitor scaling in DRAM technologies.

- Materials for achieving better endurance and retention in NAND flash memory.

- Integration of ferroelectric materials for FeRAM and hafnium-based oxides for non-volatile memories.

- Spintronic materials (e.g., magnetic tunnel junctions) for MRAM and resistive switching materials for RRAM.

- Development of phase-change materials for PCM with improved switching speeds and endurance.

- Materials research for enabling BEOL-compatible materials in monolithic 3D memory stacking.

- Techniques for integrating memory layers with logic in ultra-dense chip architectures.

- Integration of materials with improved thermal stability to handle heat dissipation in stacked and hybrid memory architectures.

- Research into stress-resilient materials for minimizing mechanical degradation in 3D NAND and other stacked memory solutions.

# 3.2.5 Components

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Components segment of the semiconductor value chain for the Memory research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

| International Cooperation<br>On Semiconductors | Title   | Recommendations for International F | Recommendations for International Research Cooperation |    |  |

|------------------------------------------------|---------|-------------------------------------|--------------------------------------------------------|----|--|

|                                                | Authors | Paolo Motto Ros, Danilo Demarchi,   | Version                                                | 11 |  |

|                                                |         | Nadine Collaert, Markus Pfeffer,    |                                                        |    |  |

|                                                |         | Gustavo Ardila, Alan O'Riordan,     |                                                        |    |  |

|                                                |         | Wim Bogaerts, Roel Baets and        |                                                        |    |  |

|                                                |         | Georgios Fagas                      |                                                        |    |  |

- Research and development in DRAM and NAND technologies, focusing on scaling limits and improving energy efficiency.

- Exploration of high-density memory arrays and ultra-thin dielectric layers for advanced memory cells.

- Development of FeRAM, MRAM, and RRAM technologies for next-generation non-volatile memory.

- Exploration of phase-change memory and other storage-class memory solutions for hybrid memory/storage systems.

- Components for in-memory computing, including logic-in-memory approaches to reduce data movement and latency.

- R&D into hybrid memory technologies for monolithic 3D integration with logic.

# 3.2.6 Manufacturing (front-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the front-end Manufacturing segment of the semiconductor value chain for the Memory research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Techniques for manufacturing memory cells with ultra-high density and achieving vertical scaling in 3D NAND.

- Process development for scaling DRAM beyond traditional lithographic limits.

- Manufacturing techniques for integrating novel materials, such as ferroelectrics (FeRAM), spintronic materials (MRAM), and resistive materials (RRAM).

- Advanced deposition and etching methods for phase-change materials in PCM devices.

- Overcoming variability and defect challenges in extreme scaling of emerging memory technologies.

- R&D into uniformity and reliability improvements for wafer-scale memory production.

# 3.2.7 Manufacturing (back-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the back-end Manufacturing segment of the semiconductor value chain for the Memory research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Manufacturing processes for 3D NAND stacking and wafer-level bonding for DRAM and hybrid memory technologies.

- Integration of memory dies with logic chips in monolithic 3D architectures.

- Back-end processes for ultra-dense interconnects in memory modules (e.g., TSVs and micro-bump technologies).

- R&D into HBM interposer technologies.

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|--------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                        | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                        |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                        |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                        |         | Georgios Fagas                                         |         |    |

- Development of techniques for testing and mitigating failure mechanisms in stacked and hybrid memory architectures.

- Back-end processes for improving long-term reliability and minimizing thermal degradation.

### 3.2.8 Equipment & Tools (front-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the front-end Equipment & Tools segment of the semiconductor value chain for the Memory research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Development of EUV and multi-patterning tools for creating high-density memory arrays (e.g., NAND flash, DRAM).

- Tools for overcoming challenges in extreme scaling of memory cells (e.g., <10 nm features).

- Tools for precise deposition of materials used in ferroelectric FeRAM, MRAM, and RRAM.

- R&D into equipment for depositing and etching phase-change materials for non-volatile memory (e.g., PCM-based memory).

- Tools for evaluating read/write speeds, endurance, and retention of advanced memory devices under various operating conditions.

- Electrical characterization tools for studying variability in emerging memory types, such as MRAM and RRAM.

# 3.2.9 Equipment & Tools (back-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the back-end Equipment & Tools segment of the semiconductor value chain for the Memory research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Development of tools for high-precision wafer bonding and die stacking in 3D NAND flash and hybrid memory technologies.

- Equipment for integrating memory with logic in monolithic 3D architectures.

- R&D into tools for thermal management and reliability testing of stacked memory devices.

- Development of equipment for accelerated testing of memory endurance and failure mechanisms.

- Tools for creating high-density packaging solutions for HBM, including interposers and chiplets.

- Equipment for ultra-thin wafer handling and back-grinding to enable compact memory solutions.

| International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                |         | Georgios Fagas                                         |         |    |

### 3.3 Mixed-Signal Processing

#### 3.3.1 EDA & IP

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the EDA & IP segment of the semiconductor value chain for the Mixed-Signal Processing research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Research and development of early compact models for advanced/in-development nodes.

- Research and development of tools/libraries supporting the design of systems leveraging heterogeneous integration since the beginning of the design stages.

- Research and development of libraries and IPs of digitally-assisted analog circuits (e.g., with digital calibration), digital analog-like circuits (e.g., based on a standard cell design but with an analog behaviour).

- Research and development of advanced macro modelling techniques and tools leveraging data-driven/ML approaches for fast execution of comprehensive simulations of large/complex AMS designs.

- Research and development (including active support and promotion of new and emerging standard, open-source initiatives) of Hardware Description Languages (HDLs) and tools integrating different simulation approaches (e.g., event-driven and real-number simulators, numerical solvers) and targeting different levels of abstraction (e.g., behavioural, TLM- and RTL-like, transistor and/or physical levels).

#### 3.3.2 Chip Design

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Chip Design segment of the semiconductor value chain for the Mixed-Signal Processing research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Research and development of analog and mixed-signals circuits for leading edge process technologies.

- Research and development of digital wrapped or digitally-assisted analog circuits (e.g., with digital calibration), digital analog-like circuits (e.g., based on a standard cell design but with an analog behaviour).

- Research and development of low-power techniques targeting dynamic power management, for example leveraging dynamic voltage (or frequency) scaling, power gating.

- Research and development for Design for Testability (DfT) solutions for analog and mixed-signal ICs.

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|--------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                        | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                        |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                        |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                        |         | Georgios Fagas                                         |         |    |

#### 3.3.3 System Design

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the System Design segment of the semiconductor value chain for the Mixed-Signal Processing research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Research and development of structural solutions for mitigating and preventing, at the system level, issues regarding power integrity, signal integrity, and performance degradation, especially in large digital designs combined with analog and mixed-signals sub-systems.

- Research and development of solutions for advanced packaging, multi-die (chipletbased) solutions, and heterogeneous integration in general.

- Research and optimization in system-level optimization beyond PPAC (power, performance, area, cost), for example including R (robustness, reliability), T (temperature, thermal management), EDP (Energy-Delay product), Quality-energy trade-off.

- Research and development of constraints, requirements, and specifications bottomup/top-down propagation methodologies, aiming at addressing the mutual impact between specific AMS circuit low-level design issues in leading edge process technologies and high-level, large and resource intensive, advanced applications such as AI/ML and quantum models and systems.

- Research and development of structural approaches for an effective and efficient implementation and integration of Design for Testability (DfT) solutions at the system level, in particular seamlessly extending digital solutions with advanced AMS features.

#### 3.3.4 Materials Integration

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Materials Integration segment of the semiconductor value chain for the Mixed-Signal Processing research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Research and development beyond Si-based devices, exploiting new materials (e.g., nanowires, carbon nanotubes, graphene, 2d materials in general) properties and their engineering/integration with Si-based devices and circuits.

- Research and development of materials for BEOL-compatible monolithic 3D integration of active and passive components.

#### 3.3.5 Components

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Components segment of the semiconductor value chain

| International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                |         | Georgios Fagas                                         |         |    |

for the Mixed-Signal Processing research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Research and development of integrated passive devices on silicon substrate.

- Research and development of passive components for integration in advanced packaging and System-in-Package (SiP) solutions, multi-die (chiplet-based) solutions, heterogeneous integration in general.

#### 3.3.6 Manufacturing (front-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the front-end Manufacturing segment of the semiconductor value chain for the Mixed-Signal Processing research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

• Research and development of techniques for better control/reduction of layoutdependent effects in leading edge process technologies.

#### 3.3.7 Manufacturing (back-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the back-end Manufacturing segment of the semiconductor value chain for the Mixed-Signal Processing research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

• Research and development of techniques for better control/reduction of RC parasitics in leading edge process technologies.

#### 3.3.8 Equipment & Tools (front-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the front-end Equipment & Tools segment of the semiconductor value chain for the Mixed-Signal Processing research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

• Research and development of equipment & tools for electrical characterization, aiming at developing reliable early models of devices and parasitics in leading edge process technologies.

#### 3.3.9 Equipment & Tools (back-end)

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the back-end Equipment & Tools segment of the semiconductor value chain for the Mixed-Signal Processing research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

| IC S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International F | Recommendations for International Research Cooperation |    |  |

|--------------------------------------------------------|---------|-------------------------------------|--------------------------------------------------------|----|--|

|                                                        | Authors | Paolo Motto Ros, Danilo Demarchi,   | Version                                                | 11 |  |

|                                                        |         | Nadine Collaert, Markus Pfeffer,    |                                                        |    |  |

|                                                        |         | Gustavo Ardila, Alan O'Riordan,     |                                                        |    |  |

|                                                        |         | Wim Bogaerts, Roel Baets and        |                                                        |    |  |

|                                                        |         | Georgios Fagas                      |                                                        |    |  |

- Research and development of equipment & tools for electrical characterization, aiming at developing reliable early models of parasitics in leading edge process technologies.

- Research and development of equipment & tools for processing, and integrating in the BEOL processes, materials for BEOL-compatible monolithic 3D integration of components.

#### 3.4 Powering

#### 3.4.1 EDA & IP

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the EDA & IP segment of the semiconductor value chain for power devices and energy harvesting research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

- Research and development of tools and libraries that support the design of systems in the specific area of power devices and power harvesting, particularly aimed at improving:

- Simulation Accuracy: Developing accurate models to predict device behaviour under various conditions.

- Thermal Analysis: Creating tools for analysing heat dissipation and thermal management.

- Process Variation: Addressing variations in manufacturing processes to ensure reliability.

- Design Optimization: Implementing techniques to optimize layouts for performance and efficiency.

- Integration with CAD Tools: Ensuring compatibility with existing Computer-Aided Design (CAD) tools for seamless workflows.

- Design for Manufacturability (DFM): Making sure designs are practical and costeffective for manufacturing.

- Yield Prediction: Developing tools to predict and enhance yield rates in manufacturing.

- Reliability Analysis: Conducting assessments of long-term performance and reliability of devices.

#### 3.4.2 Chip Design

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the Chip Design segment of the semiconductor value chain for power devices and energy harvesting research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

| ICCOS S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|-----------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                           | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                           |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                           |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                           |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                           |         | Georgios Fagas                                         |         |    |

- Design Automation: Developing tools for automating repetitive design tasks to improve efficiency.

- Simulation and Verification: Creating accurate simulation tools to verify functionality and performance of designs.

- Physical Design Tools: Implementing tools for layout design, including place and route processes.

- Power Analysis: Tools for analysing power consumption and optimizing for energy efficiency.

- Timing Analysis: Ensuring tools can check for timing violations and optimize clock distribution.

- Manufacturing Process Integration: Compatibility with specific manufacturing processes and technologies.

- Design for Testability (DFT): Implementing techniques to facilitate testing and debugging of chips.

- Yield Management: Tools to predict and improve yield in manufacturing processes.

- Reliability and Aging Analysis: Assessing long-term reliability and performance degradation of chips.

- Research and development, considering the development of circuits for power management in energy harvesting applications, of:

- Strategies to reduce the overall device size and cost.

- Efficient power management architectures fully integrated in a single chip.

- Strategies to reduce the intrinsic power consumption.

- Solutions allowing the miniaturization of the system embedding micro-magnetic components or power converters.

- Strategies to reduce cold start and steady-state thresholds.

- Strategies for the management of heterogeneous and/or multiple input energy transducers.

- Integration of complex load management functions into the same silicon.

#### 3.4.3 System design

Suggested international cooperation topics, used as a reference for rating the overall strength of each target country, considering the System Design segment of the semiconductor value chain for power devices and energy harvesting research/application field, in particular regarding (but not limited to) the following challenges and opportunities:

• Architecture Modelling: Developing tools for modelling system architectures to evaluate performance and scalability.

| ICCOS S<br>International Cooperation<br>On Semiconductors | Title   | Recommendations for International Research Cooperation |         |    |

|-----------------------------------------------------------|---------|--------------------------------------------------------|---------|----|

|                                                           | Authors | Paolo Motto Ros, Danilo Demarchi,                      | Version | 11 |

|                                                           |         | Nadine Collaert, Markus Pfeffer,                       |         |    |

|                                                           |         | Gustavo Ardila, Alan O'Riordan,                        |         |    |

|                                                           |         | Wim Bogaerts, Roel Baets and                           |         |    |

|                                                           |         | Georgios Fagas                                         |         |    |

- Design Specification: Creating frameworks for defining system requirements and specifications clearly.

- Simulation and Prototyping: Implementing tools for simulating system behaviour and creating prototypes for testing.

- Interface Design: Ensuring tools support the design of user interfaces and system interactions.

- Integration and Interoperability: Tools for ensuring seamless integration of different system components and interoperability.

- Performance Analysis: Developing tools to assess system performance under various conditions and workloads.

- Security Analysis: Implementing techniques to evaluate and enhance the security of system designs.

- Reliability and Fault Tolerance: Tools for assessing system reliability and incorporating fault tolerance mechanisms.