## IC and System Design

PROFESSOR V. KAMAKOTI DIRECTOR, IIT MADRAS MEMBER, NSAB 09/10/2024

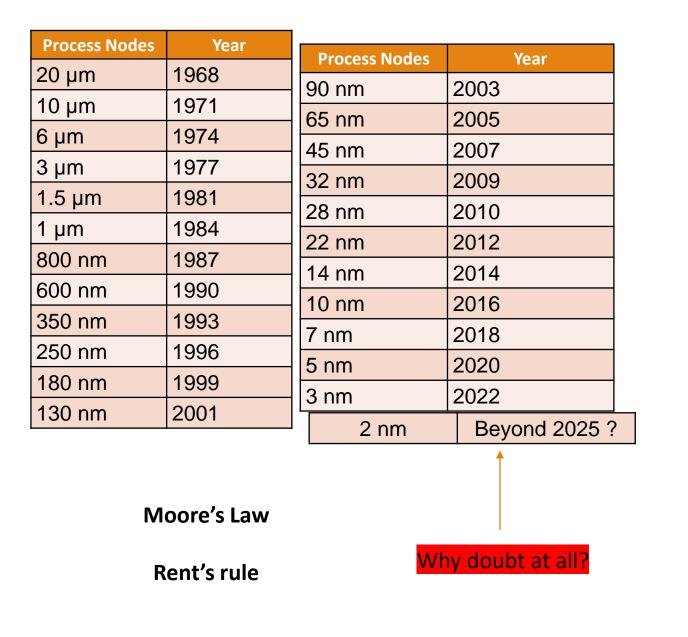

What does this table indicate to us?

#### MOSFET Scaling and Process Nodes over the years

#### **ICS are Typical Semiconductor devices**

- Processors,

- Microcontrollers,

- Memory Chips (NAND flash and DRAM)

# All most all ICS are typically CMOS Devices

#### What's EDA?

A Comprehensive Snap-Shot- Prelude

#### CMOS Based Mostly

Semi-Conductor Manufacturing

Metrology

ASIC, SOC, FPGA, CPLDs, Memories..

Electrical, Electronics, Mechanical, Computer Science, Industrial, Material Sciences, Chemicals ... Analog/Digital/Mixed Signal/RF High Speed/Power Aware/Low Power

Consumer Electronics, Automotive Aerospace Safety Critical

Medical, Industrial, Instrumentation, Power Systems

IOT, CPS, Edge Devices, Embedded Systems, Transducers

PCS, Servers, GPGPUS, HPC, FPGA Boards

Mobile, Telecom Networking, Satellite Communication, Positioning Systems

Software, Simulation, Emulation, Modeling, Verification, Validation, Testing

### Integrated Chips System Design

### An Indicative Landscape - Prelude

Newsroom Home | Newsroom Search | International Sites | Email Opt-in

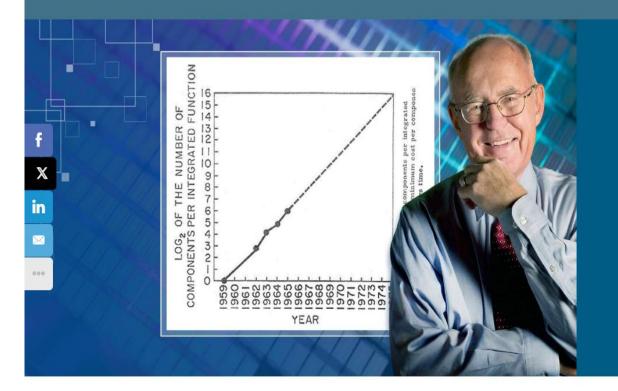

### Moore's Law

The past, present and future of Gordon Moore's golden rule for the semiconductor industry.

Ref : https://www.intel.com/content/www/us/en/newsroom/resources/moores-law.html#gs.fnxl6a

All Electronic Devices and ICs

ICS are typically Semiconductor Devices

### Prelude – Moore's Law ?

#### Rent's Rule Coincidence or the Result of the Design Process?

Dirk Stroobandt\*

University of Ghent, ELIS Department Sint-Pietersnieuwstraat 41 B-9000 Gent, Belgium dstr@elis.rug.ac.be

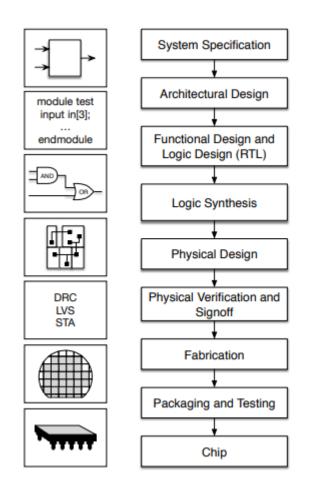

The design process for VLSI systems requires several iterations of the physical design cycle. After a partitioning of the circuit and a floorplanning step, the circuit components are placed. The wires between the components are then routed taking the placement into account. A bad placement cannot be solved by a good routing. Therefore, the information obtained during routing generally leads to a new placement step to improve the placement results. A new routing is then performed and so on.

In order to fasten the iteration process and to improve the placement and routing results, it is mandatory to efficiently use estimates of area, wire length, etc. Three kinds of estimates are used: a priori, on line, and a posteriori estimates [1, 2]. The first kind estimates circuit parameters before any of the layout steps (floorplanning, placement, or routing) is performed. On line estimates are obtained during the layout process and are based on the information that results from the layout process itself. A posteriori estimates are obtained after a complete layout step and present the layout results.

A priori estimates need basic information on the circuit to be designed, on the architecture in which it is to be designed, and on the layout process that performs the implementation of the circuit into the architecture [3, 4]. In this position statement, we consider the circuit information.

Apart from the number of gates (or blocks) in the circuit, its number of in- and outputs, its number of nets and number of pins, the most important information is the notion of interconnection complexity of the circuits netlist.

The interconnection complexity information is provided by Rent's rule [5]

$P = T_b B^r$

where B is the number of gates (blocks) in the circuit, P is the number of pins, and  $T_b$  is the average number of terminals per gate (block). The exponent r is called the Rent exponent and is a measure for the interconnection complexity of the circuit. The problem is: "can we rely on the Rent exponent to make a priori estimations?" To answer this question, we have to ask ourselves some related questions:

Ref : https://citeseerx.ist.psu.edu/document?repid=rep1&type=pdf&doi=3c51d041b2cefe4b5ae7df7ec1ec6ade93bb6b05

This relates to the number of I/Os required for a block containing a given number of computing elements

Prelude – Rent's Rule – Does it Matter at all?

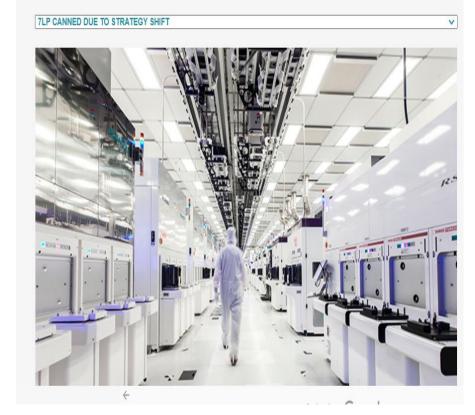

#### GlobalFoundries Stops All 7nm Development: Opts To Focus on Specialized Processes

by Anton Shilov & Ian Cutress on August 27, 2018 4:01 PM EST

Posted in Semiconductors CPUs AMD GlobalFoundries 7nm 7LP

For most of our lives, the idea that computers and technology would get better, faster, and cheaper every year was as assured as the sun rising every morning. The story "GlobalFoundries Halts 7-nm Chip Development," in *IEEE Spectrum*, doesn't sound like the end of that era, but for you and anyone who uses an electronic device, it most certainly is.

Technology innovation is going to take a different direction.

<u>GlobalFoundries</u> was one of the three companies that made the most advanced silicon chips for other companies, such as <u>AMD</u>, IBM, Broadcom, Qualcomm, STM and the Department of Defense.) The other <u>foundries</u> are <u>Samsung</u> in South Korea and <u>TSMC</u> in Taiwan. Now there are only two pursuing the leading edge. (Intel too is pursuing these advanced chips, but its business making chips for other companies is relatively small.)

This is a big deal.

Ref https://www.anandtech.com/show/13277/globalfoundries-stops-all-7nm-development

Ref <u>https://spectrum.ieee.org/what-globalfoundries-retreat-really-means</u>

Settling Down  $\rightarrow$  No more Semi-Conductor Shrinking [or what] ??

|                  | System-Level Electronics Design                           |

|------------------|-----------------------------------------------------------|

|                  | Chip-Level Electronics Design                             |

|                  | Embedded Design                                           |

| $\triangleright$ | System Modelling                                          |

| $\triangleright$ | Std Cell Libraries                                        |

| $\succ$          | I.S.A design [Open-Source vs Proprietary]                 |

| ≻                | I/O and Peripherals [Opensource vs Proprietary]           |

| ≻                | SOC inter and Intra connects [Open-Source vs Proprietary] |

| ≻                | Packaging                                                 |

|                  | Reliability and Quality                                   |

| $\triangleright$ | Timing                                                    |

|                  | Functionality                                             |

|                  | Synthesis                                                 |

|                  | Verification and Validation                               |

|                  | Yield Analysis                                            |

|                  | Simulation and Emulation, Modelling                       |

| $\triangleright$ | Power Electronics                                         |

|                  | PCB Designing                                             |

|                  | RF, Analog, Mixed Signal Modelling, Simulations           |

| $\succ$          |                                                           |

### Enter EDA

### There are 1000s of books and articles written, lectures delivered

#### The EDA Landscape

### Definition

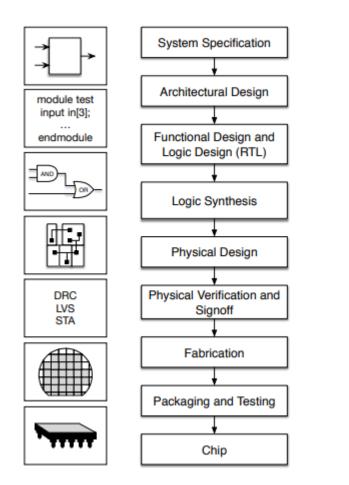

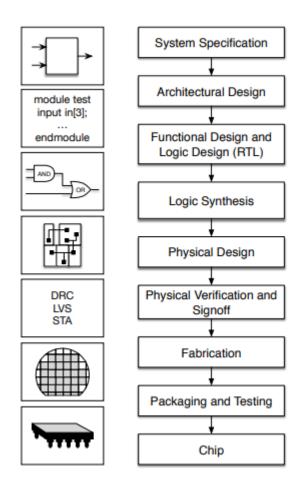

Electronic Design Automation, or EDA, is a market segment consisting of software, hardware, and services with the collective goal of assisting in the definition, planning, design, implementation, verification, and subsequent manufacturing of semiconductor devices, or chips. Regarding the manufacturing of these devices, the primary providers of this service are semiconductor foundries, or fabs. These highly complex and costly facilities are either owned and operated by large, vertically integrated semiconductor companies or operated as independent, "pure-play" manufacturing service providers. This latter category has become the dominate business model.

### Why is EDA Important?

Semiconductor chips are incredibly complex. State-of-the-art devices can contain over one billion circuit elements. All of these elements can interact with each other in subtle ways, and variation in the manufacturing process can introduce more subtle interactions and changes in behavior.

There is simply no way to manage this level of complexity without sophisticated automation, and EDA provides this critical technology. Without it, it would be impossible to design and manufacture today's semiconductor devices.

It is also worth noting that the cost of an error in a manufactured chip can be catastrophic. Chips errors cannot be "patched." The entire chip must be re-designed and re-manufactured. The time and cost of this process is often too long and too expensive, resulting in a failure of the entire project. So, the complexity to design chips is high and the need to do it flawlessly is also required.

Without EDA tools, these challenges cannot be met.

Ref: <u>https://www.synopsys.com/glossary/what-is-electronic-design-automation.html</u>

What does EDA mean to A Theoretical Computer Scientist

IC designs are NP-hard.

- The complexity of Integrated Circuits (IC) has increased exponentially, posing challenges to circuit design's scalability and reliability.

- EDA algorithms and software must be more effective and efficient to handle a large search space with low runtime.

- Many problems in EDA, are placement and wiring or scheduling.

- Simulation, Emulation, and Modeling are Complex and Resource Intensive

Without EDA, Moore's law would have remained applicable to ONLY satisfy curiosity.

The world wouldn't have had a single billion- -million or even a 1000s transistor chip.

Without EDA, systems could not have been designed, modelled, simulated, debugged, or tested.

Modern Day Computer-Aided Design Tools aids all System Design

EDA and IC and System Design

### Enter ML Methods

| Optimization Idea                | Task                        | ML Algorithm          |

|----------------------------------|-----------------------------|-----------------------|

|                                  |                             | Statistical Model     |

|                                  | Digital Design              | Search Methods        |

|                                  |                             | Rule Learning         |

|                                  |                             | CNN, SVM, et al.      |

| Test Set Redundancy<br>Reduction |                             | GCN                   |

| Reduction                        | Analog/RF Design            | KNN, ONN              |

|                                  |                             | Regression            |

|                                  | Semiconductor<br>Technology | CNN                   |

|                                  | Digital Design              | SVM, MLP, CNN, et al. |

| Test Complexity<br>Reduction     | Analog/RF Design            | ONN                   |

|                                  |                             | Active Learning       |

#### Ref : <u>https://arxiv.org/pdf/2102.03357</u>

### We Do have solutions..

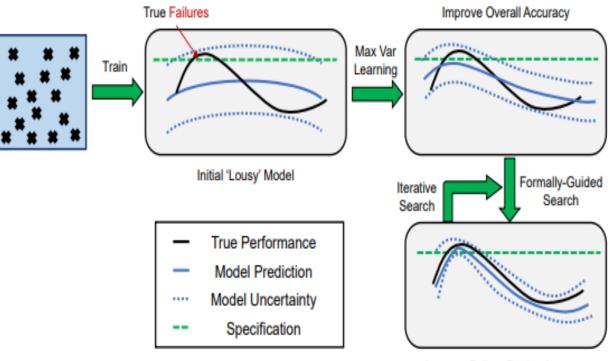

Improve Failure Region Accuracy

Ref : <u>https://arxiv.org/pdf/2102.03357</u>

We Do have solutions – Enter ML Methods

| ML Functionality                          | Task / Design Stage                                                                                                 | ML Algorithm                                                                  | Input                                                                                                           | Output                                                                               |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Decision making in<br>traditional methods | HLS Design space explo-<br>ration                                                                                   | Decision Tree, qua-<br>dratic regression,<br>etc.                             | Hardware direc-<br>tives (pragmas) in<br>HLS design                                                             | Quality of hyper-<br>parameters, e.g.,<br>initial state, termi-<br>nation conditions |

|                                           | Logic synthesis                                                                                                     | DNN                                                                           | RTL descriptions                                                                                                | Choice of the work-<br>flow and optimizer                                            |

|                                           | Mask synthesis                                                                                                      | CNN                                                                           | Layout images                                                                                                   | Choice of optimiza-<br>tion methods                                                  |

|                                           | Analog topology design                                                                                              | CNN, Fuzzy logic,<br>etc.                                                     | Analog specifica-<br>tions                                                                                      | Best topology selec-<br>tion                                                         |

| Performance<br>prediction                 | HLS                                                                                                                 | Linear Regression,<br>SVM, Random<br>Forest, XGBoost,<br>etc.                 | HLS Report, work-<br>load characteristics,<br>hardware character-<br>istics                                     | Resource usage, tim-<br>ing, etc.                                                    |

|                                           | Placement and routing                                                                                               | SVM, CNN, GAN,<br>MARS, Random For-<br>est etc.                               | Features from<br>netlist or layout<br>image                                                                     | Wire-length, rout-<br>ing congestion,<br>etc.                                        |

|                                           | Physical implementation<br>(lithography hotspot de-<br>tection, IR drop predic-<br>tion, power estimation,<br>etc.) | SVM, CNN, XG-<br>Boost, GAN, etc.                                             | RTL and gate-<br>level descriptions,<br>technology li-<br>braries, physical<br>implementation<br>configurations | Existence of lithog-<br>raphy hotspots, IR<br>drop, path delay<br>variation, etc     |

|                                           | Verification                                                                                                        | KNN, Ontogenic<br>Neural Network<br>(ONN), GCN, rule<br>learning, SVM,<br>CNN | Subset of test<br>specifications or<br>low-cost specifica-<br>tions                                             | boolean pass/fail<br>prediction                                                      |

|                                           | Device sizing                                                                                                       | ANN                                                                           | Device parameter                                                                                                | Possibility of con-<br>straint satisfaction                                          |

#### Ref : <u>https://arxiv.org/pdf/2102.03357</u>

We Do have solutions – Enter ML Methods

Could we do Analog/RF testing/Physical design, with their performance tied

to machine learning models or an ML and Classical Methods ensemble?

How would this meet the industrial needs?

How to trust ML methods?

Do we have enough trust in classical EDA?

#### Night Marish? Or Exciting Opportunities?

EDA for QComp

**QComp for EDA**

• Limitations of Semi-Conductor Process Nodes?

• FIN FET and Tunneling effect and other Quantum Effects

• Which QUBIT Manufacturing for Utility QComps?

We Do have solutions – ML Methods – But Is That All?

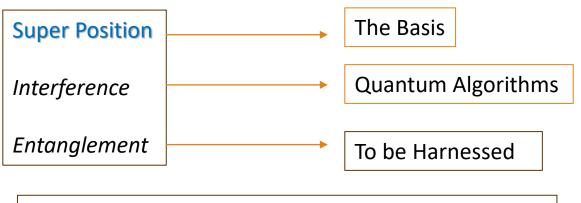

### Enter Quantum

### Computing

Information is processed based on Binary Logic - BITS

Logic elements that operate with N distinct states

Computational Power is based on the number of distinct states.

Based on Binary States

Algorithms

Parallel Operations

CMOS Based Transistors

Information processed] – based on Logical of Quantum Mechanics - QUBIT

Logic elements that operate with N states with different probability amplitudes simultaneously

Computational Power is based on a linear combination of probability amplitude states.

Super Conducting, Cold atoms, NV Centre, Photons..

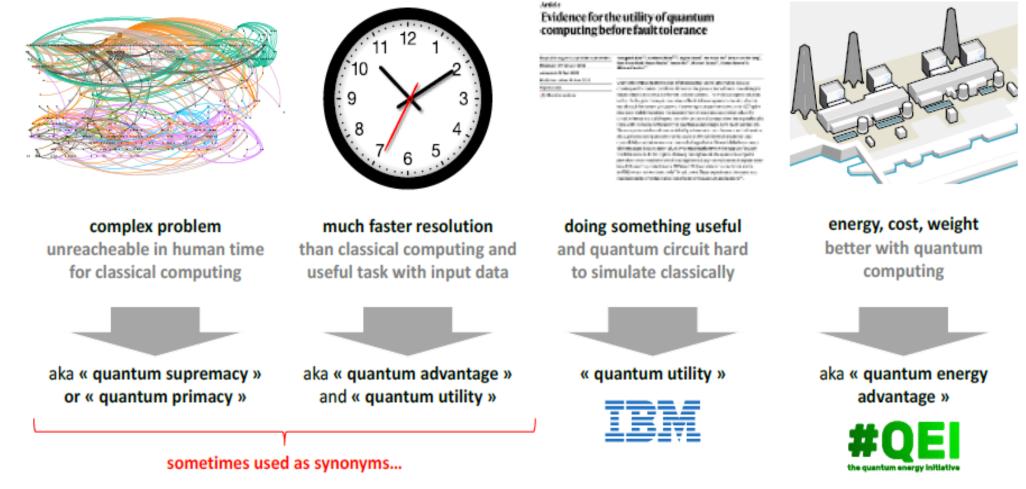

Figure 788: trying to define quantum supremacy (or primacy) and quantum advantage. (cc) Olivier Ezratty, 2022-2024.

- From the viewpoint of a C.S and a Policy advocate, I believe

- Utility of a QCOMP comes when we can't solve a classical problem with HP

- When we have an industry-compatible manufacturing process for QUBIT Implementation

- When the Energy, Power, and Operating Cost of QComp is better than the present HPCs

- When QCOMPS are "Trustable"

- Till then?

- Accelerate adoption of ML / Data Sciences methods in EDA and SemiCon Processes

- ✤ As strong cases of utility QCOMP dawn, integrate ML and QCOMP

- That time may not be far away though

# Any Questions?

17