EU – India Joint Researchers Workshop on Semiconductors

▶ 9 October 2024

# Heterogenous Integration – Enabling systems beyond Moore's Law

Dr.-Ing. Andreas Middendorf Strategic Business Development Fraunhofer IZM, Berlin

Brussels, Belgium October 9th 2024 EU – INDIA - Joint Researchers Workshop on Semiconductors

### **Fraunhofer IZM - Crossing Frontiers in Microelectronics** Three facts about our institute

We are one of the world's leading institutes for applied research as well as the development and system integration of robust and reliable electronics.

We have over 30 years of experience with novel technological solutions developed in collaboration with partners from industry and academia.

We are the only fully integrated packaging institute covering everything from design, technology, reliability, and eco assessments.

10 October 2024 © Fraunhofer IZM

Page 2

2

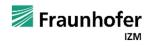

# **Fraunhofer IZM at a Glance** 30 years of experience

Page 5 10 October © Fraunhofer IZM

## **Fraunhofer IZM** A selection of our clients and partners

Fraunhofer

Page 4

© Fraunhofer IZM

10 October

2024

## The Fraunhofer-Gesellschaft

## **Research Fab Microelectronics Germany (FMD)**

10.10.2024 Page 5

© Fraunhofer IZM

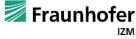

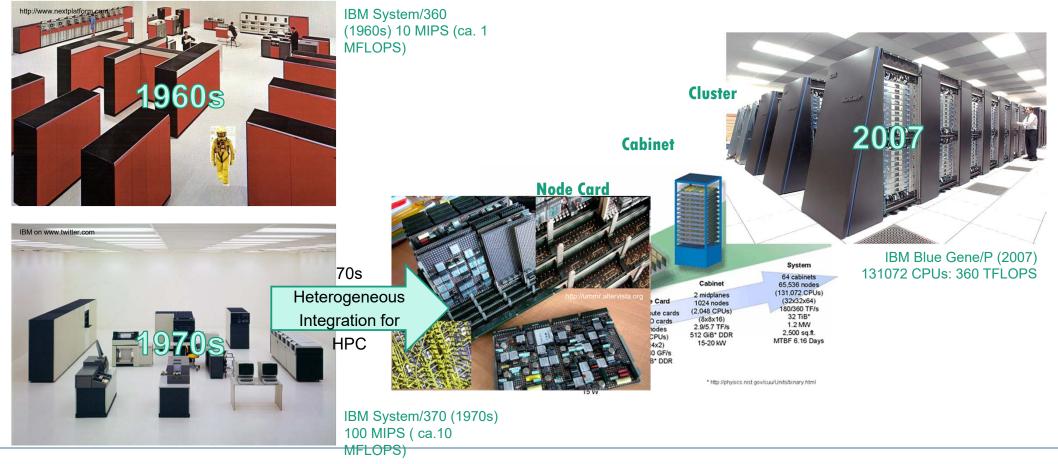

## **High Performance Computing Cluster**

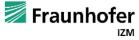

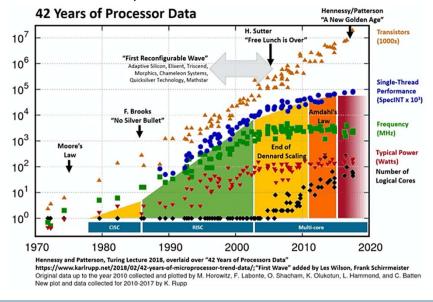

Some Historical Facts...

Page 7 10/10/2024 © Fraunhofer IZM

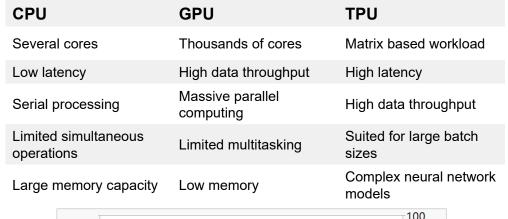

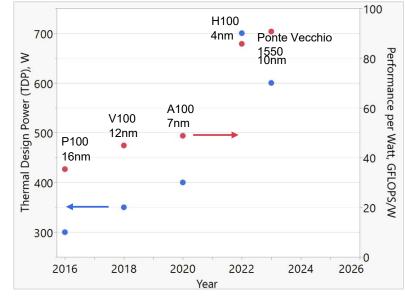

## **High Performance Computing** Drivers and Challenges

**MEMORY WALL:** Microprocessor speed increased faster than memory speed

**POWER WALL:** End of Dennard Scaling (= as transistors get smaller, their power density stays constant, < 65nm)

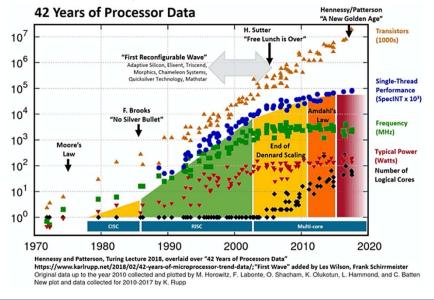

Training compute (FLOPs) of milestone Machine Learning systems over time

AlexNet: Convolutional neural network (CNN) used for image recognition AlphaGo: 1st computer program to defeat a human Go player

Page 8 10/10/2024 © Fraunhofer IZM

## **High Performance Computing** Drivers and Challenges

**MEMORY WALL:** Microprocessor speed increased faster than memory speed

**POWER WALL:** End of Dennard Scaling (= as transistors get smaller, their power density stays constant, < 65nm)

Page 9 10/10/2024 © Fraunhofer IZM

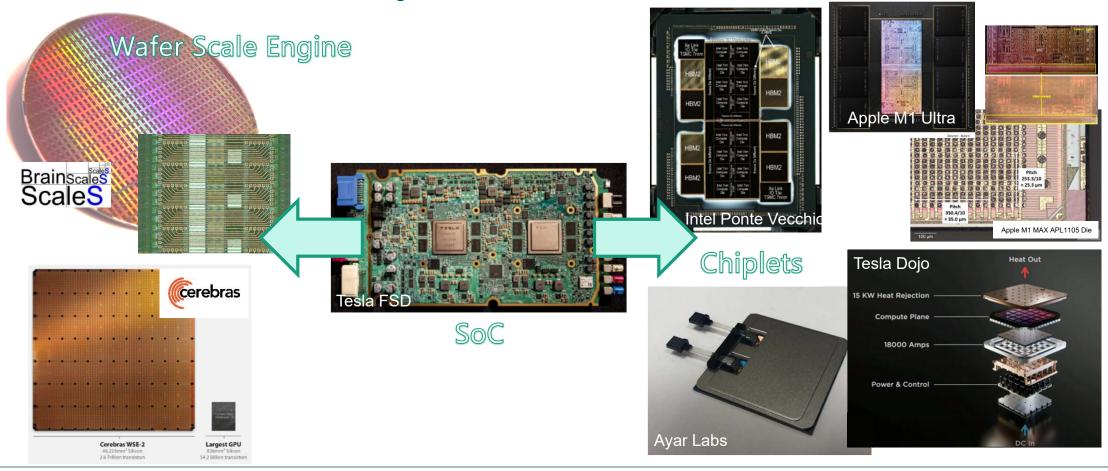

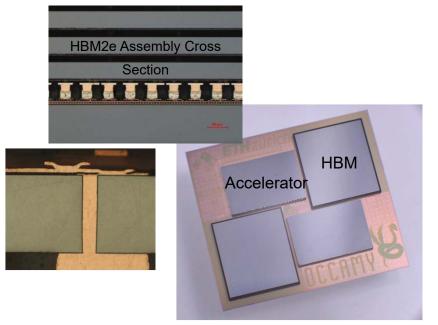

## **Demanding High-End Performance Packaging**

SoC vs. Chiplet vs. Wafer Scale Engine

Page 10 10/10/2024 © Fraunhofer IZM

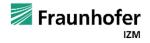

## **Technology Overview and Manufacturers**

High-End Performance Packaging

## **Advanced Packaging for High-Performance Computing** Major Technology Challenges for Chiplets Systems

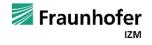

131072/mm2 **High-end Performance Packaging** areal density Heterogeneous Integration placement 65536/mm2 [bumps/mm<sup>2</sup>] accuracy Hybrid Bonding: Next-Architectures 32768/mm2 Gen 107 16384/mm2 50n@3o 3D-SOC 8192/mm2 106 100n@30 mm2) Hybrid Bonding: 3D-Image 4096/mm2 Flip-Chip: ubumps/Cu Bumpless Sensors Pillars 3D-SIC 2048/mm2 Density\* (I/O per Log Scale DIELETS (Inorganic RDL) Embedded Si bridge: 105 1024/mm2 µbumps CHIPS 0.5µ@3σ Fan-Out (HD FO) 512/mm2 Flip-Chip: µbumps/Cu 1µ@3σ 104 256/mm2 Pillars Flip-Chip: µbumps/Cu EMIB 2.5D HBM Pillars 128/mm2 SLIM Flip Chip: Bump CoWos 0/ 64/mm2 InFO, FOCoS 10<sup>3</sup> 2.5D Si Interposer SWIFT Organic RDL 4µ@30 32/mm2 16/mm2 RCP Fan-Out (Core) Fan-In Fan-Out (UHD FO) 10<sup>2</sup> 2D 10µ@3σ eWLB 8/mm2 FC-BGA 4/mm2 IC Substrate: BGA Balls 101 2/mm2 IC Substrate: BGA Balls Flip Chip: QFN 40 100 µm 0.2 0.5 1 5 10 1/mm2 🖕 1024,0µm 512,0µm 256,0µm 128,0µm 64,0µm 32,0µm 16,0µm 4.0µm 2.0µm 1,0µm 0.5µm bump pitch [µm] 8,0µm IO Pitch (µm) 6 https://www.ectc.net/files/68/Behler%20Besi.pdf YOLE Log Scale Integration of components Smaller and smaller combined to a system dimensions on a single wafer 💹 Fraunhofer

IO Density vs. IO Pitch for Advanced Packaging (Log Scale)

10/10/2024 © Fraunhofer IZM Page 12

Page 14 © Fraunhofer IZM

10/10/2024

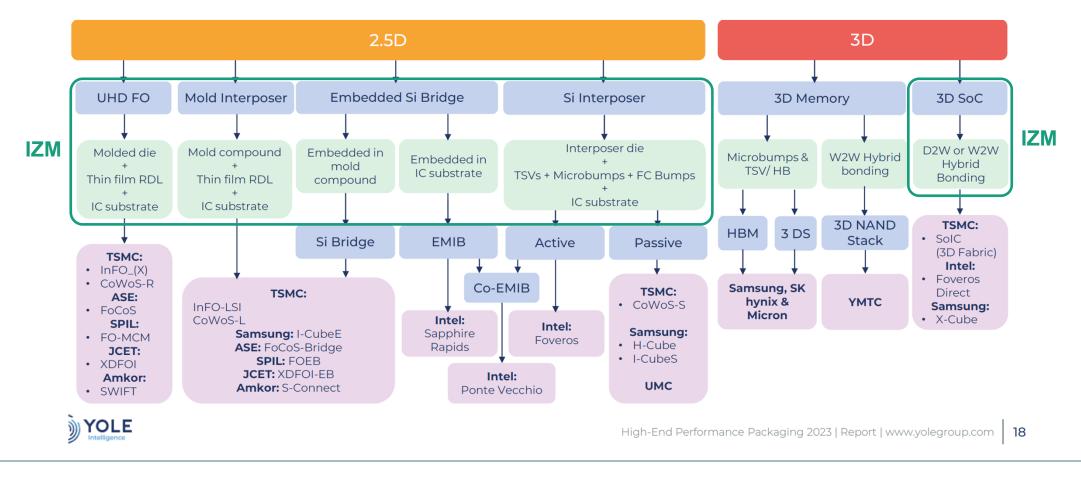

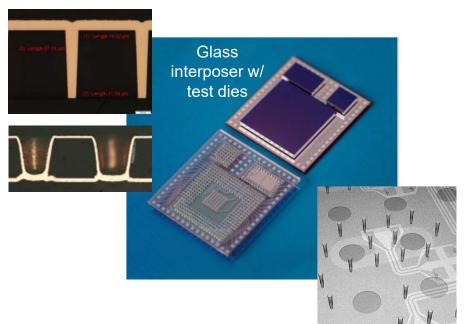

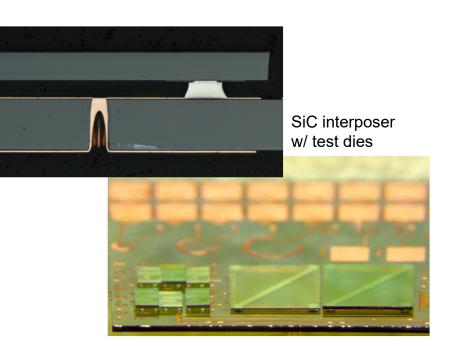

## **Interposers** Silicon, Glass and Silicon Carbide

- Si-interposers w/ polymer based RDL and TSV → established technology, approved by industry

- BEOL Si-interposers back side finishing → established technology, approved by industry

- Glass interposers → technology path explored, various TGV and cavity options, interest from industry

- SiC interposers → technology setup is done but why SiC?

High thermal conductivity (>350 W/mK, on par with Cu!), high

Young's modulus (>370 GPa), dielectric contant (6.5-10)

Chip / System Design: ETH Zürich Interposer Finish / Assembly: Fraunhofer IZM

## **Interposers** Silicon, Glass and Silicon Carbide

- Si-interposers w/ polymer based RDL and TSV → established technology, approved by industry

- BEOL Si-interposers back side finishing → established technology, approved by industry

- Glass interposers → technology path explored, various TGV and cavity options, interest from industry

- SiC interposers → technology setup is done but why SiC?

High thermal conductivity (>350 W/mK, on par with Cu!), high

Young's modulus (>370 GPa), dielectric contant (6.5-10)

## **Interposers** Silicon, Glass and Silicon Carbide

- Si-interposers w/ polymer based RDL and TSV → established technology, approved by industry

- BEOL Si-interposers back side finishing → established technology, approved by industry

- Glass interposers → technology path explored, various TGV and cavity options, interest from industry

- SiC interposers → technology setup is done but why SiC?

High thermal conductivity (>350 W/mK, on par with Cu!), high

Young's modulus (>370 GPa), dielectric constant (6.5-10)

Top contact

500 nm

15 um

Bottom conta

Si filling

Substrate

A cooperation of 📓 Fraunhofer

MIKROELEKTRONIK

MFM

2 µm

FBI

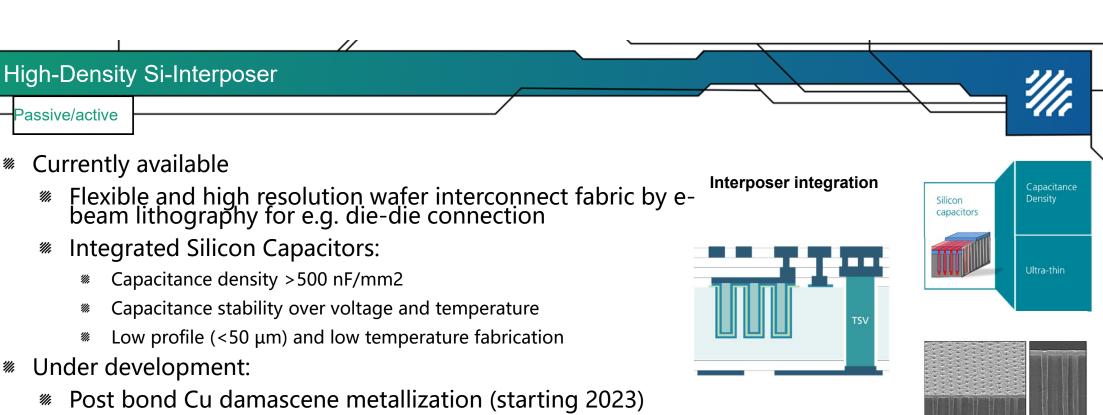

- Security key integration through embedded NVM (starting 2024)

- <u>Coils and ferromagnetic materials for voltage regulators</u> (2025)

Passive/active

‴//

Page 18

10/10/202

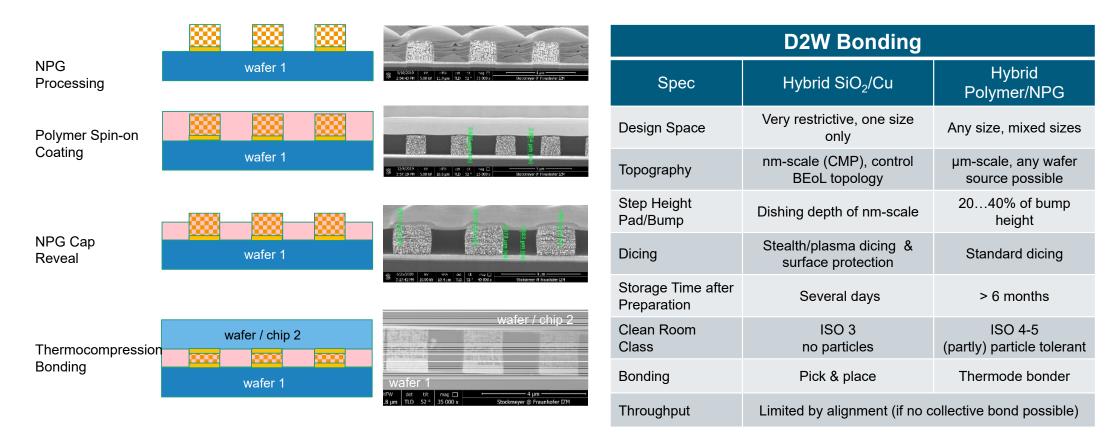

- W2W bonding with focus shift to (self-assembled) D2W bonding

- Massive parallel transfer bonding for chiplet integration

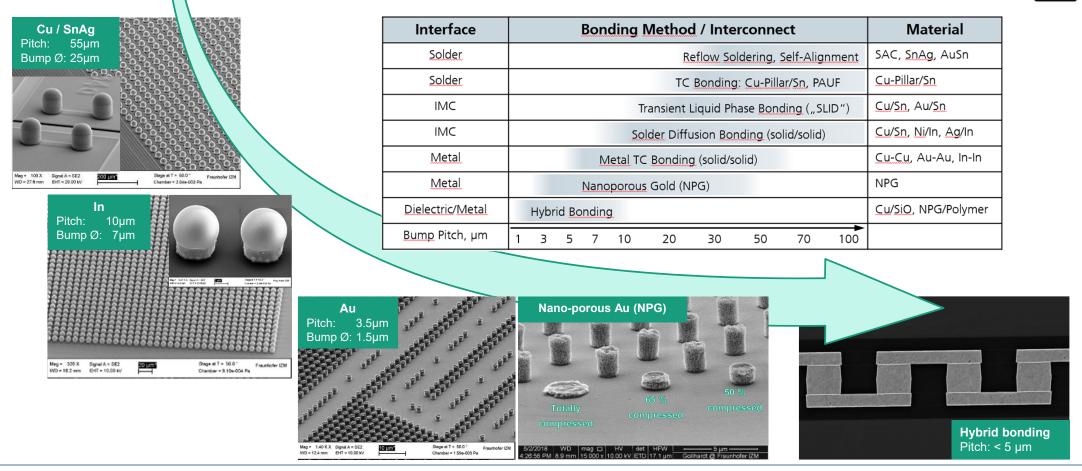

## **Pitch / Material Progression to Ultra-Fine Pitch** Bumping and Assembly Technology

Page 19 10/10/2024 © Fraunhofer IZM

## Spotlight: Assembly Progress to Ultra-Fine Pitch

Polymer Hybrid Bonding Technology

Technology

Building 0000

Blocks

Page 20 10/10/2024 © Fraunhofer IZM

## Chiplets

# Cramming more components onto integrated circuits

With unit cost falling as the number of components per circuit rises, by 1975 economics may dictate squeezing as many as 65,000 components on a single silicon chip

By Gordon E. Moore Director, Research and Development Laboratories, Fairchild Semiconductor division of Fairchild Camera and Instrument Corp. 19th April1965

[...] It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically. [...]

Gordon E. Moore, 1965

Fraunhofer

Page 22 10/10/202 <sup>©</sup> Fraunhofer IZM 4

## **Chiplet-Technology** Definition

# A chiplet is an integrated circuit block specifically designed to work with other chiplets to form a larger more complex system that often makes use of reusable IP blocks

- A chiplet can be created by partitioning a die into functions that are more cost effectively fabricated (smaller die, higher yield, and less advanced nodes)

- A chiplet is a hard IP block

- Functions with other chiplets, so design must be co-optimized and silicon cannot be designed isolated

- Made possible by communication using chiplet interface (proprietary today)

#### Differs from SiP or MCM $\rightarrow$ New system design, not just a combination of different "off-the-shelf" chips

#### Chiplet is not the package, it's the design philosophy

- Change from "silicon centric thinking" to "system-level planning" and "co-design of IC and package"

- The industry has to think about chip design in a new way

- Same impact as when the industry moved from a peripheral chip layout to area array!

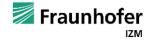

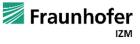

## **Chiplet-Technology** Motivation

#### Moore's Law and ist classic node scalability has no economic advantages anymore:

- High design cost and equipment invest f

ür next node generation (significantly caused by lithography)

- High production cost vs. Yield (Samsung has 60 % and TSMC at ca. 55% yield at 3 nm, according to KMIB News, 07/2023)

Phil Garrou, 2018 (7nm)

Page 24 10/10/2024 © Fraunhofer IZM

## **Chiplet-Technology** Motivation

#### Moore's Law and ist classic node scalability has no economic advantages anymore:

- High design cost and equipment invest f

ür next node generation (significantly caused by lithography)

- High production cost vs. Yield (Samsung has 60 % and TSMC at ca. 55% yield at 3 nm, according to KMIB News, 07/2023)

## **Chiplet-Technology** Motivation

#### Moore's Law and ist classic node scalability has no economic advantages anymore:

- High design cost and equipment invest f

ür next node generation (significantly caused by lithography)

- High production cost vs. Yield (Samsung has 60 % and TSMC at ca. 55% yield at 3 nm, according to KMIB News, 07/2023)

#### Heterogeneous integration offers an economic turning point:

- 2.5D / 3D integration

- Embedded bridge

- Chiplet-disaggregation

- HD Fan-Out

- ...

#### Challenges and at the same time the requirements would be:

- System Technology Co-Optimization (STCO) on system level is essential, combination of different materials, parts of classic assembly (D2W) probably are integrated in the fab processing

- Union of the triumphirate of design / fabrication / test

Design

Page 26 10/10/2024 © Fraunhofer IZM

### Wafer-and Panel-Level Hetero-Integration

Merging of Wafer- and PCB Technologies

#### Fraunhofer – Heterogeneous Integration From Wafer Level System Integration to Panel Level System Integration

5 nm ... >100 nm

0.75 μm ... >10 μm

## < 5 µm ... 100 µm

#### Wafer Level Packaging (WLP) Panel Level Packaging (PLP)

Technology: Based on thin film materials & equipment Wafer size: 100 mm ... up to 300 mm Input: CMOS - III/V - WBG wafers Output: 2.5D/3D integrated systems or system components

Technology: Based on PCB materials & equipment **Panel size:** up to  $610 \times 456 \text{ mm}^2$ Input: CMOS / III/V / wide bandgap dies (w/ bumping) **Output:** Packaged/embedded modules

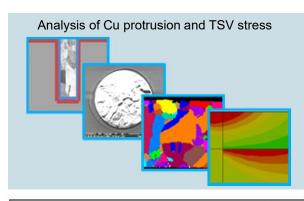

## Design for Reliability

Reliability Challenges for Heterointegration

- Process and Material Level

- Hybrid bonding/TSV: contact integrity, bonding strength, cyclic protrusion

- Smaller size & pitch (µm...sub-µm): dielectric breakdown, migration, ESD

- New material interaction: Si/SiC/GaN...Metals like Cu, W, Al...barriers...dielectric

- → Model upgrades needed (size, process, time / age,

- temp. ... dependences)

- Assembly Level

- Thermal aspects: heat path solutions, thermo-mechanical interactions

- Modeling aspects: digital twin, compact digital twin, health monitoring

- W Use Case / Application Level

- Flexibility & performance of QMS technology

Useful in many different markets

- Much increased robustness & safety needed for markets like automotive

Page 30 10/10/202

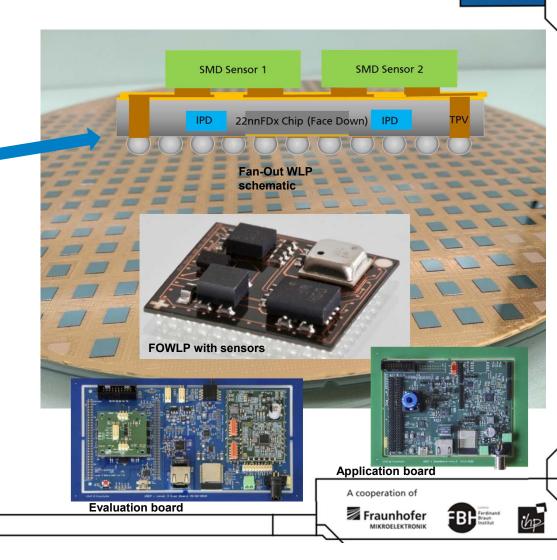

## Application: Sensor platform for next generation electronics

Universal Sensor Platform (USEP)

- Development of universal sensor platform (USEP), with which even smaller system providers can shoulder the growing development and production effort for next generation electronics

- Embedded chips

- Package-size: 10mm x 10mm x 0.2mm

- # 4 layer thinfilm redistribution

- SMD-assembly of different sensors on top

- Assembly of complete sensor system on evaluation and application boards

- System level validation and functionality demonstration

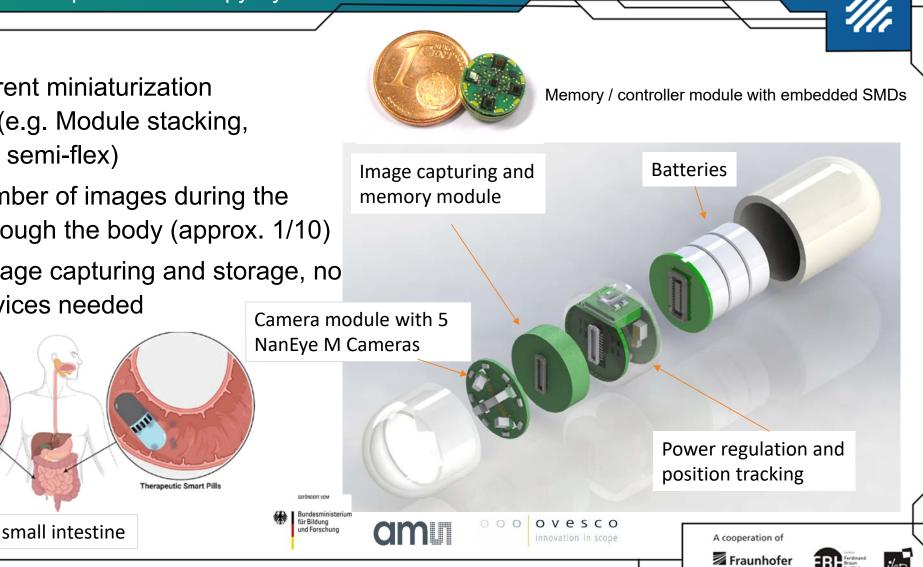

## Application: Modular Capsule Endoscopy System

Project EndoTrace

**Diagnostic Smart Pills**

10/10/202

endo Trace

Page 32

- Use of different miniaturization ‴// techniques (e.g. Module stacking, embedding, semi-flex)

- Reduce number of images during the ‴// passage through the body (approx. 1/10)

- Onboard image capturing and storage, no ‴// external devices needed

MIKROELEKTRONI

## Summary

## **Key Elements for HPC Module Integration**

- Optimized system design and package technology for superior signal- und power integrity (active interposer, back side power supply, ...)

- Thermal management crucial for scalability of package

- Purpose built client (tailoring of chiplet mix for specific applications)

- Handling of thin wafers + TSV integration

- Thermo-mechanical stability → warpage / scalability

- Interconnect scalability → bump size/pitch and assembly technology (extreme placement accuracy specs!)

## System Technology Co-Optimization (STCO)

Page 34 10/10/2024 © Fraunhofer IZM

## Heterogeneous Integration

#### Conclusion

- Co-Design

- Chip design needs a close link to the package design to guarantee high performance and reliability

- Multiple domains with different scaling properties have to be taken into account

- Different design libraries are necessary for product development

- Thermal, mechanical and electrical analysis are key for high yield

- New Materials

- Mechanical, electrical and thermal interactions of different materials not yet used as default

- # Cost

- Complex systems require new packages

- → Therefore new package platform like embedding have to be considered

- Customer Requirements

- Reliability and application specific requirements

- High performance is mostly required in HI-applications

- Control of temperature requires advanced cooling concepts

- # Test

- Application specific tests for complex packages (incl. mixed signal, media, etc.)

- Electrical, mechanical and thermal aspects are important

35 10.10.2024

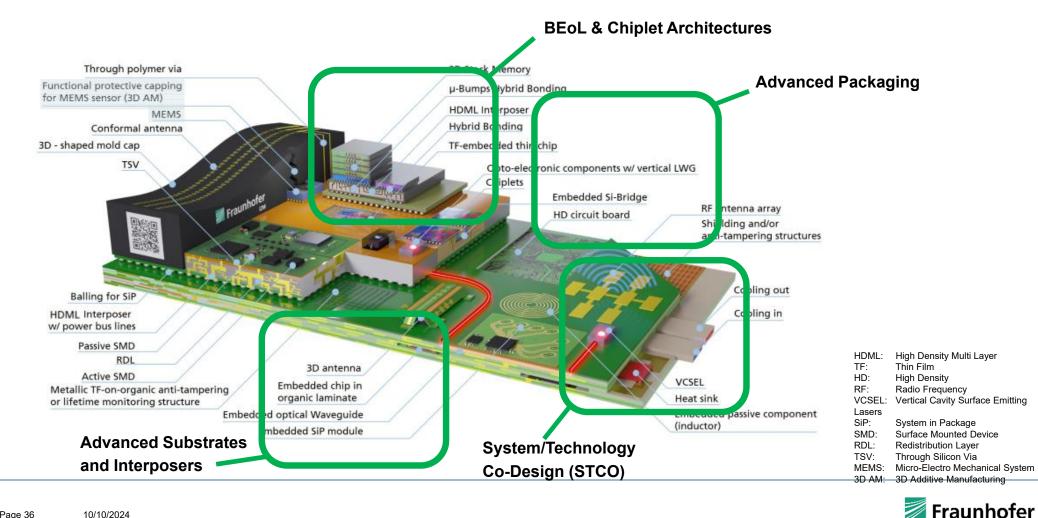

## **Complexity of Advanced Heterogenous System Integration**

10/10/2024 Page 36

IZM

## Contact

Dr. Andreas Middendorf Strategic Business Development

Phone: +49 30 46403-135 E-Mail: <u>andreas.middendorf@izm.fraunhofer.de</u>

Fraunhofer IZM Gustav-Meyer-Allee 25 13355 Berlin www.izm.fraunhofer.de

Fraunhofer Institute for Reliability and Microintegration IZM