#### EU – India Joint Researchers Workshop on Semiconductors

▶ 9 October 2024

How 3D integration can help the emergence of Power efficient innovative architectures?

Olivier Faynot

Silicon Component Division Manager

**CEA-Leti**

$\odot$

EU – INDIA - Joint Researchers Workshop on Semiconductors Olivier Faynot

Brussels, Belgium October 9th 2024

# Outline

- Why going Vertical?

- **3D Integration Building Blocks**

3D integration for innovative architectures

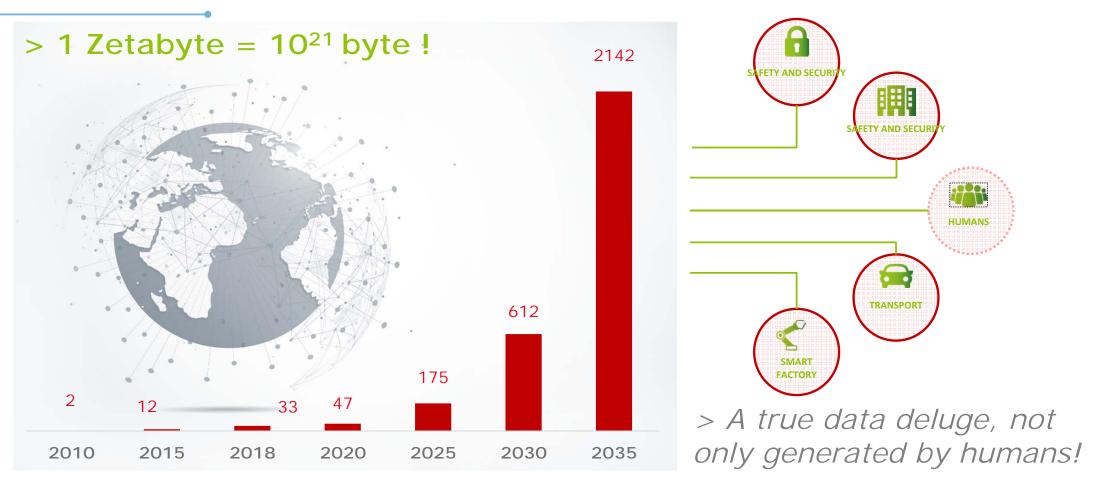

# Global data generation (actual & forecast)

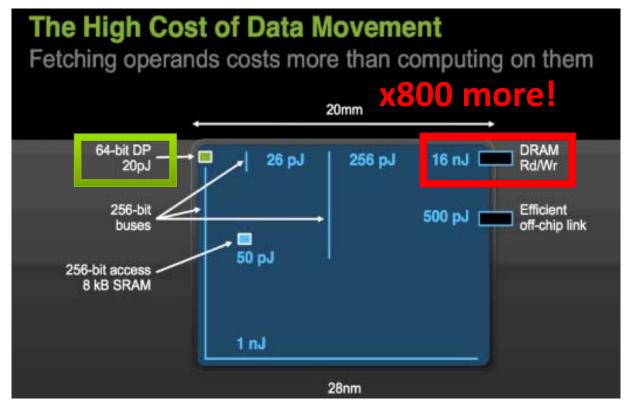

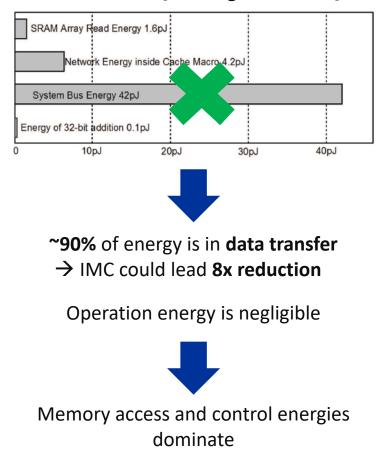

### The cost of moving data

[J. Wang – ISSCC'19]

Bill Dally, "To ExaScale and Beyond", 2010

FEOL CMOS scaling

>1000x by 2030

Memory technologies

**Disruptive Computing**

Chiplet & 3D System

- Why going Vertical?

- 3D Integration Building Blocks

• 3D integration for innovative architectures

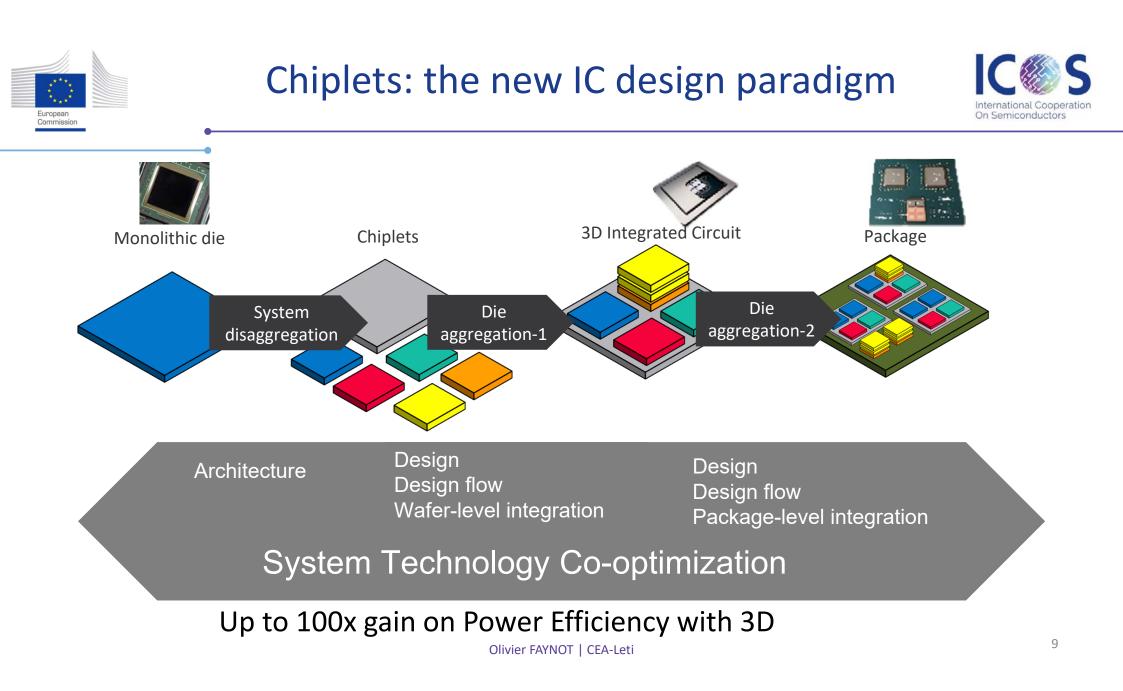

## New paradigms are needed

- Interconnects Bottleneck

- − Dramatic R.C increase  $\rightarrow$  strong impact on latencies

- Gate delay << interconnects delay</li>

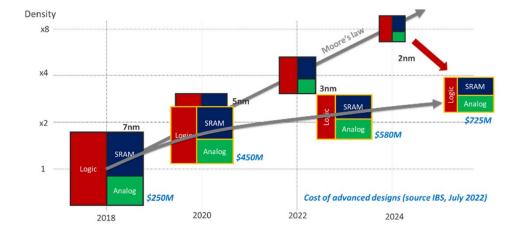

- Scaling becomes costly

- High development cost (mask, IP porting, verif...)

- High manufacturing cost (low yield with large die)

- Heterogeneous architectures needed

- More processing (AI, perception accelerators...)

- More data to handle (memory capacity, fusion...)

- Reuse of legacy (ISA, I/O interface...)

- More modularity, scalability & sustainability

## 3D benefits for advanced systems

- High-performance interconnections

- − Low R, L, C  $\rightarrow$  latencies, bandwidth, energy efficiency

- Massively parallel processing with vertical links

- Answers to modern design needs

- Reduced form factors, I/O number non limited by pad size

- Partitioning, IP reuse, scalability & density

- Heterogeneous integration

- Mixed CMOS nodes & materials (Si, III-V, II-VI, passives, MEMS)

Sensor on logic

Memory on Logic Chiplet-based integrations EU – INDIA – Joint Researchers Workshop on Semiconductors Olivier FAYNOT | CEA-Leti

**III-V on Logic**

SoC performance

SiP benefits

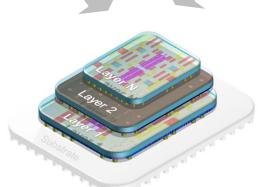

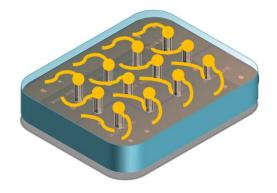

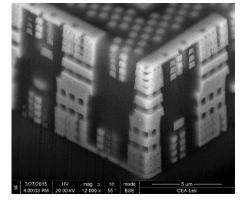

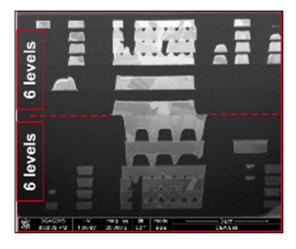

# Morphology of a 3D circuit

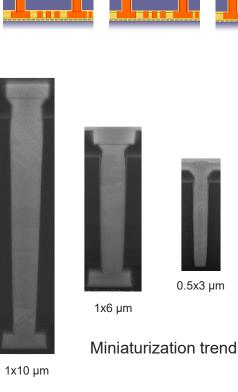

#### • Layer-to-layer vertical interconnects

Miniaturization trend: pillars, hybrid bonding ...

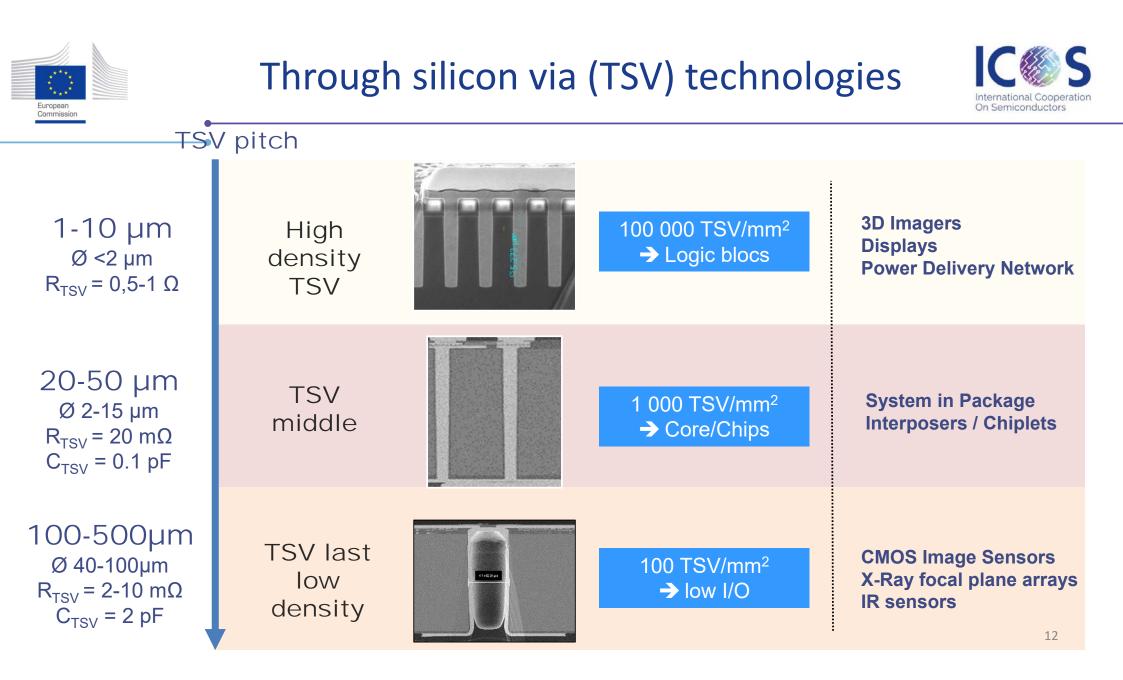

#### • Intra-layer vertical interconnects

Communication between frontside and backside of each layers Through silicon Vias (TSV)

• Intra-layer in-plane interconnects (2D)

ReDistribution Layers (RDL)

# Assembly configurations

#### **Die to die**

- Known Good Dies → yield

- Heterogeneous integration

- Flexible design

- Low assembly throughput

- Low alignment accuracy

- Very high cost

Pure packaging operation

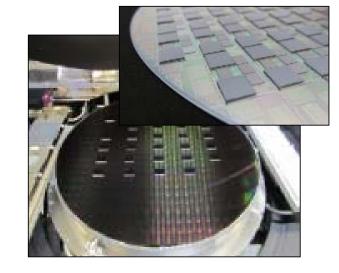

#### Wafer to wafer

Collective processHigh assembly throughputHigh alignment accuracy

Yield lossStrong design limitation

Mass production for imagers and memories

EU – INDIA – Joint Researchers Workshop on Semiconductors Olivier FAYNOT | CEA-Leti

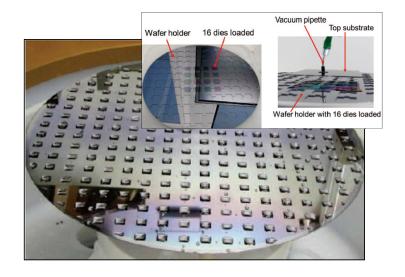

#### **Die to wafer**

- Known Good Dies  $\rightarrow$  yield

- Heterogeneous integration

- Flexible design

- Low assembly throughput

- Low alignment accuracy

Breakthrough processes needed

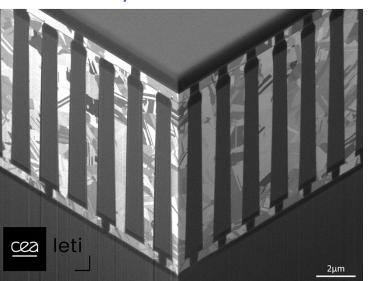

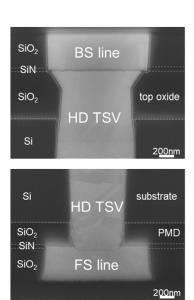

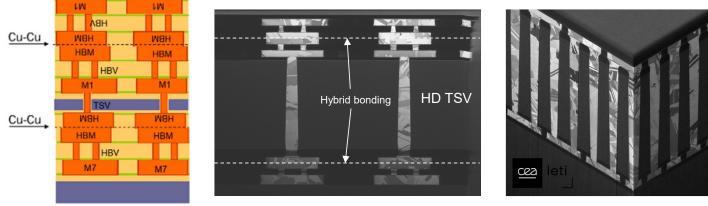

# "High density TSV" (HD-TSV) process flow

Base wafer

- TSV done after circuit processing\*

- Diameter typically < 2µm & height <15 µm

- Uniform silicon thinning needed (TTV < 1 $\mu m$ )

- TSV fully filled with Cu

S. Borel et al., Electronic Components and Technology Conference, 2023

Base water

1 0X-0) 9µm

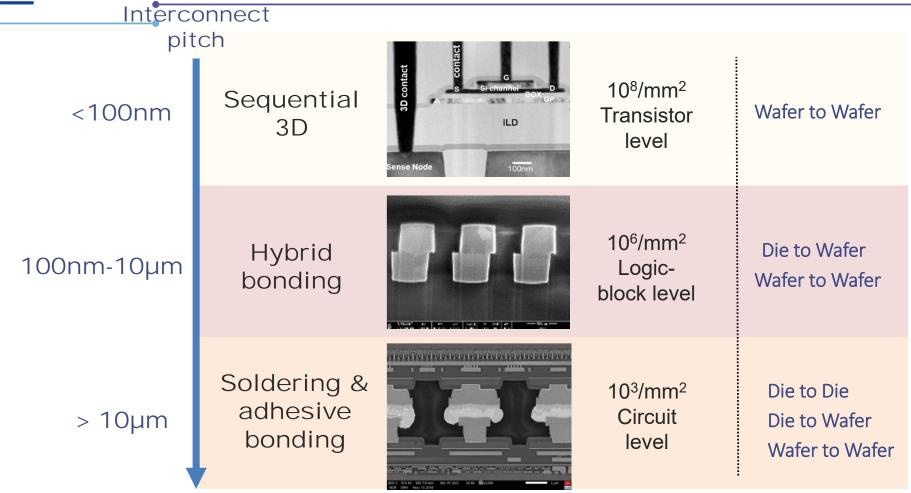

## Technologies for 3D interconnects

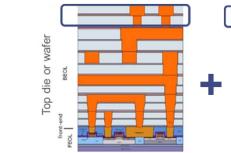

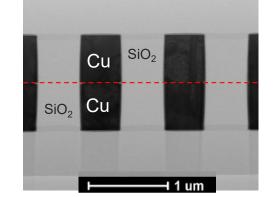

# Direct hybrid bonding process: a hot topic !

- Mix SiO<sub>2</sub>/SiO<sub>2</sub> & Cu/Cu bonding

- Precautious CMP process

- Proper design rule manual

- Unprecedented benefits

- Ultra dense interconnections

- Improved mechanical strength, no organics

J. Jourdon et al., IEDM 2018

EU – INDIA – Joint Researchers Workshop on Semiconductors

Olivier FAYNOT | CEA-Leti

#### Direct hybrid bonding principle

Y. Beilliard et al., IJSS, Vol. 117, June 2017, pp. 208-220

L. Millet et al., VLSI 2018

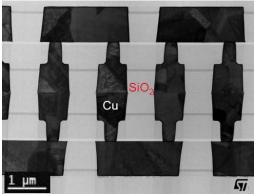

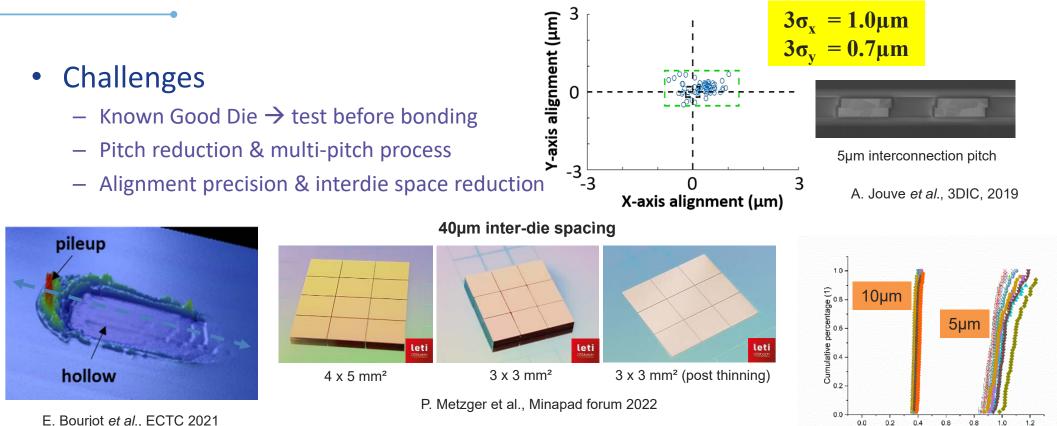

## Die-to-wafer hybrid bonding

E. Bourjot et al., ECTC 2021

E. Bourjot et al., « Towards a Complete Direct Hybrid Bonding D2W Integration Flow: Known-Good-Dies and Die Planarization Modules Development », 3DIC

E. Bourjot et al., "Known Good Dies (KGD) strategies compatible with D2W Direct Hybrid bonding", MAM 2020

E. Bourjot et al., « 10µm and 5µm die-to-wafer direct hybrid bonding », in 2022 ESTC, sept. 2022.

EU – INDIA – Joint Researchers Workshop on Semiconductors Olivier FAYNOT | CEA-Leti

Resistance per daisy chain-link (Ohm)

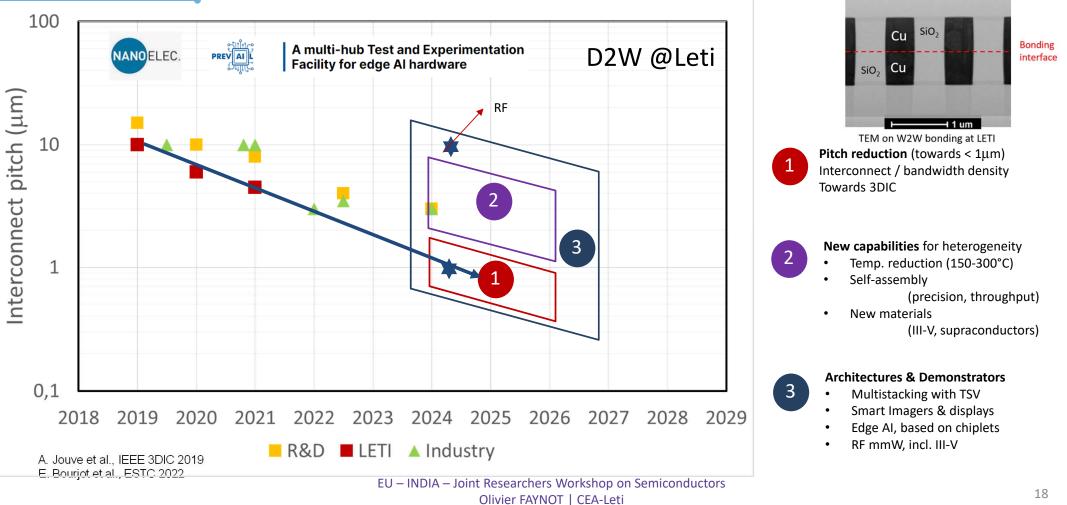

## Hybrid Bonding Solutions

- Direct bonding of metal and dielectric

- Down to 1 micron pitch interconnects

- Wafer-to-wafer

(W2W) or Die-to wafer (D2W)

technologies

- High heterogeneity allowed by D2W

- > Collective D2W approaches

- Self-assembly for high precision & high throughput

## Hybrid bonding pitch roadmap

Pitch down to previous Cooperation

- Why going Vertical?

- **3D Integration Building Blocks**

- 3D integration for innovative architectures

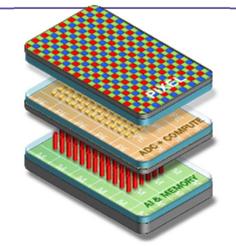

## Smart imager developments

- From imagers to vision sensors

- Edge-AI targeted applications (autonomous vehicle)

- 3-layer scheme:

- Pixel array / Readout IC / AI & memory layer

Autonomous vehicle functions

1x10 $\mu$ m HD TSV (2 $\mu$ m pitch) 100% yield on 10 000 TSV daisy chains R<sub>TSV</sub> = 500m $\Omega$ Misalignment HB2: max. 1  $\mu$ m (avg 200 nm) Misalignment HB1: max. 350 nm (avg 100 nm) 1x5 $\mu$ m HD TSV under development

J. J. Suarez Berru , 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 2023, pp. 97-102,

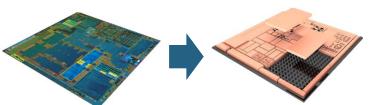

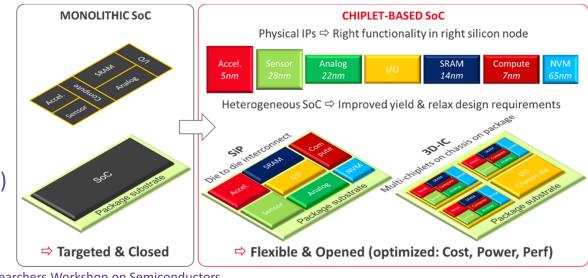

# Chiplet approach: Heterogenous IC design

- Interposer & chiplets

- − Interconnects performance  $\rightarrow$  R.C delay

- Exceeding latency & bandwidth limits

- Cost/form factor advantages

- Appropriate partitioning

- Heterogeneous IC design

- Optimized technology for each function

- specialization by app.: CPU, GPU, AI (...)

- Standardization (coming soon, hopefully)

The end of "all for the SoC" paradigm (image from DARPA)

Chiplet topology on interposer

## HPC and AI converging roadmaps

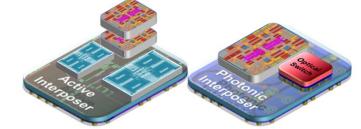

#### Metallic Passive interposer

✓ Chip-to-chip side-by-side communication

#### Active interposer (ENoC) Intact

Extended communication capability (increased distance, routing, power management, ...)

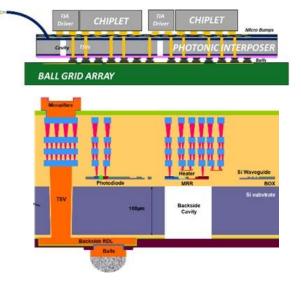

#### Photonic interposer (ONoC) Starac

Optical communication:

- ✓ Reduction of on-chip latencies

- ✓ Higher throughput

- ✓ Lower energy consumption

- ✓ Scalability

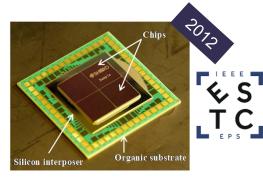

#### More than 12 years expertise on Silicon Interposers

Y. Thonnart et al., "POPSTAR: a Robust Modular Optical NoC Architecture for Chiplet-based 3D Integrated Systems," Proc. DATE, 2020, p. 6. D. Saint Patrice et al, "Process Integration of Photonic Interposer for Chiplet-Based 3D Systems" Proc. IEEE ECTC, 2023

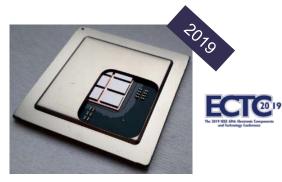

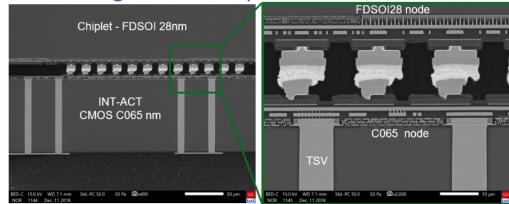

## Active interposers (INTACT)

life.auamentec

- 1st functional architecture with active interposer

- Si interposer: 65nm including TSV middle 10x100 $\mu$ m

- Chiplets FDSOI 28nm

- State of the art 20  $\mu m$  pitch Cu pillars (diam. 10  $\mu m$ )

- High performance 3D connecting between chiplets and DC/DC convertors

D. Lattard et al., 3DIC 2016 E. Guthmuller et al., ESSIRC 2018 D. Dutoit, D43D 2018 P. Coudrain et al., ECTC, 2019

20 19 NANDELEC

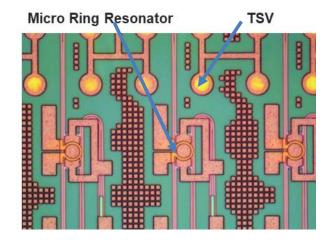

## Interposer level optical links for HPC

#### Architecture

**ONoC Popstar Interposer**

#### **Co-Integration & test**

#### Co-integration TSV mid (12x100µm) and photonic FEOL after Metal 1

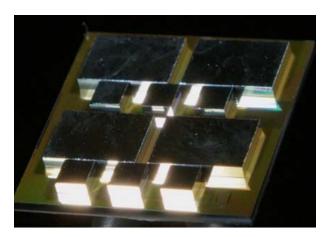

#### 3D Assembly

Silicon Photonic Interposer front side: 4 chiplets and 6 electro-optical drivers in 28nm FD-SOI

**Full demonstration**

expected in 2025

- 4 x 16 cores FDSOI 28nm Chiplet

- 6 electro-optical drivers (Rx/Tx) in 28nm FDSOI

- Silicon photonic interposer: Full integration @CEA-Leti

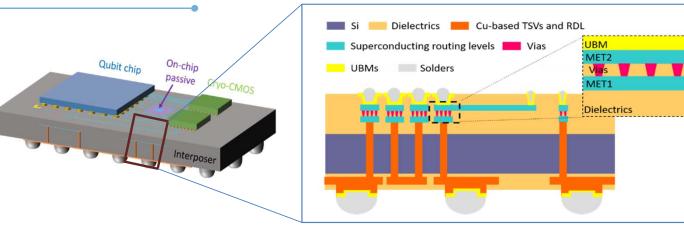

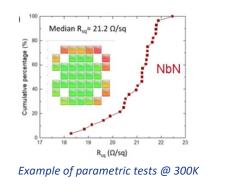

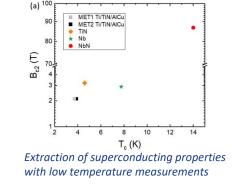

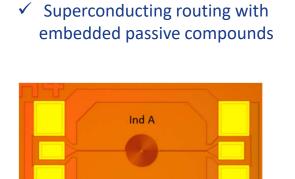

### Leti Quantum interposers

UBM

MET2 NbN

Dielectrics

Vias

Ti/TiN/W

100 µm

C. Thomas et al., Materials for Quantum Technology, 2, 3, 035001, (2022)

500 nm

٠

Ο

$\bigcirc$

$\bigcirc$

Ο

$\bigcirc$

$\mathbf{O}$

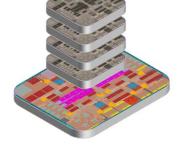

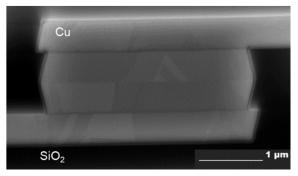

More Moore : Wafer level chip architecture

Minimized TSV footprint on active devices

Heterogeneous Integration of advanced in

Combination of DTW + TSV (Mid or HD)

**TSV HD + W2W** allows many active layers wafer

Interconnection density increase (x, y z)

Power delivery network

**Applications HPC & IA**

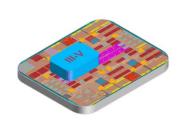

More than Moore : system level

#### Heterogeneous compute chiplets:

- Advanced node (7nm, 5nm)

- Heterogeneous (size, pitch, node)

- Full digital compute chiplet

- Optional: TSV HD for memory cube

- Face down

#### 3D assembly:

- Die-to-Wafer

- Hybrid Bonding

- Face-to-Face

#### Base die:

- Mature node (FD28, GF22FDX,...)

- Face up

- TSV for power delivery and los (preferred mid process)

EU – INDIA – Joint Researchers Workshop on Semiconductors

This project has received funding from the European Union's Horizon Europe research and innovation programme under GA N° 101092562

#### www.icos-semiconductors.eu