# Advancements in Neuromorphic Computing Using Silicon Nitride Memristors for IoT and Security

## N. Vasileiadis <sup>a,b</sup>, A. Mavropoulis <sup>a</sup>, I. Karafyllidis <sup>b</sup>, G. Ch. Sirakoulis <sup>b</sup>, P. Dimitrakis <sup>a</sup>

<sup>a</sup> Institute of Nanoscience and Nanotechnology, NCSR "Demokritos", Ag. Paraskevi 15341, Greece

<sup>b</sup> Department of Electrical and Computer Engineering, Democritus University of Thrace, Xanthi 67100, Greece

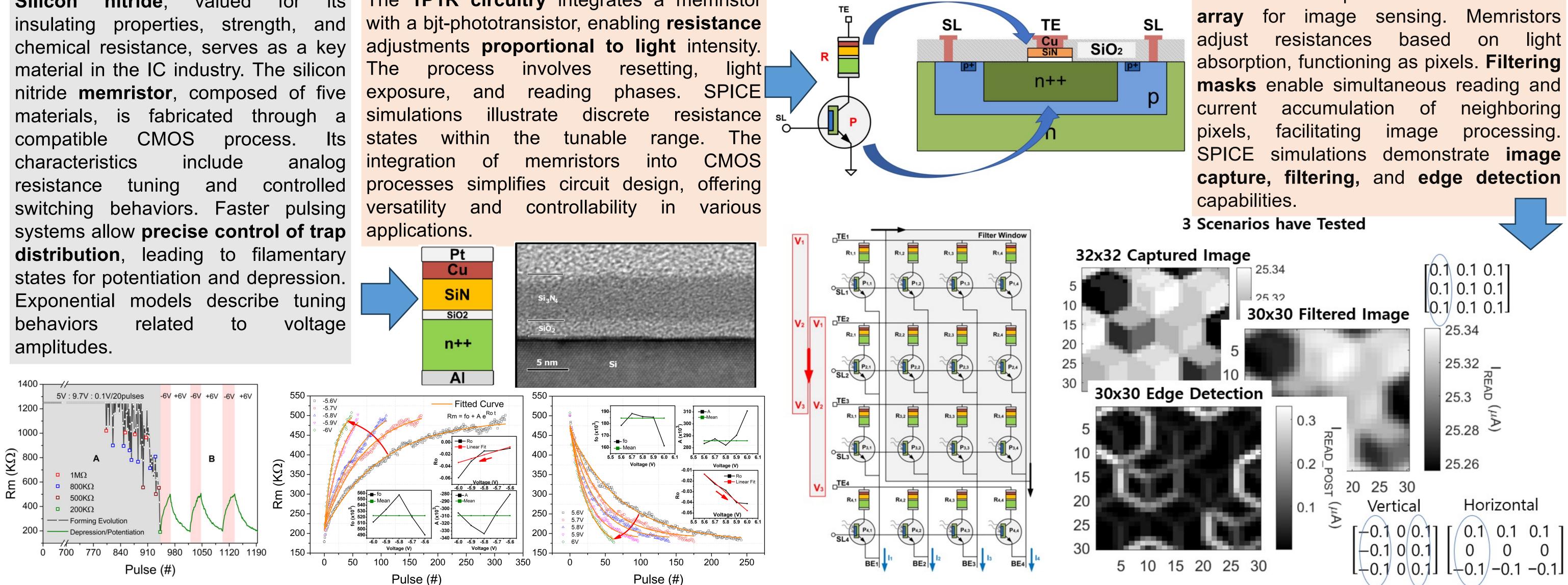

#### A new 1Ph1R image sensor with *in-memory* computing properties based on silicon nitride devices

Silicon its nitride. valued for CMOS process.

The 1P1R circuitry integrates a memristor resetting, light SPICE and reading phases. discrete illustrate The tunable the range.

The 1P1R concept extends to a **crossbar**

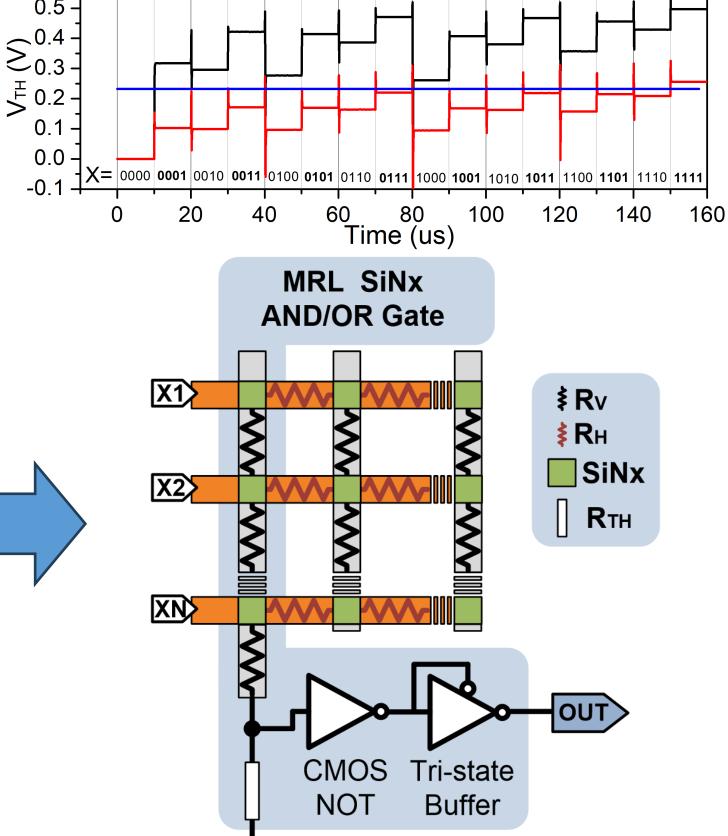

#### Novel crossbar array of silicon nitride resistive memories on SOI enables memristor rationed logic

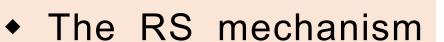

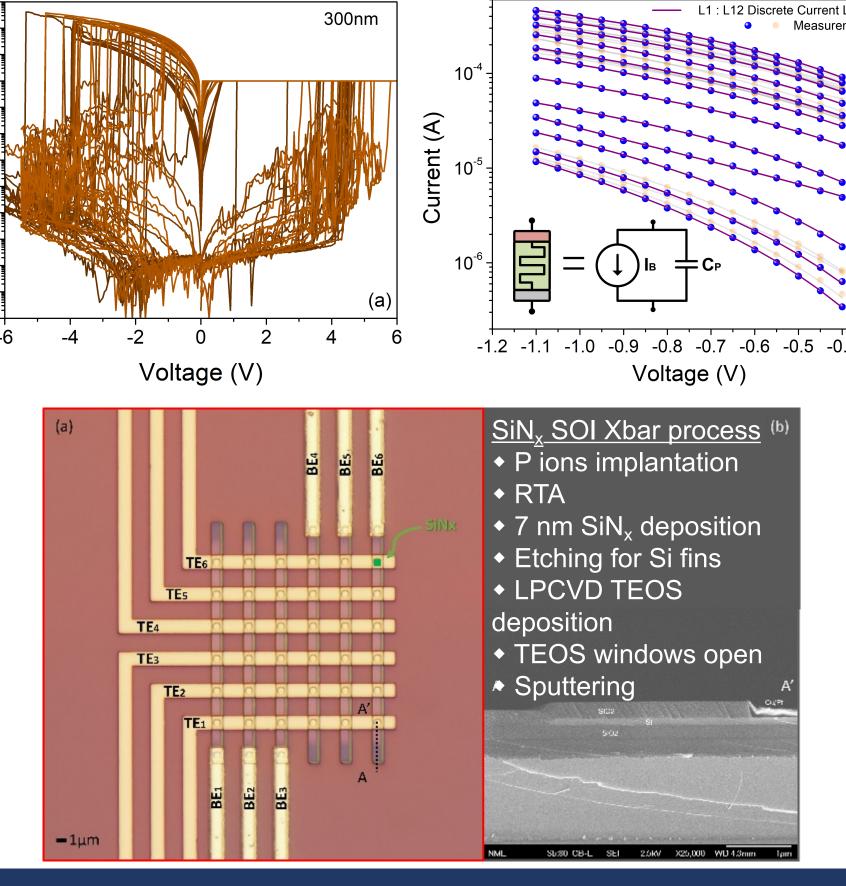

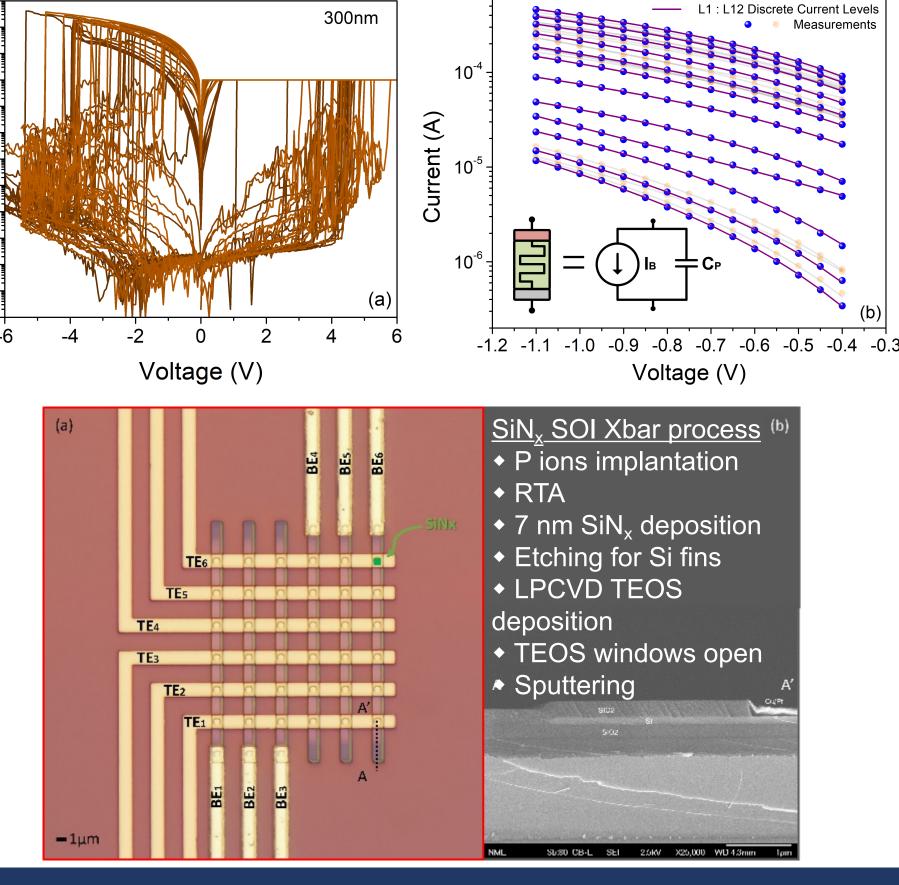

- In this work, the fabrication of Xbar arrays of SiNx resistive memories on SOI substrate and their utilization to realize MRL circuits are presented.

- Typical electrical characterization of the memristors revealed their ability of multi-state operation by the presence of 12 well separated resistance levels.

- Through a dedicated fitting model, a reconfigurable logic based on MRL scheme is designed/evaluated and a Xbar integration methodology was proposed.

- Several circuitry aspects were simulated in SPICE with a SiNx SOI Xbar array calibrated model and power optimization prospects were discussed.

**Parallel connected** SiN<sub>x</sub> memristors at a

- AND - Thresshold —— OR — 0.6 –

attributed to the native 3 of presence traps created by the deficiency ਹੋ nitrogen and their subsequent density enhancement under the applied electric field.

Significant current fluctuations are observed due to the unhindered electron exchange between the N<sup>++</sup> Si (BE) and the  $SiN_x$  boarder traps.

common node  $V_{th}$  with a resistor  $R_{th}$  are a reconfigurable structure as it is possible to voltage change the of common node  $V_{th}$  by varying the conductance state of each memristor.

- Logic 1 (True) is represented by 1V while **Logic 0** (False) by Non-Contact (NC).

- Reduced complexity with simplified design ready for larger scale integrations using a unique threshold V<sub>th</sub> and unique node resistance **R**<sub>th</sub>.

- Intermediate resistances as well as the increasing number of inputs can affect the performance of the proposed MRL.

- Larger MRL gates can be achieved by combining more smaller crossbars using the segmented architecture of crossbars.

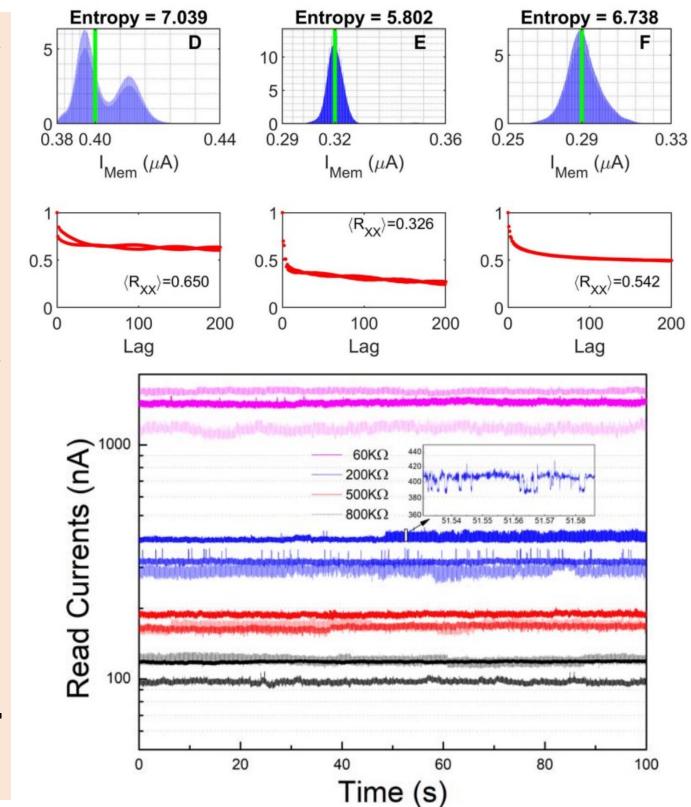

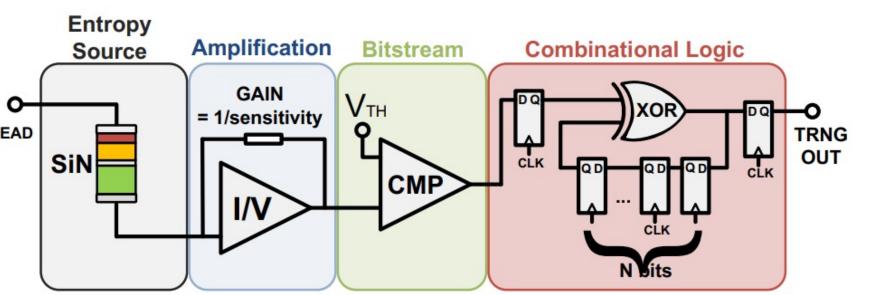

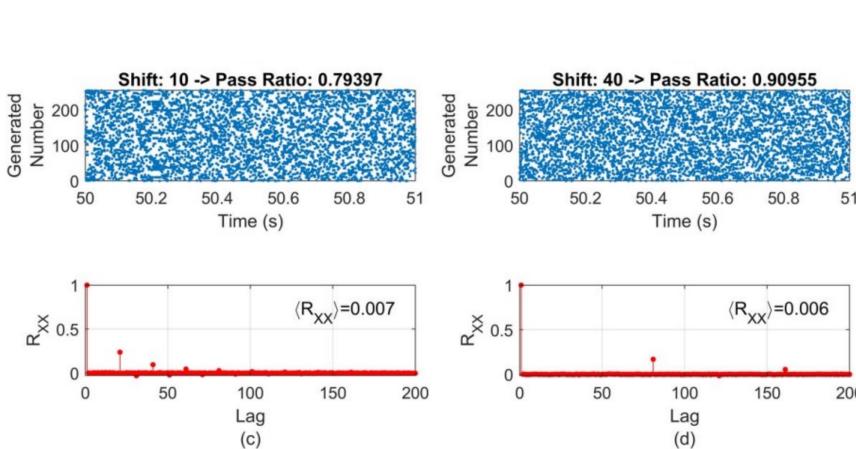

### True random number (TRNG) generator based on multi-state silicon nitride memristor entropy sources combination

random number True generators (TRNGs) utilize randomness from physical sources like flicker noise or random telegraph noise for cryptographic purposes. TRNG systems face challenges including high consumption power and design complexity, limiting their use in IoT applications. Proposed solutions like memristive **TRNG** aim to address these issues by modularity offering to the entropy device, source flexibility enhancing system and tweakability.

The study explores achieved twelve states through tuning a algorithm, showcasing dominant resistance silicon nitride levels in

TRNG The Memristive SiNx circuit employs memristors to generate VREAD current noise signals. A comparator generates a bitstream based on a

| devices.                                   | 0 |

|--------------------------------------------|---|

| <ul> <li>Noise analysis reveals</li> </ul> |   |

| flicker (1/f) and RTN                      |   |

| <b>noise</b> $(1/f^2)$ due to trap         |   |

| charging.                                  |   |

| <ul> <li>Entropy sources'</li> </ul>       |   |

| randomness and                             |   |

| periodicities are                          |   |

| examined through                           |   |

| histograms and auto-                       |   |

| correlation diagrams.                      |   |

threshold. Postprocessing XOR shift involves an randomness for logic enhancement. Multiple sources can multiple create or bitstreams combined using crossbar arrays.

#### **ACKNOWLEDGEMENTS & Contact info**

This work was supported in part by the research projects "3D-TOPOS" (MIS 5131411) and "LIMA-chip" (Proj.No. 2748) which are funded by the Operational Programme NSRF 2014-2020 and the Hellenic Foundation of Research and Innovation (HFRI) respectively. Corresponding authors: n.vasiliadis@inn.demokritos.gr (N. Vasileiadis) p.dimitrakis@inn.demokritos.gr (P. Dimitrakis).

## **EU-South Korea Joint Researchers Forum on Semiconductors**