# Innovative materials and devices for future logic and memory

## technologies

Sujin Ahn

EVP, Advanced Technology Development Office, Samsung Electronics

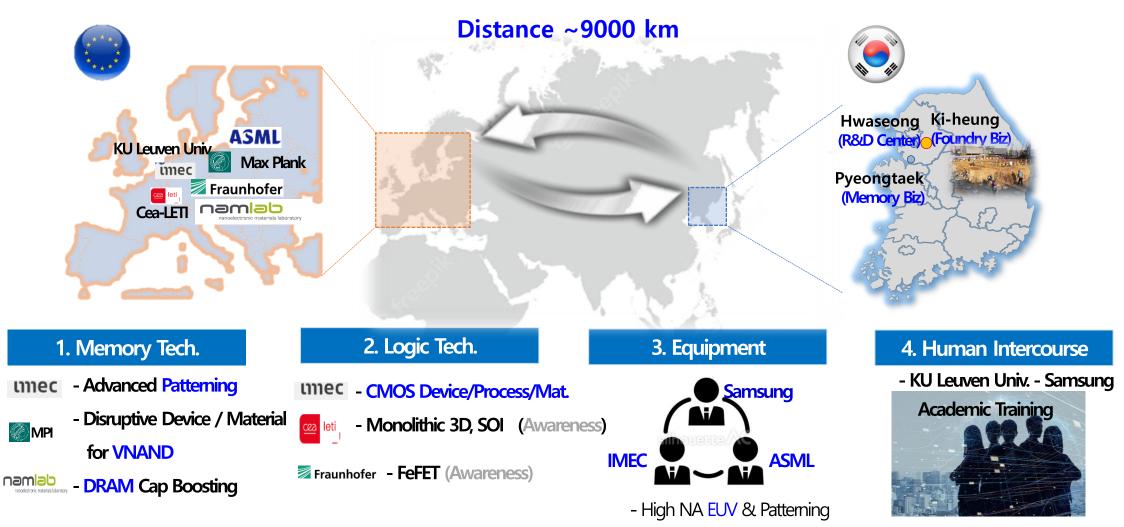

## **Collaboration Journey with EU over 20 years**

History of Overcoming Technical Challenges in Device Scaling

#### SAMSUNG

SAMSUNG

## Contents

01 New Eras Driven by Semiconductors

02 Upcoming Challenges and Innovations

03 Conclusion

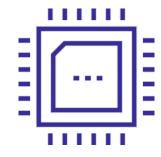

## New Eras Driven by Semiconductors

## Paradigm Shift in Computing over the Past 80 Years

Every 15 Years, Introducing New Devices and Accelerates Computing Speed x1000 times Faster

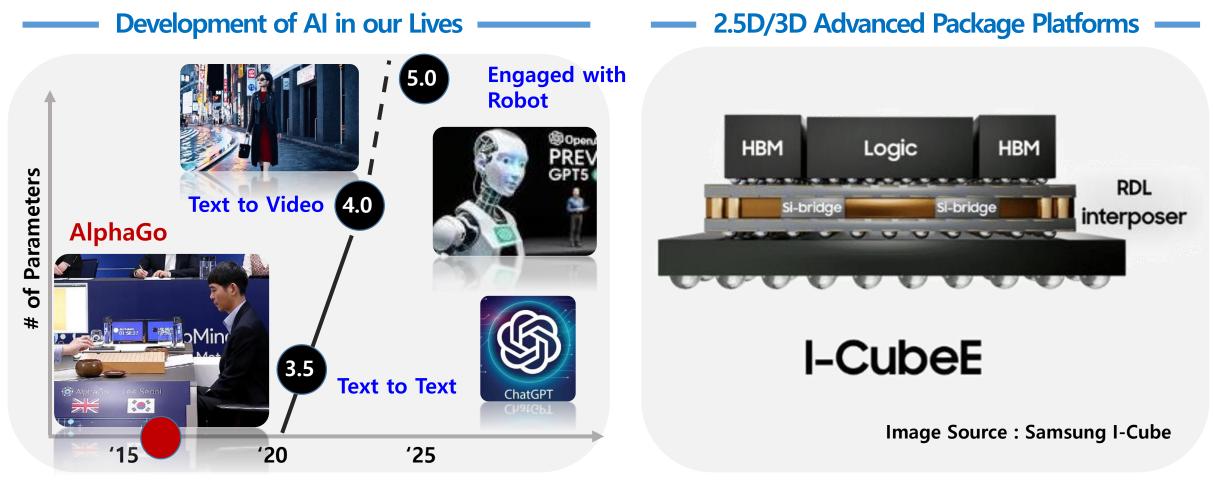

## The Future Transformed by Generative AI

The Expansion of Large-scale LLM models Drives the Steep Growth in HPC Servers with Advanced Logic, Memory, even Packaging Technology

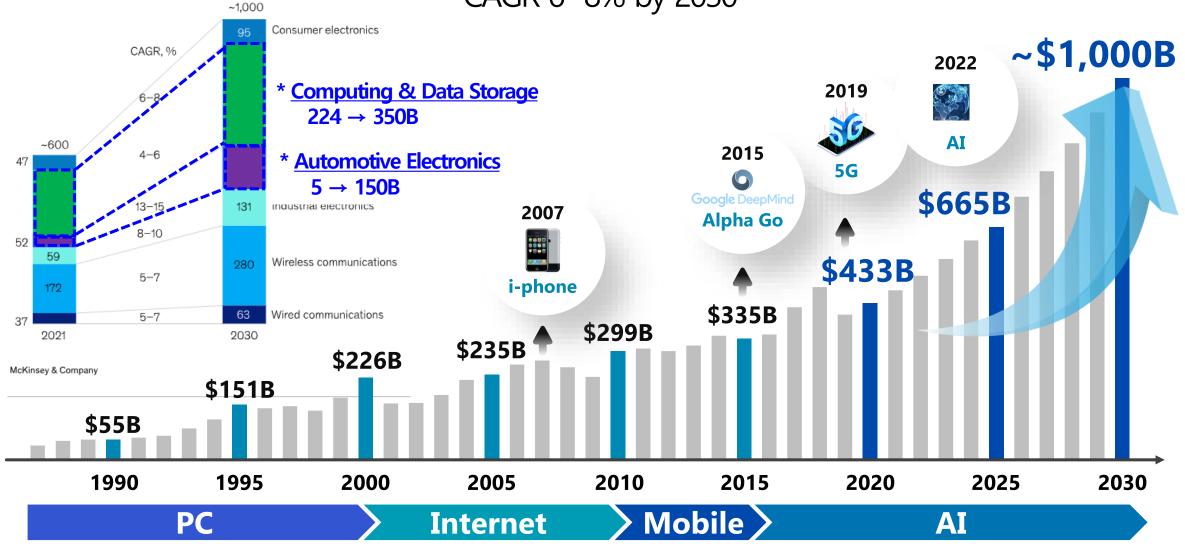

#### **Semiconductor Market Growth**

CAGR 6~8% by 2030

#### SAMSUNG

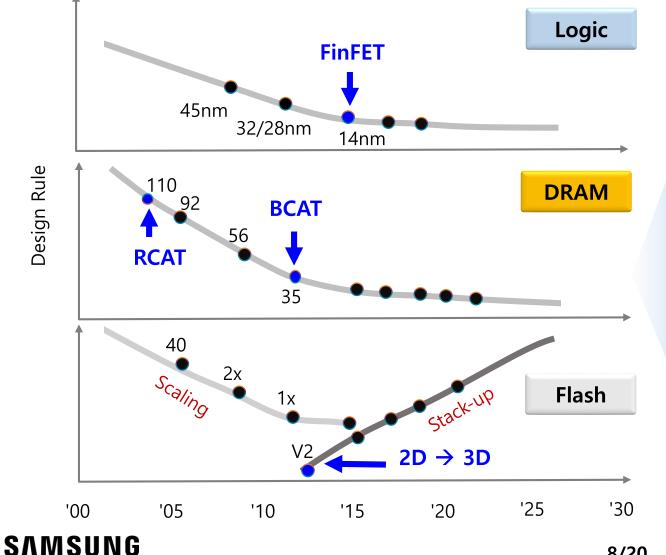

#### **Moore's Law Extended by Structure Innovations**

Logic, DRAM, and Flash Transistors has changed from Planar to 3D Structures

8/20

Design Rule

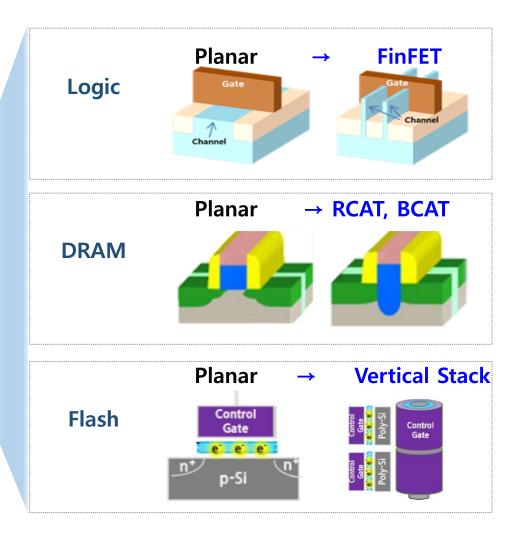

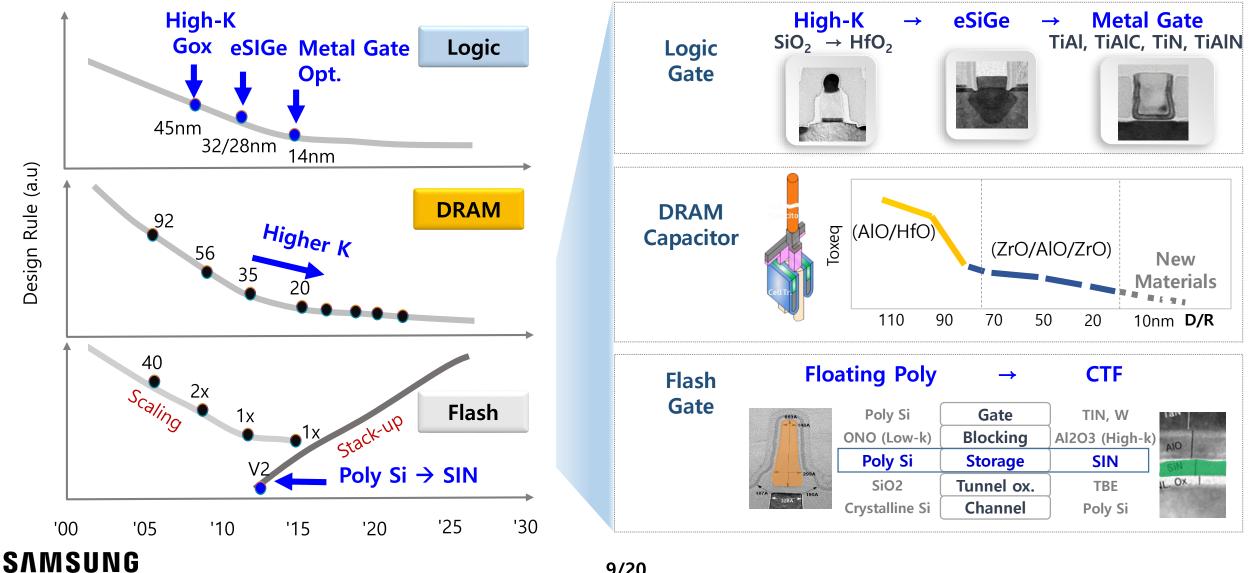

### **Moore's Law Extended by Material Innovations**

High-K Dielectrics, SiGe Epi, Metal Gates, and New Gate Stack Integration

9/20

Design Rule (a.u)

## Upcoming Challenges and Innovations

## **Prospects for Logic Transistor Beyond FinFET**

Gate All Around Transistor followed by 3D Stack FET(CFET) and Others

стсит

СТСЛ

NMOS

PMOS

#### 3nm

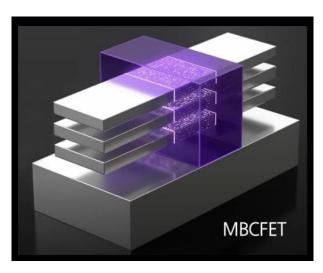

#### World 1<sup>st</sup> 3nm GAA Transistor Samsung MBCFET ™

16% Area Reduction45% Power Saving,23% Performance Improvement

than 5nm FinFET

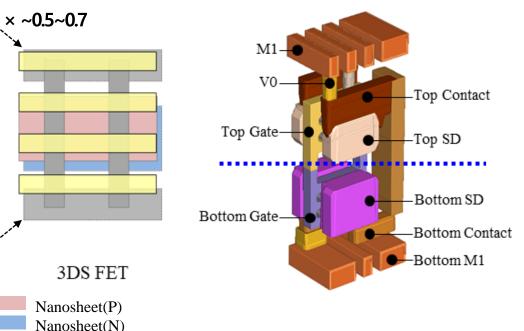

#### 3D Stack FET(CFET) and Others

: NMOS and PMOS are Stacked Vertically A Significant Area Reduction by up to half

#### [Layout Comparison]

#### SAMSUNG

11/20

Gate

Metal

MBCFET<sup>TM</sup>

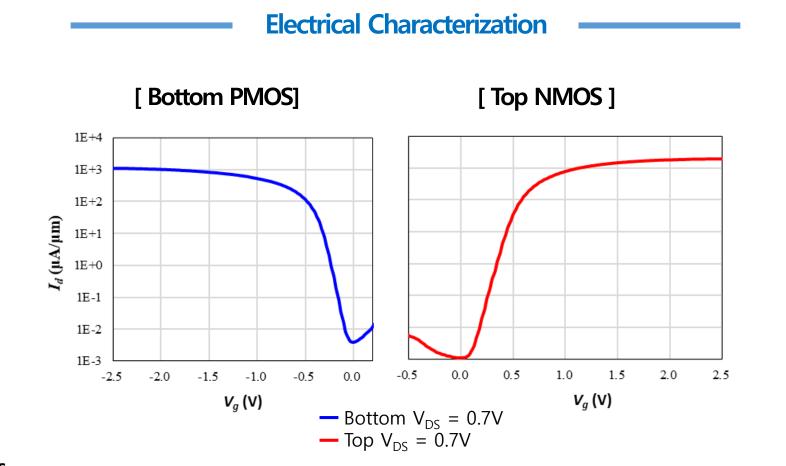

## **3D Stack FET in GAA Transistor Platform**

1<sup>st</sup> Successful Demonstration of Fabrication and Electrical Properties of Transistors

Vertical SEM View \_\_\_\_\_

NMOS

NMOS

channel

Top

SD

Channel

SD

Channel

Channel

'IEDM 23, JH Park, Samsung Electronics

## **Beyond Si Channel Materials**

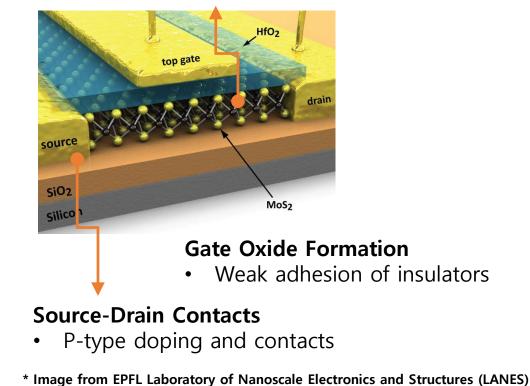

Thin 2D Materials such as MoS2, WSe2 needs Entire Gate Stack Process Renovation

#### **High Mobility Channel Materials** Higher Mobility 2D material > Si (@ same THK) **3nm GAA Transistor** Si (e 2D semiconductors 3.1 S Van der Waals force 10<sup>2</sup>-6.5 Å MoS. Mobility (cm<sup>2</sup> V<sup>-1</sup> Si (h+) Y. Liu et al., Nature comm., 591, 43 (2021) 10<sup>1</sup> 2 3 n Body thickness (nm)

#### Process Integration Challenges

#### **Growth of Channel Material**

- Large-area growth with low defect density

- Low-temp synthesis for BEOL applications

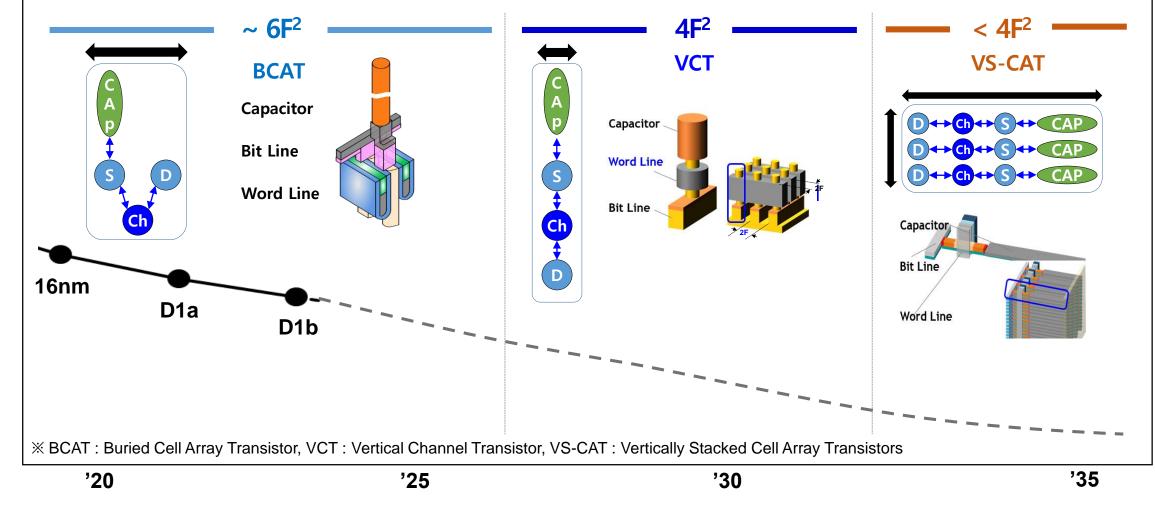

## **Prospects for DRAM Cell Beyond 10nm**

Area Scaling Continues via Vertical Channel Transistor or Vertically Stacked Cell Array

SAMSUNG

Design Rule [nm]

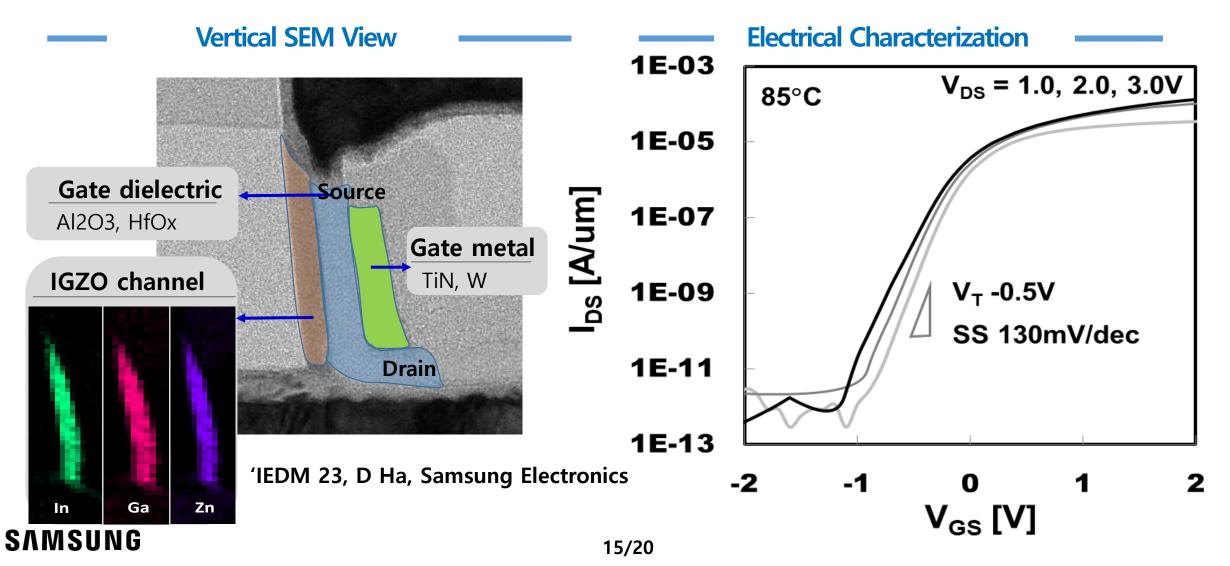

### **Vertical Channel Transistor**

Successful Demonstration with Non-Silicon Channel(IGZO) Transistor

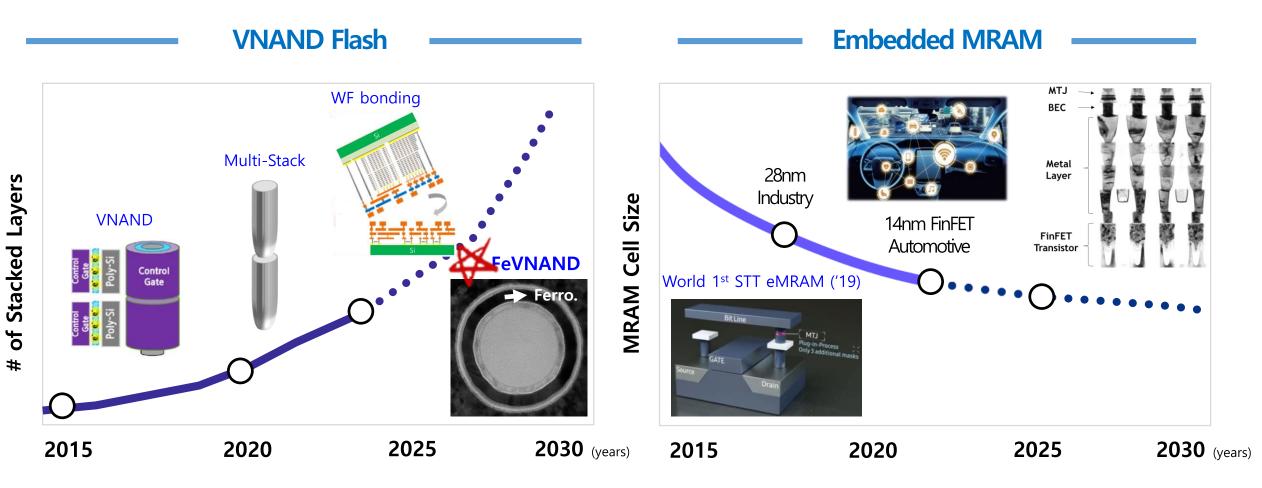

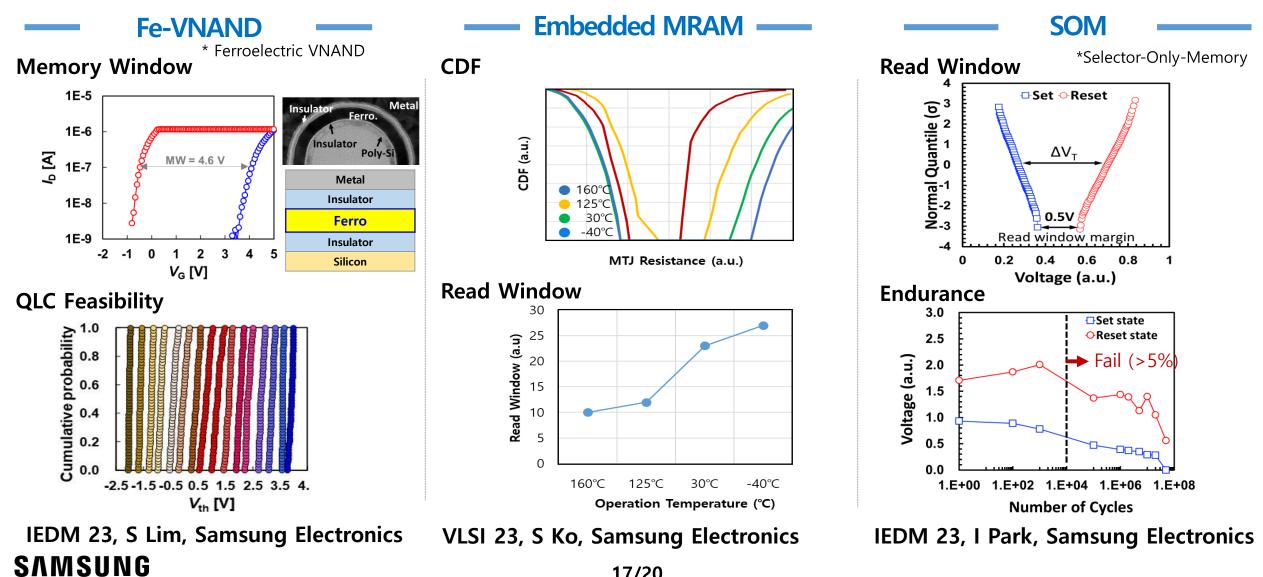

#### **Prospects for Non-Volatile Memories**

VNAND Continues to Stack Up with Cell-Peri Bonding and New Storage Media Adoption Embedded MRAM Continues to Shrink with MTJ Stack and Process Innovations

## **Emerging Technologies for Non-Volatile Memories**

Research and Developments Activities With Various Materials and Process Innovations

## Conclusion

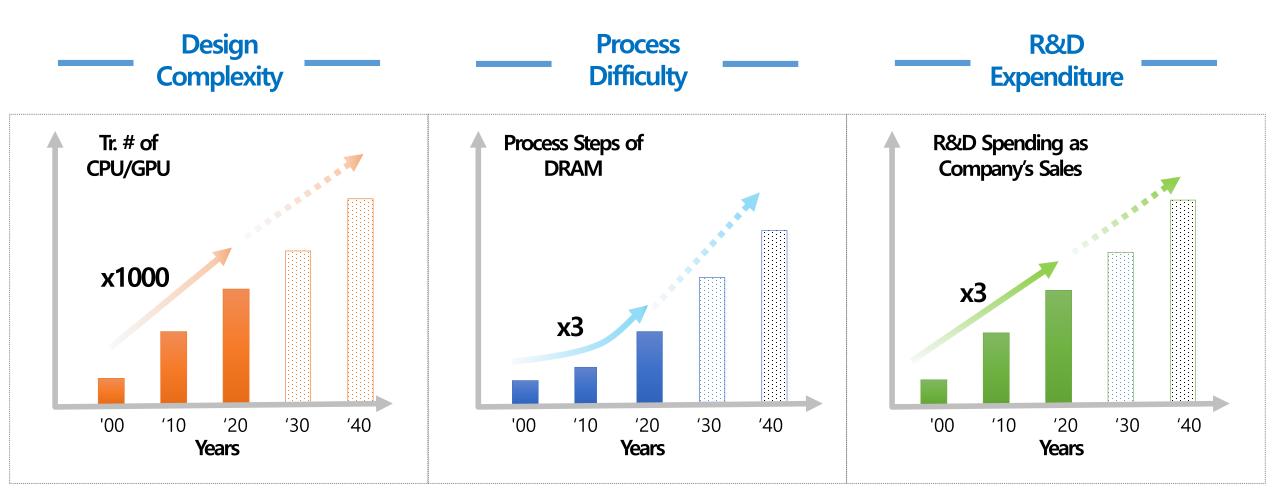

### **Another Challenges faced by Semiconductor Industry**

More Complex, More Difficult, More Expensive

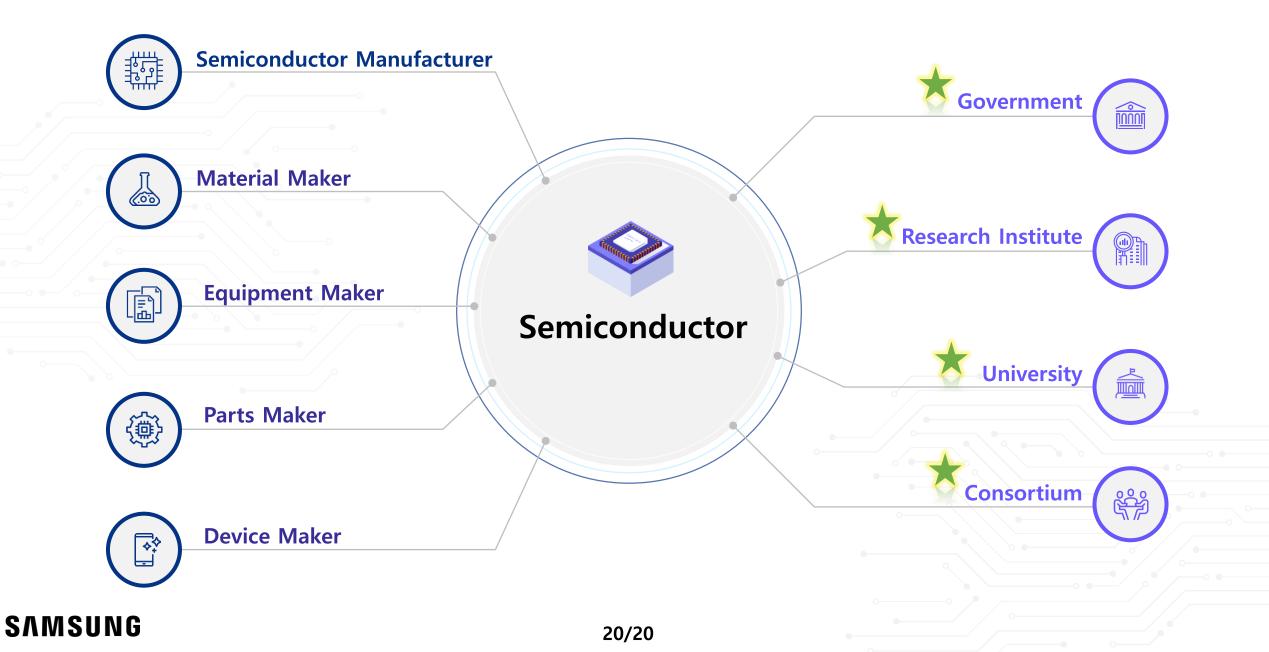

## **Co-operative Global ECO system**

## Thank You