#### ESSCIRC/ESSDERC 2023

SiNANO-ICOS Workshop "European Strengths and Gaps in Emerging Semiconductor Technologies"

# Advanced computation: review of main EU and international activities and technologies

Olivier Faynot and Nadine Collaert CEA-Leti, IMEC olivier.faynot@cea.fr, nadine.collaert@imec.be

Lisbon, September 11, 2023

ESSDERC/ESSCIRC 2023 Workshop European Strengths and Gaps in Emerging Semiconductor Technologies

## Outline

- □ Introduction: trends and challenges

- **Computing roadmap**:

- CMOS device architecture

- 2D materials for FEOL

- New materials for BEOL

- Lithography

- Memory technologies

- □ Beyond Von Neumann disruptive approaches:

- Near or in-memory computing

- Quantum computing

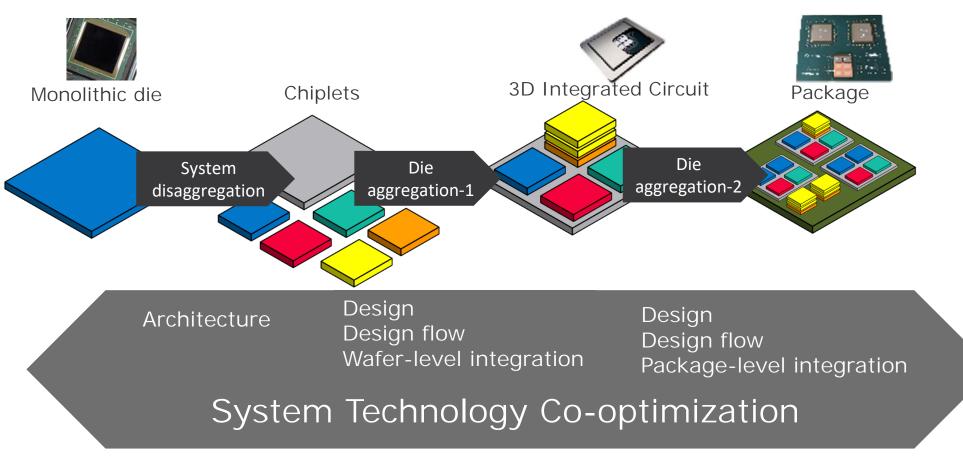

- □ Heterogenous integration: from chiplets to functional backside

- EU and non-EU actors

- Conclusions

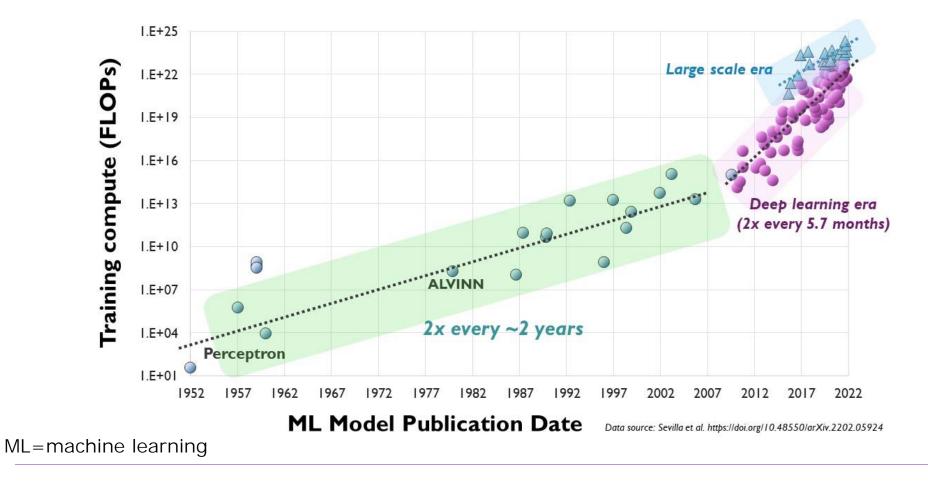

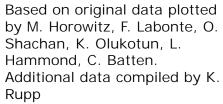

#### Compute needs for ML continue to grow

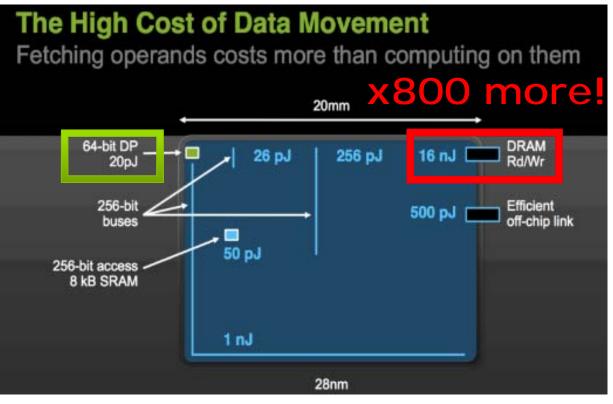

### The cost of moving data

[J. Wang – ISSCC'19]

Bill Dally, "To ExaScale and Beyond", 2010

D% of energy is in data transfer

→ IMC could lead 8x reduction

Operation energy is negligible

Memory access and control energies dominate

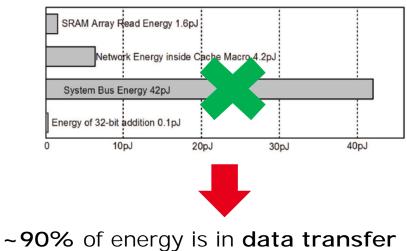

Carbon Emissions Estimate of Logic Manufacturing: "Do Nothing" Scenario

Constant electricity mix (0.49 kCO2eq/kWh), Abatement and GHG global warming potential according to IPCC assumed for the years 2020-2030. Volume technology mix from IBS "Foundry Market Trends and Strategic Implications" Vol 30, N 12, Dec 2021. Logic nodes only. \*imec.netzero emissions estimate of imec process nodes representative of foundry nodes.

6

The required gain in energy efficiency

CMOS scaling

>1000x by 2030

Memory technologies

**Disruptive Computing**

Chiplet & 3D System

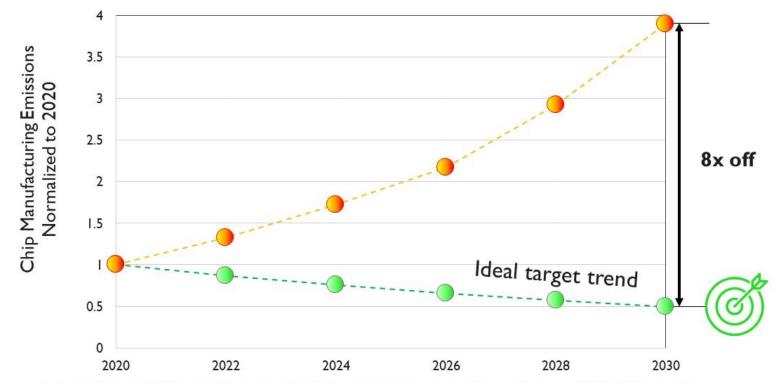

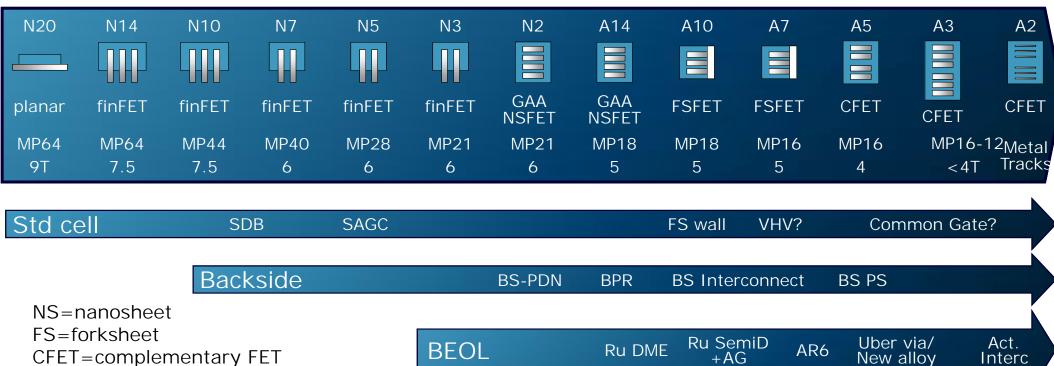

#### New device architectures to extend scaling

Source: 2023 IRDS Roadmap

### Logic scaling roadmap

CMOS 2.0

CFET=complementary FET

MP=metal pitch

BS=backside

AUC=array under CMOS

9

AuC

Interc

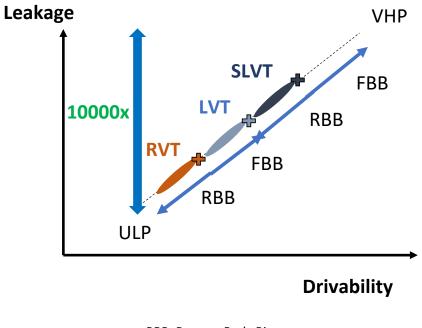

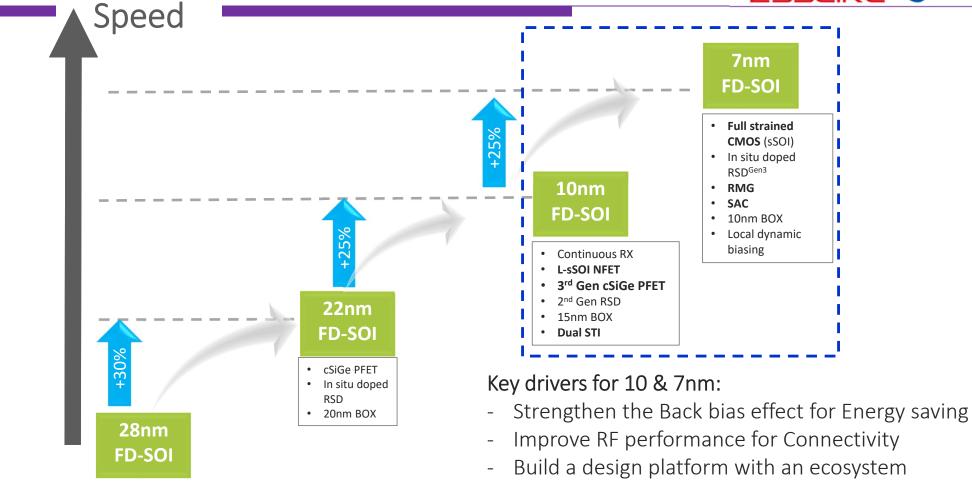

### **FD-SOI** Technology

|                              | 22FDX               | 14nm<br>FInFET | 28nm<br>Bulk | 45nm<br>PDSOI |

|------------------------------|---------------------|----------------|--------------|---------------|

| f <sub>T</sub> n-FET [GHz]   | 347                 | 314            | 310          | 296           |

| f <sub>max</sub> n-FET [GHz] | 371                 | 180            | 161          | 342           |

| f⊤ p-FET [GHz]               | 242<br>275 (mmWave) | 285            | 185          | -             |

| f <sub>max</sub> p-FET [GHz] | 288<br>299 (mmWave) | 140            | 104          | -             |

RBB: Reverse Body Bias FBB: Forward Body Bias ULP: Ultra-Low Power VHP: Very High Performance

# **FD-SOI** Roadmap

Name & Surname

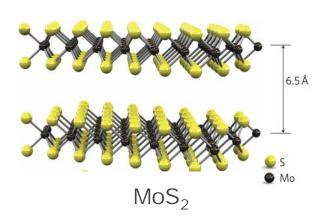

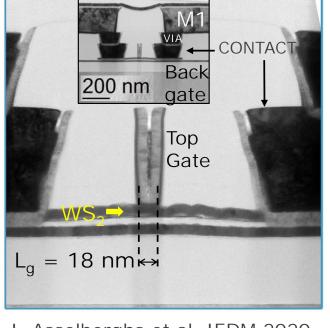

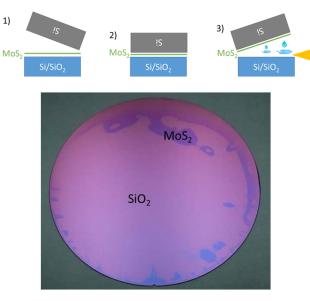

ESSDERC/ESSCIRC 2023 Workshop European Strengths and Gaps in Emerging Semiconductor Technologies 2D Atomic Channels: Next generation logic devices

Monolayer channel thickness enables gate length scaling while keeping high performance

300mm Flow

I. Asselberghs et al, IEDM 2020

Layer Transfer:

CEA-Leti, un-published

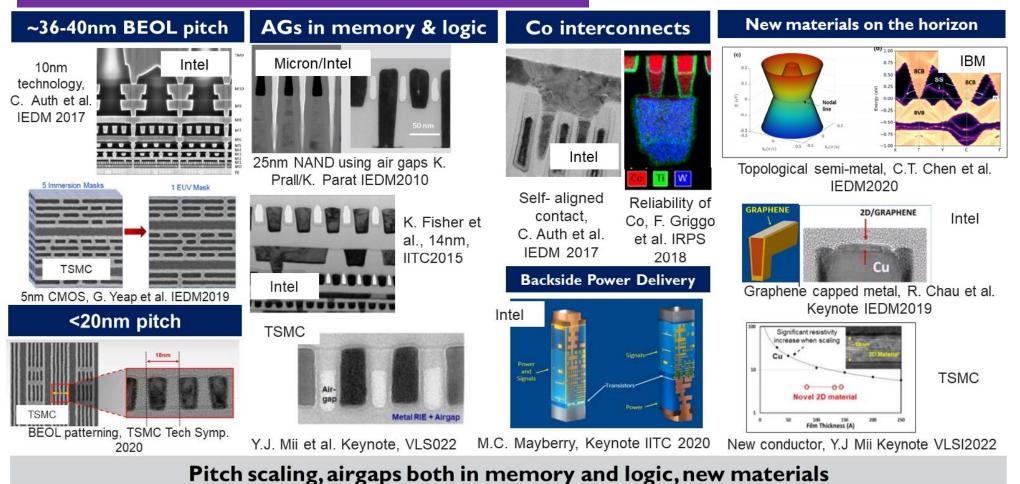

# Industry BEOL trends

Courtesy: Zsolt Tokei (imec)

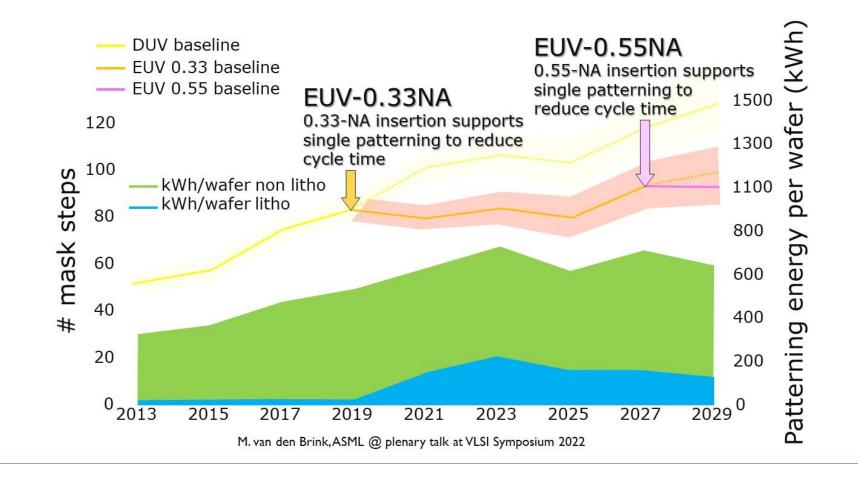

#### EUV lithography key enabler for scaling

#### Emerging Non-Volatile Memories

|                      | NOR FLASH                         | MRAM                              | PCRAM           | OxRAM                                           | FeRAM (PZT)        | FeRAM (HfO <sub>2</sub> )                                                        |

|----------------------|-----------------------------------|-----------------------------------|-----------------|-------------------------------------------------|--------------------|----------------------------------------------------------------------------------|

| Programming<br>power | ~200pJ/bit                        | ~20pJ/bit                         | ~300pJ/bit      | ~100pJ/bit                                      | ~10fJ/bit          | ~10fJ/bit                                                                        |

| Write speed          | 20 µs                             | 20 ns                             | 10-100 ns       | 10-100 ns                                       | <100ns             | 14ns @ 2.5V<br>(SONY)<br>4ns @ 4.8V (LETI)                                       |

| Endurance            | 10 <sup>5</sup> - 10 <sup>6</sup> | 10 <sup>6-</sup> 10 <sup>15</sup> | 10 <sup>8</sup> | 10 <sup>5</sup> – 10 <sup>6</sup> on 16<br>kbit | > 10 <sup>15</sup> | > 10 <sup>11</sup> single device<br>10 <sup>6</sup> - 10 <sup>7</sup> on 16 kbit |

| Retention            | > 125°C                           | 85°C - 165 °C                     | 165°C           | > 150°C                                         | 125°C              | 125°C                                                                            |

| Extra masks          | Very high (>10)                   | Limited (3-5)                     | Limited (3-5)   | Low (2)                                         | Low (2)            | Low (2)                                                                          |

| <b>Process flow</b>  | Complex                           | Medium                            | Medium          | Simple                                          | Simple             | Simple                                                                           |

| Multi-Level Cell     | Yes                               | No                                | Yes             | Yes                                             | No                 | No                                                                               |

| Scalability          | Bad                               | Medium                            | High            | High                                            | Medium             | Poor (2D)<br>High (3D)                                                           |

Memory activity focus on embedded NVM for NOR flash replacement

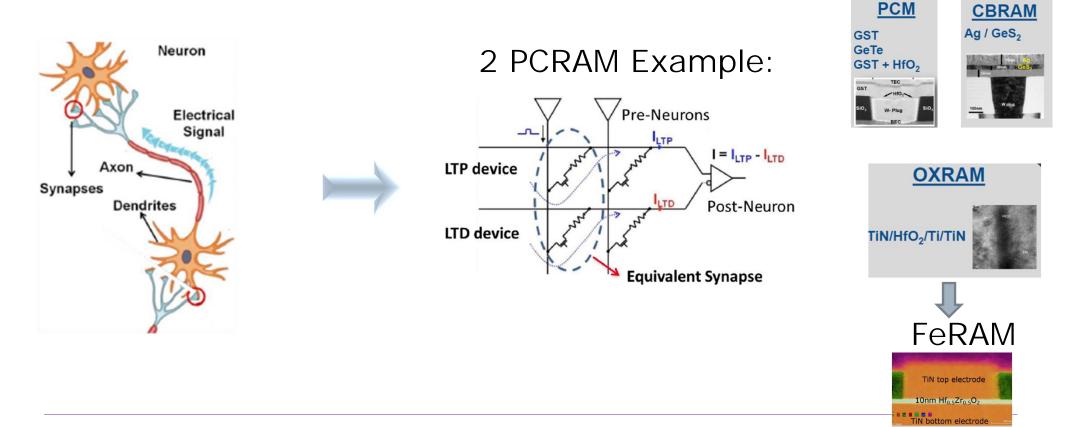

#### Neuromorphic based RRAM circuit

#### M. Suri et al, IEDM 2011.

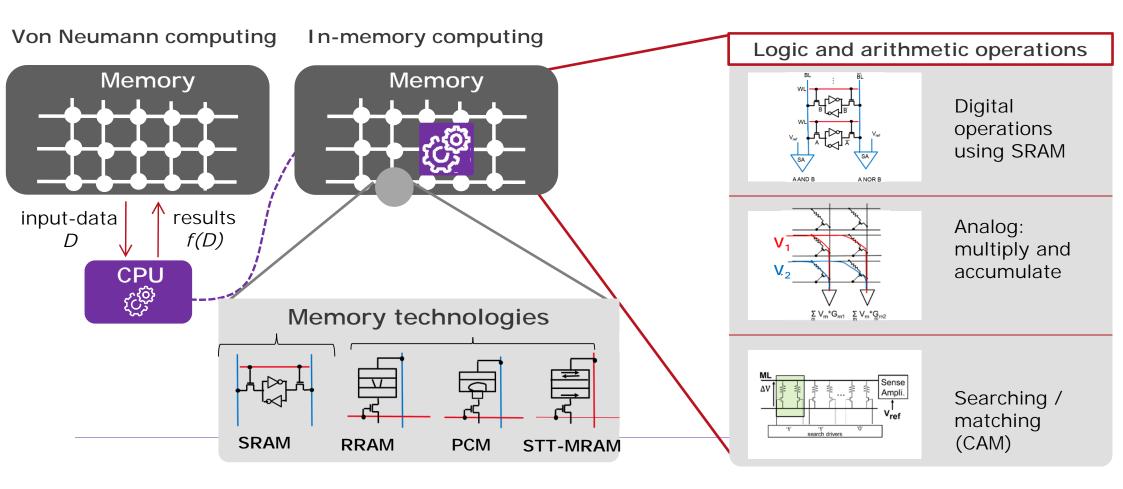

#### In memory computing

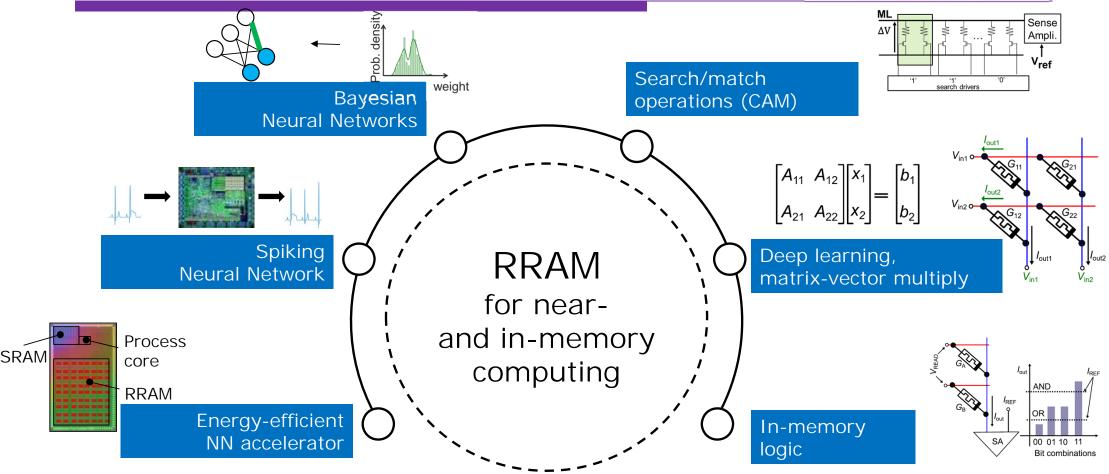

#### Near- & in-memory computing

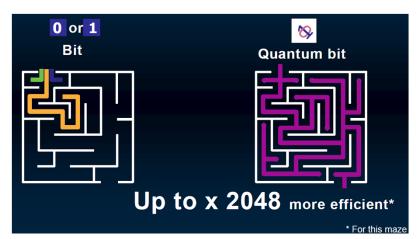

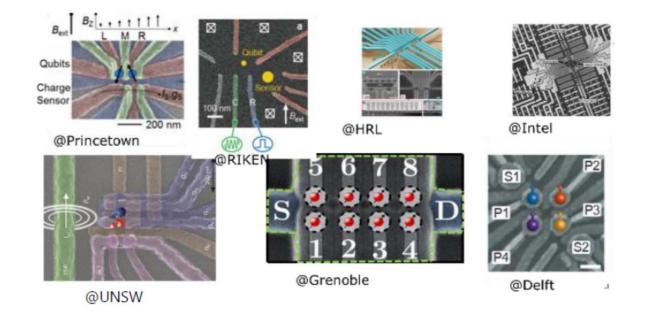

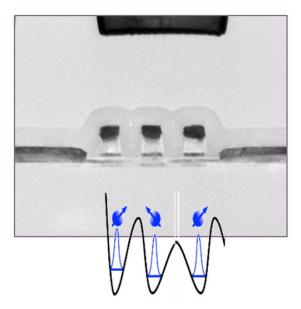

### From bits to q-bits

#### Quantum Physics to compute

|                     | Superconductor | Si spin qubit       | Trapped ion | Photon                           |

|---------------------|----------------|---------------------|-------------|----------------------------------|

| Size*               | (100µm)²       | (100nm)²            | (1mm)²      | ~(100µm)²                        |

| 1qubit fidelity     | 99.96%         | 99.93%              | 99.98%      |                                  |

| 2qubit fidelity     | ~99.3%         | >99%                | 99.9%       | 50% (measurement)<br>98% (gates) |

| Speed**             | 12-400 ns      | ~1 µs               | 100 µs      | 1 ms                             |

| Variability         | 3%             | 0.1%-0.5%           | 0.01%       | 0.5%                             |

| T° of operation     | 15mK           | 1K                  | 10K         | 4K/10K                           |

| Entangled<br>qubits | 433 (IBM)      | 3 (TU) (6 - QuTech) | 32 (IonQ)   | 70 (Pan-China)                   |

|                     |                |                     |             |                                  |

# From bits to q-bits

#### Quantum Physics to compute

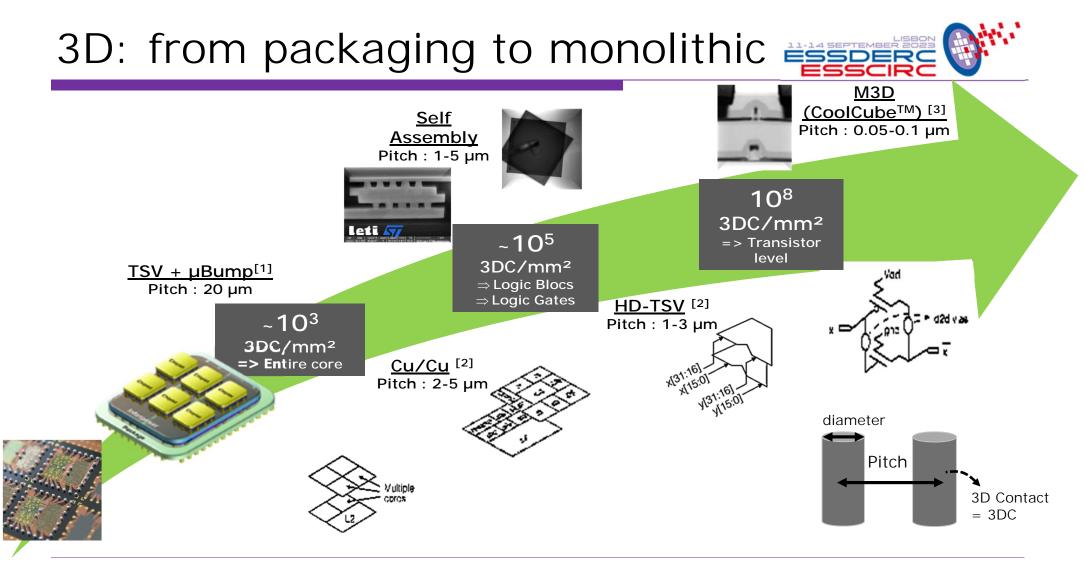

#### Chiplets: the new IC design paradigm

Up to 100x gain on Power Efficiency with 3D

[1] Cheramy, S., et al. "Advanced Silicon Interposer", C2MI Workshop, 2015

[2] Patti, B., "Implementing 2.5D and 3D Devices", In AIDA workshop in Roma, 2013

[3] Batude, P., et al. "3DVLSI with CoolCube process: An alternative path to scaling ." VLSI technology symposium 2015

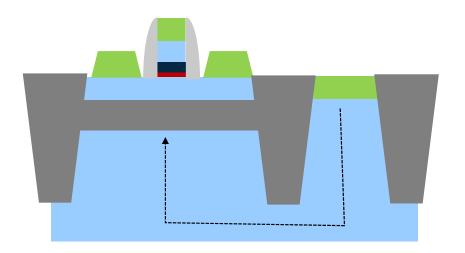

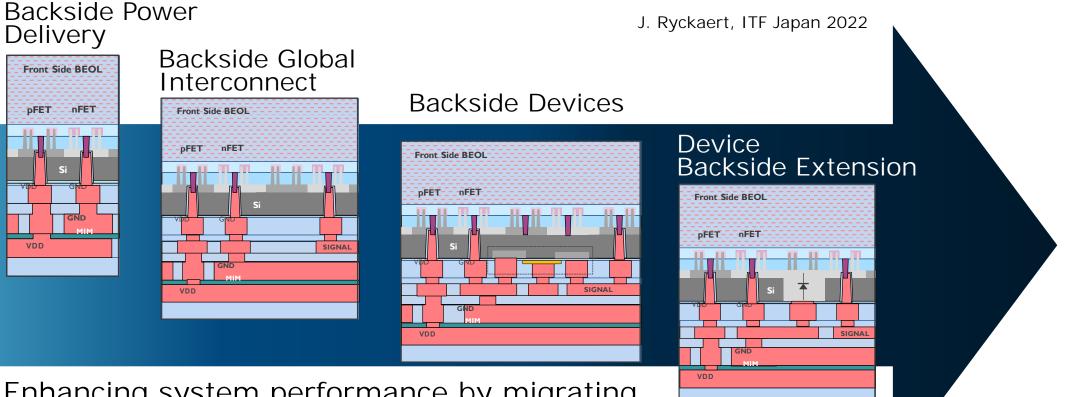

#### Towards a functional backside

Enhancing system performance by migrating system functions to the backside

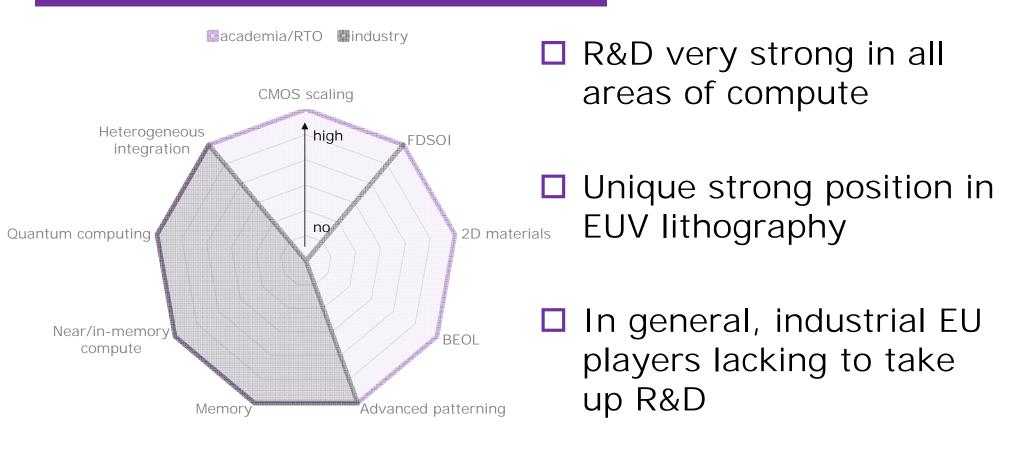

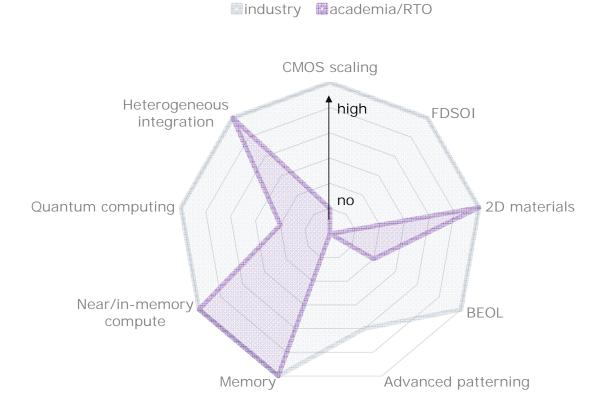

### EU and non-EU actors - EU

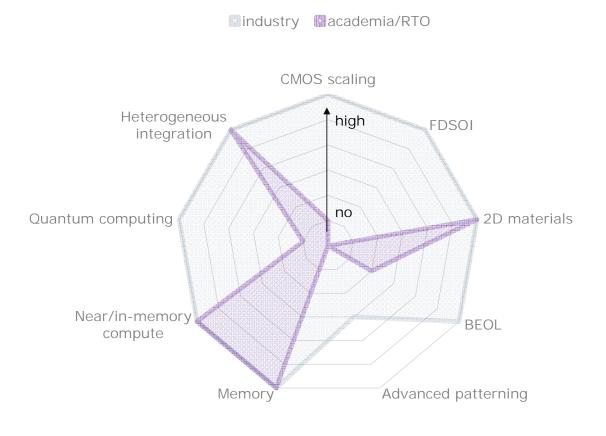

### EU and non-EU actors - US

Strong industrial activity in most areas of compute

Weaker academic activity on traditional logic scaling

Strong R&D in new materials, heterogeneous integration and memory

### EU and non-EU actors - Asia

- Very similar to US

- Strong industrial activity in most areas of compute

- Weaker academic activity on traditional logic scaling

- Strong R&D in new materials, heterogeneous integration and memory

### Summary

- □ Europe is very strong in R&D in all advanced compute areas

- Manufacturing: starting to catch up- Intel and TSMC's initiatives in Germany

- Lack of Fabless companies that drive the needs in terms of advanced compute

- Strong initiatives in EU in start-up company creation. Maybe a solution?