# Chips Acts and IRDS Building Tillars and Bridges over Valleys of Death

Paolo Gargini

Chairman IRDS

Life-Fellow IEEE, Fellow I-JSAP

Former Intel Fellow and

Director of Technology Strategy (1978-2012)

2023

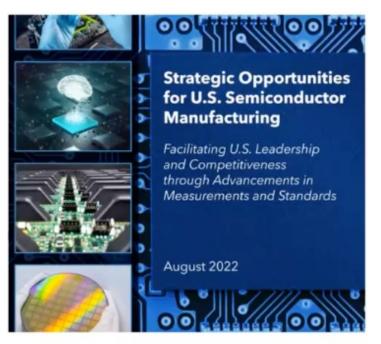

## A Message from Dr, Laurie Locascio Director of NIST and Undersecretary of Commerce

The US CHIPS R&D program looks forward to explore opportunities to cooperate with allied and partner nations on semiconductor technology innovation. We see value where Interest in technology roadmaps and grand challenges might align.

# The Script

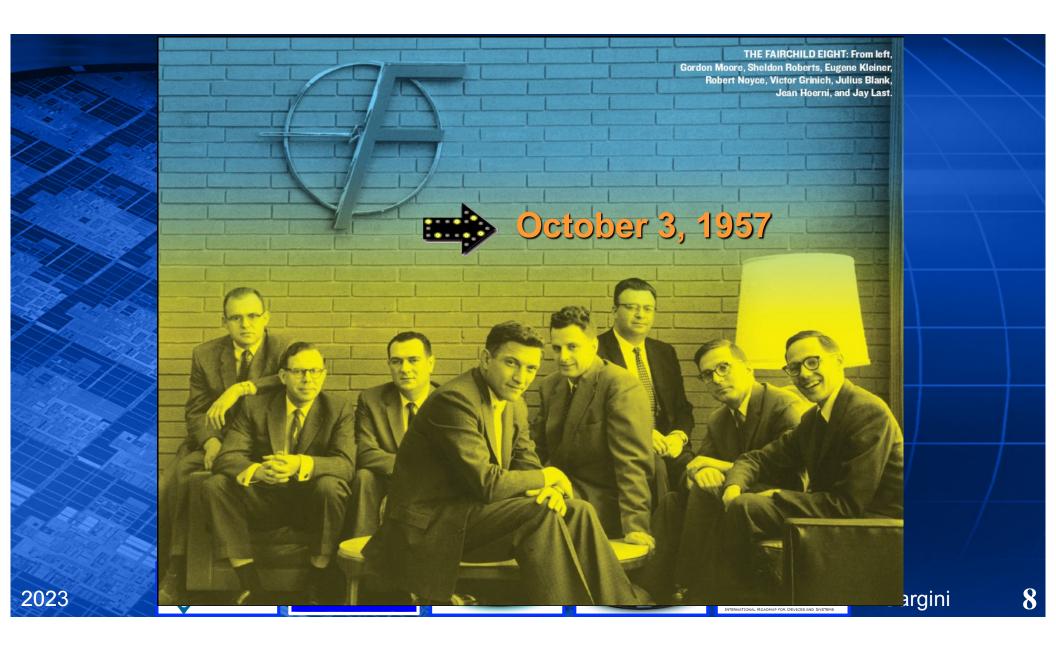

■ 1957: Act 1

■ 1987: Act 2

■ 1997: Act 3

■ 2020: Act 4

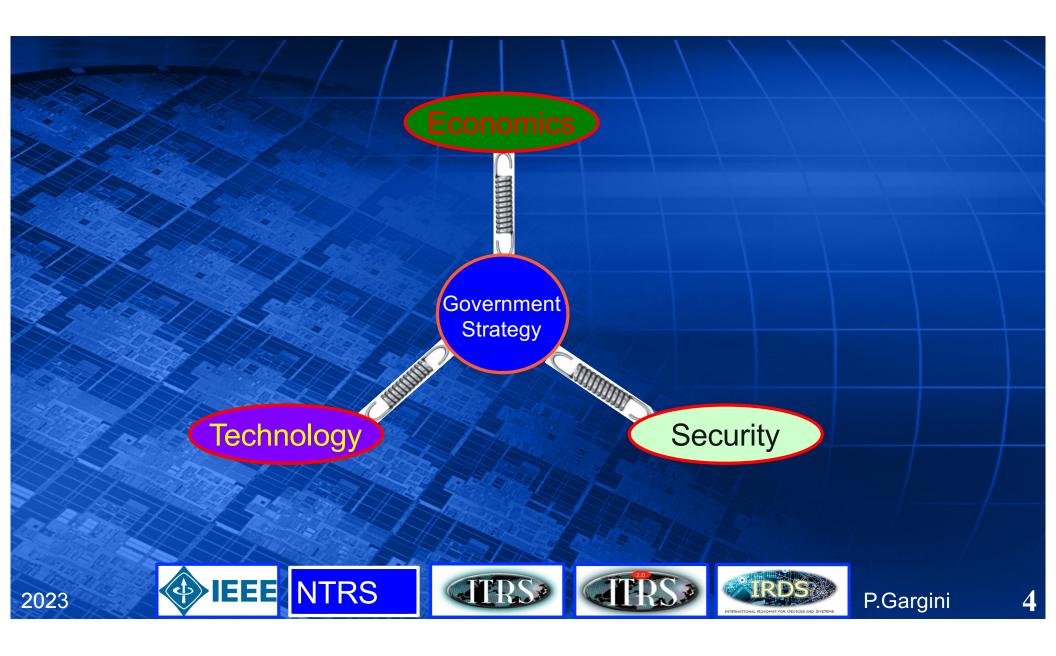

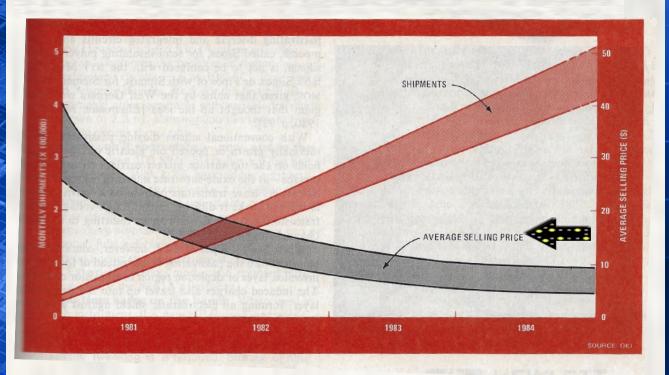

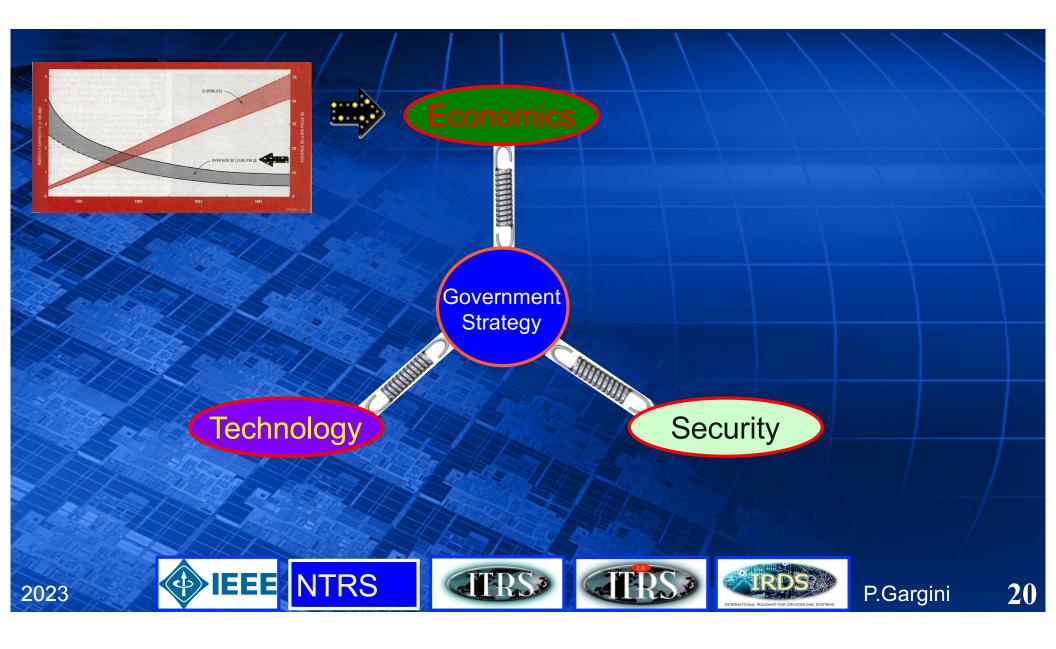

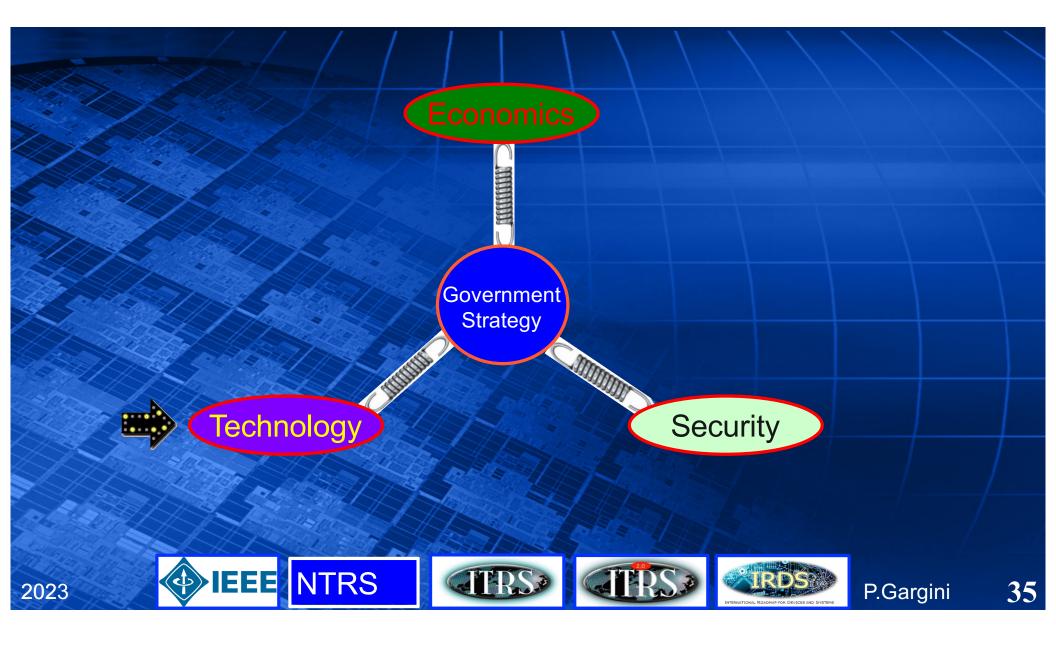

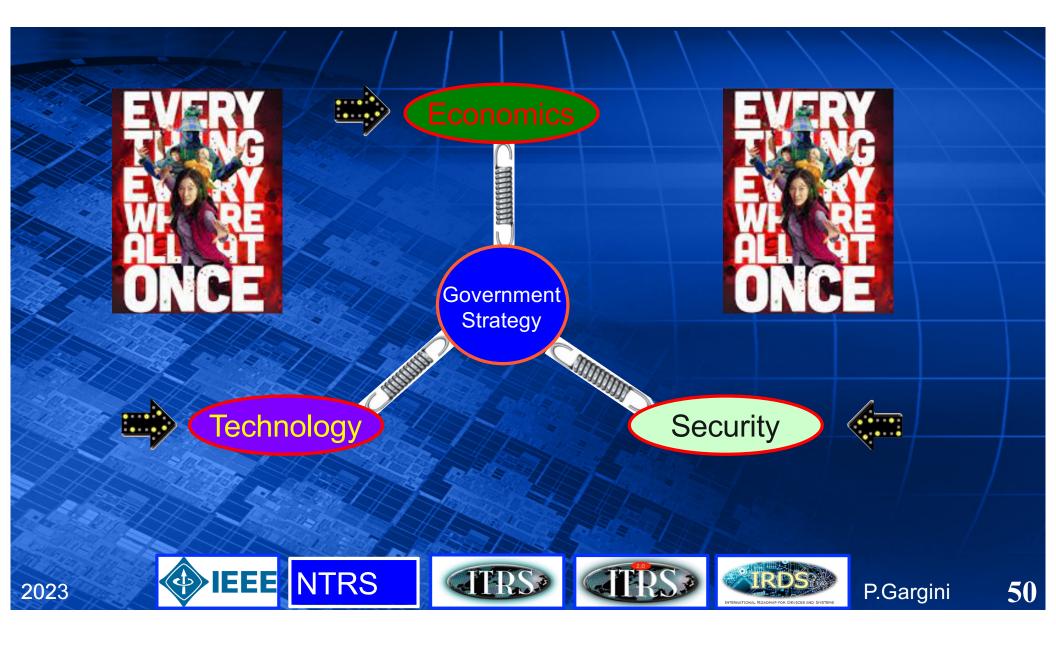

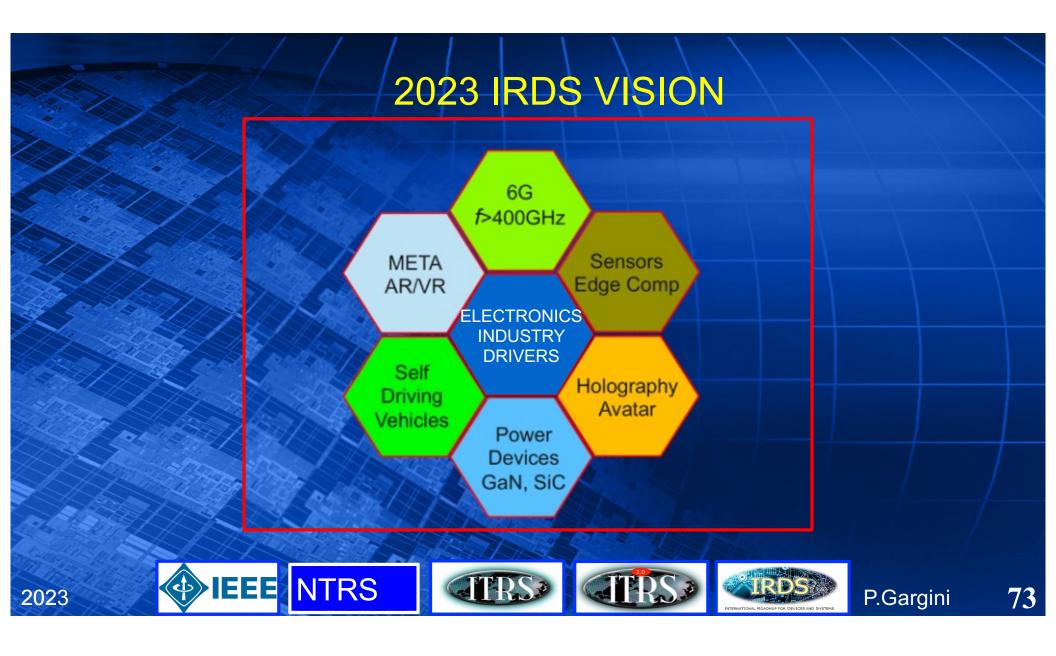

## **Electronics Industry Drivers**

### Economic Success

Obtain the maximum return with the smallest possible investment (e.g., most Companies)

## Technology Leadership

Master the most advanced technology no matter how much it costs (i.e., first man on the Moon)

### Security Requirements

Keep the most advanced technology completely exclusive (i.e., many governments)

These requirements are completely inconsistent with each other

P. Gargini

Origins

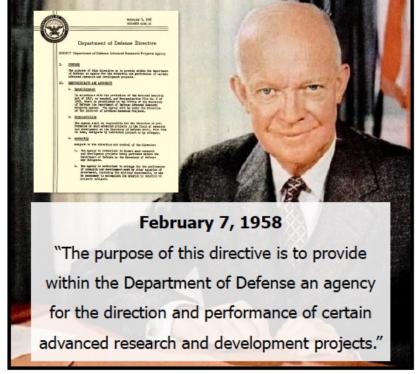

### Defense Advanced Research Projects Agency

## IBM selected Intel and Microsoft for PC (August 1980-August 1981)

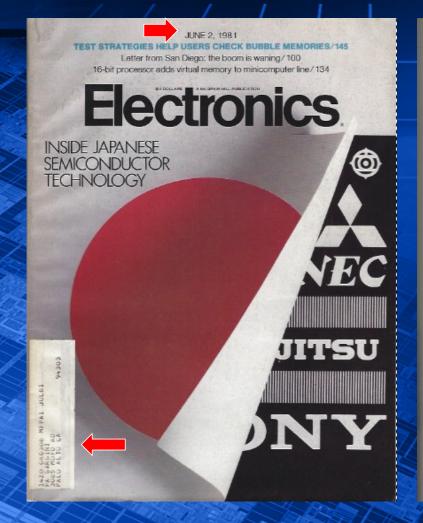

Beneath the facade of Japan Inc. lie individual companies, each with its own marketing strategies and technological strengths

by John G. Posa, soud State Editor

Given a small land mass, a large population, and few natural resources, Japan's relentless drive to produce and export are understandable. And since one of her few resources is the skill and ingenuity of her inhabitants, the decision to develop strong semiconductor and computer industries, in which intelligence and dedication count for so much, was probably inevitable.

dedication count for so much, was probably inevitable.

By now the success of Japan's semiconductor makers on the

world market is significant and has U. S. electronics manufacturers thoroughly alarmed, particularly when they view it in the

light of her stated national goal: dominance of the world computer market by 1985. For the impression on this side of the Pacific

is that Japan's chip makers are united in a monolithic drive to

topple U. S. integrated-circuit and computer builders, with IBM

is that Japan's chip makers are united in a monolithic drive to topple U.S. integrated-circuit and computer builders, with IBM Corp. as the ultimate target.

A closer view of the situation reveals a rather different state of affairs, however, and one that U.S. companies could find it helpful to understand. Not only are Japanese semiconductor makers distinctive in technology and market strategy, but further they compete vigorously among themselves.

makers distinctive in technology and market strategy, be further, they compete vigorously among themselves.

The fact is, Japan has no semiconductor companies, as such. At least, there are no large companies in Japan formed for the express purpose of manufacturing semiconductor devices. In other words, Intel Corp., Advanced Micro Devices Inc., and Mostek Corp. have no exact counterpart on the other side of the Pacific.

Rather, Japan's top 10 chip makers (Fig. 1) are all divisions of system houses. All were begun as service institutions to supply the internal needs of manufacturers of consumer products and data-processing or heavy equipment. Missubishi Electric Corp., for instance, is an enormous conglomerate with over 40 factories responsible for environmental control equipment, elevators, and linear accelerators, in addition to ICs.

It is true that the Japanese government has tried to unify Japan's IC makers, but that effort has not been as successful as generally believed. In the mid-1960s, Japan's Ministry of

Electronics / June 2, 1981

NTRS

'Until about three or four years ago, our main purpose was internal supply,' Oki says. Now more than 80% of its semiconductor sales are external.

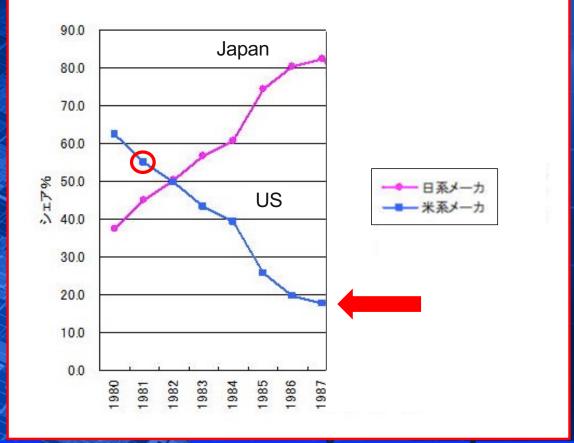

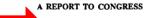

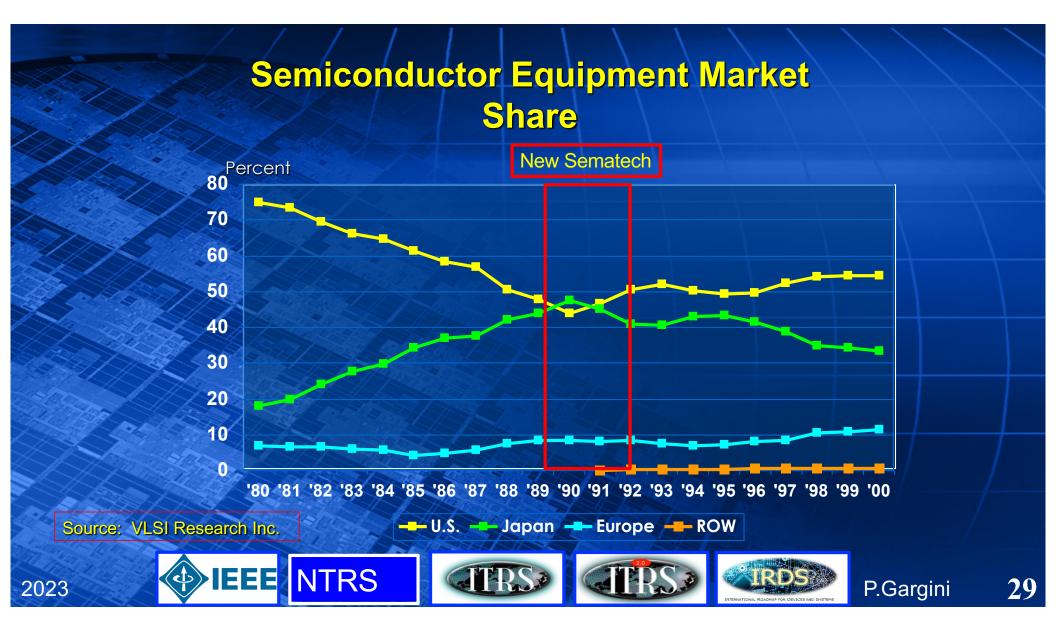

## **US-Japan Semiconductor Actual Market Share**

## Semiconductor Equipment Market **Share**

P.Gargini

# **Sematech Objectives**

This report is submitted on behalf of the Advisory Council on Federal Participation in SEMATECH. As required by law, the report provides an assessment of the progress of SEMATECH in its first year of operation.

Established by the National Defense Authorization Act for Fiscal Years 1988 and 1989 and further directed by the Omnibus Trade and Competitiveness Act of 1988, the Advisory Council is charged with reviewing SEMATECH operations and assessing continued federal participation.

#### Strategic Objectives

O Developing and Disseminating Advanced Manufacturing

Technology. SEMATECH's strategic plan calls for highyield, factory-scale application of 0.35-micron production technology in SEMATECH's own fabricating facility

("fab") by 1993--an estimated six to twelve months ahead

leading foreign chipmakers, and three years ahead of most

U.S. merchant firms (without SEMATECH).\* The resulting

commercial advantage for SEMATECH's members could be

substantial.

# **Correct Problem Statement**

- US and Japanese companies had at the time the same technology capabilities

- 2. Japanese equipment was superior in quality, accuracy and reliability to US equipment

- 3. Manufacturing methods of Japanese companies were superior to US

| Yields in percent |       |      |      |      |      |      |      |  |  |  |

|-------------------|-------|------|------|------|------|------|------|--|--|--|

|                   | Yield |      |      |      |      |      |      |  |  |  |

| Country           | 1981  | 1986 | 1987 | 1988 | 1989 | 1990 | 1991 |  |  |  |

| United States     | 55    | 60   | 60   | 67   | 74   | 80   | 84   |  |  |  |

| Japan             | 45    | 75   | 79   | 81   | 85   | 89   | 93   |  |  |  |

Source: VLSI Research.

# Cramming more components onto integrated circuits

With unit cost falling as the number of components per circuit rises, by 1975 economics may dictate squeezing as many as 65,000 components on a single silicon chip

By Gordon E. Moore

Director, Research and Development Laboratories, Fairchild Semiconductor division of Fairchild Camera and Instrument Corp.

#### VI. INCREASING THE YIELD

There is no fundamental obstacle to achieving device yields of 100%. At present, packaging costs so far exceed the cost of the semiconductor structure itself that there is no incentive to improve yields, but they can be raised as high as is economically justified. No barrier exists comparable to the thermodynamic equilibrium considerations that often limit yields in chemical reactions; it is not even necessary to do any fundamental research or to replace present processes. Only the engineering effort is needed

Electronics, Volume 38, Number 8, April 19, 1965

# **Scaling Continues beyond Imagination**

| Production   | 1989 | 1991 | 1993 | 1995 | 1997 | 1999 |

|--------------|------|------|------|------|------|------|

| Generation   | 1.00 | 0.80 | 0.50 | 0.35 | 0.25 | 0.18 |

| Gate Length  | 1.00 | 0.80 | 0.50 | 0.35 | 0.20 | 0.13 |

| SRAM Cell    | 220  | 111  | 44   | 21   | 10.6 | 5.6  |

| Power Supply | 5.0  | 5.0  | 3.3  | 2.5  | 1.8  | 1.5  |

| # Metal      | 2    | 3    | 4    | 4    | 5    | 6    |

| DA STATE     |      | int  |      |      |      |      |

New generation every 2 years

#### ADVISORY COUNCIL ON FEDERAL PARTICIPATION IN SEMATECH

John A. Betti Under Secretary of Defense for Acquisitions Chairman

#### SEMATECH 1990

May 1990

Report Directed by:

Michael R. Darby

Under Secretary for

Economic Affairs U. S. Department of Commerce

Author:

Jeffrey L. Mayer Director Office of Policy Analysis

Policy and Research Support: Robert McKibben Jane W. Molloy Gerald Moody K. Peter Wagner

#### SEMATECH 1990

#### A REPORT TO CONGRESS

### May 1990

SEMATECH assigns the highest priority and the largest share of its resources to projects aimed at averting potentially dangerous (i.e., "show-stopping") dependence on foreign suppliers for key manufacturing tools. Second highest priority goes to projects that accelerate technology development in cases where earlier access to advanced equipment, materials, or process (i.e., "key enablers") would confer a significant competitive advantage. Third place goes to high-risk/high-return projects that individual firms might not tackle on their own. In effect, these three criteria define the areas of SEMATECH's comparative advantage as a cooperative venture.

Weakness in the Supply Base. Weakness in the U.S. semiconductor manufacturing equipment and materials industries creates a competitive vulnerability for U.S. chipmakers. Success in world semiconductor markets depends on rapid growth in production efficiency and getting to market early in the product cycle. These objectives demand close relations between the chipmakers and their suppliers including the sharing of proprietary equipment and device designs and marketing strategies, and early testing and refinement of prototype tools in production settings.

## **Revised Sematech Mission**

Mission. In operational terms, SEMATECH's current mission statement ("To Provide the U.S. Semiconductor Industry the Domestic Capability for World Leadership in Manufacturing") is a commitment to sustain or create at least one world-class U.S. producer in each major category of chipmaking equipment The strategic objective for SEMATECH's members as a group, which none has the capacity to achieve alone, is freedom from the potential dangers of dependence on foreign sources of supply.

SEMATECH assigns the highest priority and the largest share of its resources to projects aimed at averting potentially dangerous (i.e., "show-stopping") dependence on foreign suppliers for key manufacturing tools. Second highest priority goes to projects that accelerate technology development in cases where earlier access to advanced equipment, materials, or process (i.e., "key enablers") would confer a significant competitive advantage. Third place goes to high-risk/high-return projects that individual firms might not tackle on their own. In effect, these three criteria define the areas of SEMATECH's comparative advantage as a cooperative venture.

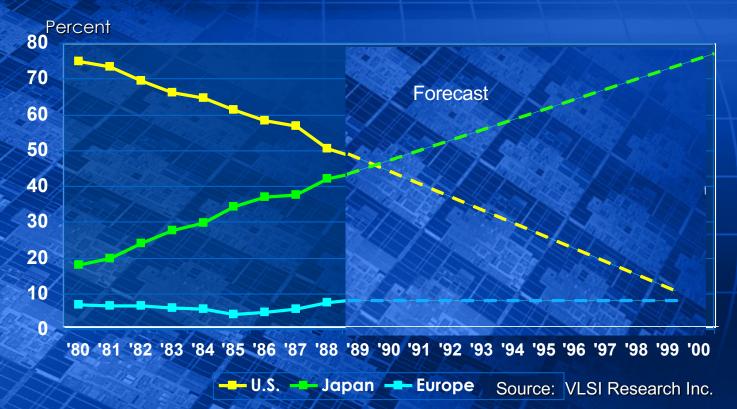

## **Semiconductor Market Share**

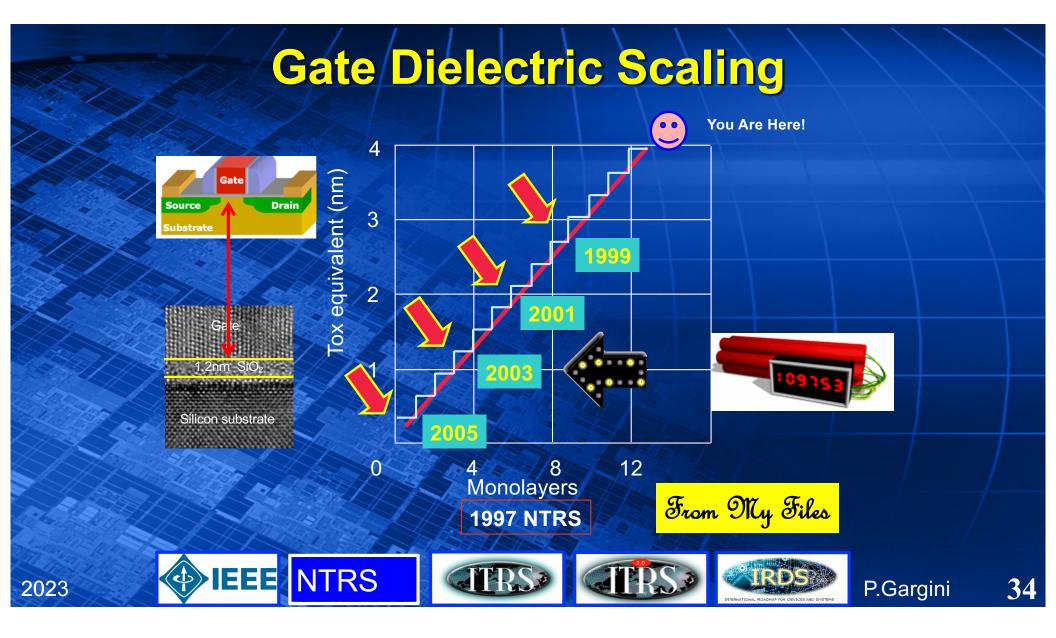

# FUNDAMENTAL LIMITATIONS IN MICROELECTRONICS—I. MOS TECHNOLOGY\*

B. HOENEISEN and C. A. MEAD California Institute of Technology, Pasadena, California 91109, U.S.A.

(Received 11 August 1971; in revised form 8 November 1971)

length cannot be made smaller than approximately two depletion regions thicknesses, or  $\approx 0.02 \mu m$ . Otherwise the two junctions would be in punch-through even with no applied bias.

The gate oxide thickness has a lower limit of ≈50Å determined by tunneling through the silicon dioxide energy gap. The isolation between gate and substrate is reduced for thinner oxides, since the oxide conductance per unit area increases exponentially with decreasing thickness [2].

# **ITRS 1.0**

Europe Japan Korea **Taiwan USA**

International Technology Roadmap for Semiconductors

1998

P.Gargini

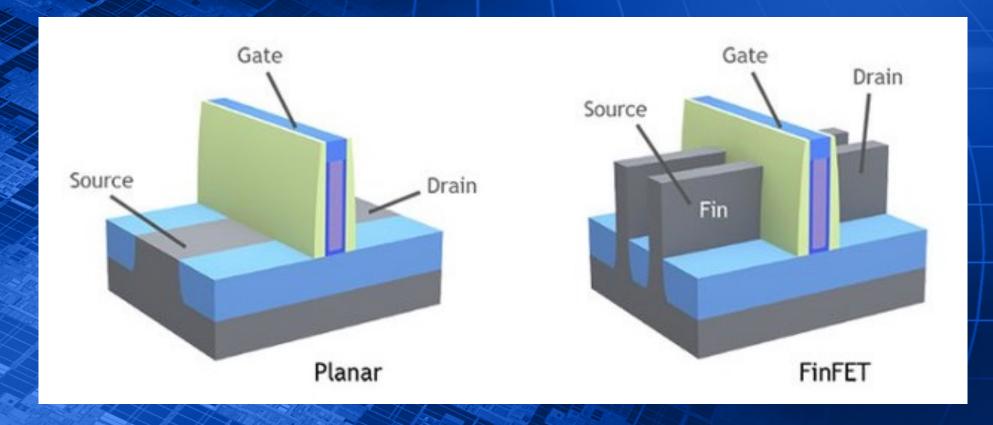

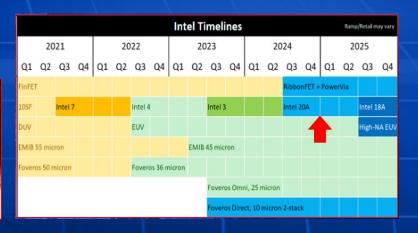

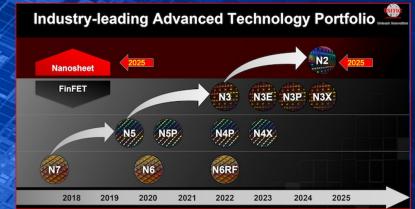

## 1965-2011: From Planar Transistor to FinFET

# IRDS

http://irds.ieee.org/

2015->2025-2040

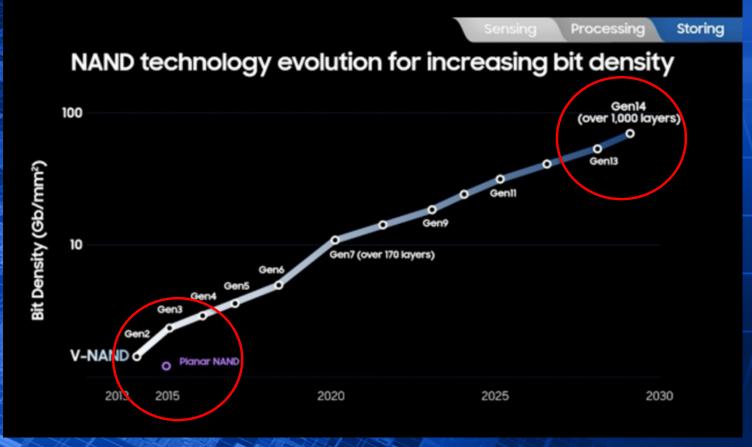

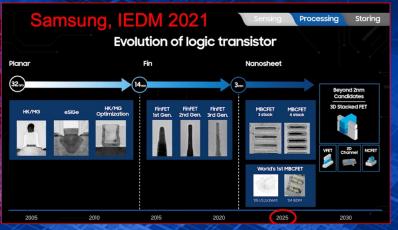

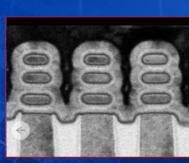

## Samsung, IEDM 2021

2015->2025-2040

## Gate All Around (GAA) by nanosheets technology in 2025

## Semiconductor Manufacturing Investments in US

#### CHIPS Act At A Glance

Creating Helpful Incentives to Produce Semiconductors for America (CHIPS Act)

\$52 billion total budget over 5 years

# Financial Incentives Programs

\$39 billion

#### **Research and Development**

\$11 billion

Technology Center Packaging Program MFG USA Institute(s) Metrology program

#### **Workforce Development**

US Code: 15 USC 4652: Semiconductor incentives

#### Next-Generation Microelectronics Manufacturing (NGMM)

National facility for 3DHI R&D and low-volume manufacturing

Users

#### **National facility**

Output

3DHI assembly design kit

3DHI: 3-dimensional heterogeneous integration

2023

Approved For Public Release; Distribution Unlimited

28

#### Heterogeneously integrated electronics – emerging opportunities

Materials Devices **Process Function** Bump, MOSFET, FinFET, μ-Bump, Logic, Memory Silicon Traditional Focus GAAFET TSV, Hybrid Bump, Analog, Mixed-Bi-CMOS, Silicon germanium --μ-Bump, Signal, RF **HBTs** TSV, Hybrid Bump, III-V, II-VI Laser, LED, Photonic μ-Bump, (GaAs, InP, HgCdTe) Detector TSV, Hybrid Emerging Opportunit Bump, Wide bandgap Photonics, RF, HEMT, MESFET, μ-Bump, (GaN, SiC) Power **JFET** TSV, Hybrid Bump, Ultrawide bandgap HEMT, MESFET, Photonics, μ-Bump, (AlGaN, Diamond) **JFET** Power TSV, Hybrid NGMM will enable heterogeneous integration of different material systems in the same package

25

#### CHIPS for America Incentives

#### \$39 billion for manufacturing

- Incentivize expansion of manufacturing capacity for semiconductors

- Attract large-scale investments in advanced technologies such as leadingedge logic and memory

- Advance U.S. technical leadership

- NDAA Section 9902

#### \$11 billion for R&D

- National Semiconductor **Technology Center**

- National Advanced Packaging Manufacturing Program

- Manufacturing USA institute(s)

- · National Institute of Standards and Technology measurement science

- NDAA Section 9906

Together with CHIPS initiatives from other agencies, including DOD, State, NSF, and Treasury

Workforce development

## **Research & Development**

CHIPS

- Strengthen and advance U.S. leadership in R&D

- An integrated ecosystem that drives innovation

- In partnership with industry, academia, government, and allies

- A strategic view of R&D infrastructure, participant value-proposition, and technology focus areas

- Informed by the Industrial Advisory Committee

## National Semiconductor Technology Center

Vision: Will serve as the focal point for research and engineering throughout the semiconductor ecosystem, advancing and enabling disruptive innovation to provide U.S. leadership in the industries of the future.

**Structure**: A public-private consortium as an independent entity with a governing board informed and advised by industry, academia, government, and key stakeholders.

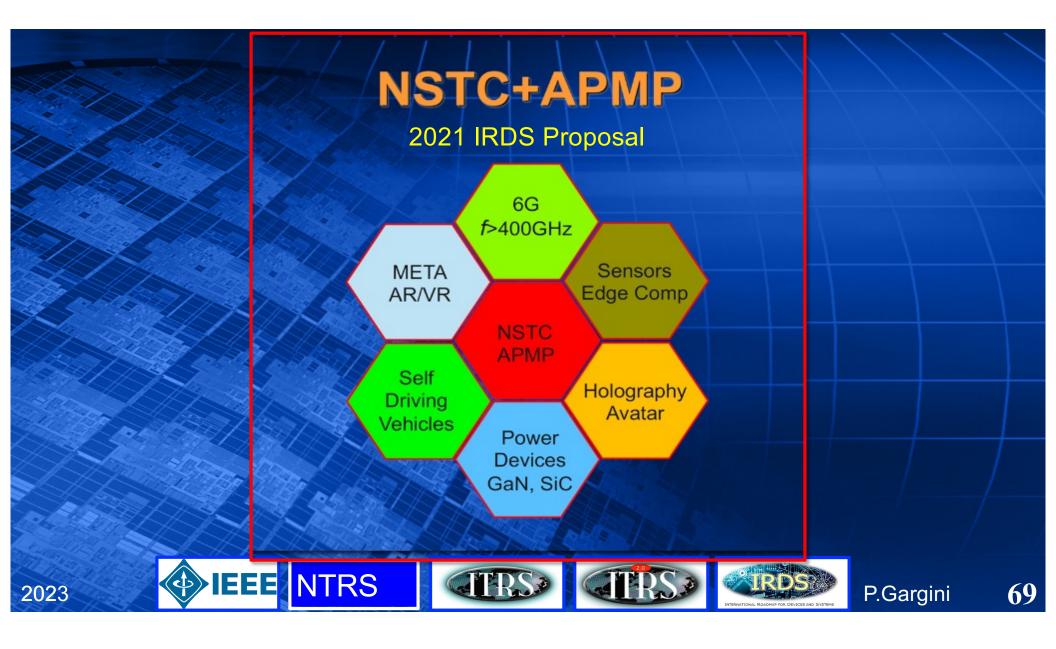

## National Advanced Packaging Manufacturing Program

- Strengthen semiconductor advanced test, assembly, and packaging capability in the domestic ecosystem

- Leverage public-private partnerships, that can include support for facilities managed by the NSTC and MUSA

- · Broad range of technologies:

- · Heterogeneous integration

- Wafer and panel-based approaches

- Tooling and automation

- Substrate technology

## Manufacturing USA Institute(s)

- Up to three new public-private partnership institutes in the Manufacturing USA network

- To advance research and commercialization of semiconductor manufacturing technologies

- Pre-competitive collaboration among researchers and manufacturers

- Ex: Virtualization, simulation, and automation; packaging

- Workforce training

## **NIST Metrology R&D**

- Measurement science for new materials and packaging

- Physical metrology for next-generation microelectronics

- Computation and data

- Virtualization and automation

- Reference materials and data, and calibrations

- Standards for processes, cybersecurity, and test methods

#### **IAC Working Groups**

#### **Technology**

#1 R&D Gaps

The charter of this working group is to look at the long term research needs of the semiconductor industry. The working group will then need to understand what is being funded by other initiatives, where the gaps are, and then suggest priorities to the IAC as to where the focus areas should be for CHIPS funding and the NSTC that provide the best opportunities to sustain US leadership in semiconductor innovation. (Chair: Dan Armbrust)

#### **Organization**

#2 Org & PPP

This working group will review and examine all the various funding sources for semiconductor R&D and map out the relationships between these entities to ensure spending efficiency and eliminate any overlaps. In addition, this working group will review the essential functions of the NSTC. Finally, this committee will review PPP proposals for both R&D partnerships, the value proposition for industry participation in PPPs, as well investment. (Chair: Deirdre Hanford)

#3 Workforce

#### **Workforce**

This working group will look at the workforce needs across the industry from high level R&D personnel to factory workers. They should review programs that will increase the interest and availability of the necessary skills for the US to lead the world in semiconductor R&D and manufacturing. (Chair: Tsu Jae King Liu)

## ▶ From Prototypes → Domestic Volume Manufacturing

**Recommendation 4-3:** The NSTC should offer prototyping enablement with a translation path to multiple domestic volume production sources, encompassing the spectrum from pre-competitive to private research program types. It should lower barriers to innovation and enable smaller entities to participate

NSTC should leverage COE capabilities and U.S. Shared Resource Network to facilitate transition to domestic manufacturing

# Prototyping Volume Manufacturing

#### Considerations:

- Baseline flows/PDKs to enable execution

- Provides value to large entities

- Accessible to small/mid size entities, start-ups

- Provides a pathway to volume manufacturing

IAC Organization / PPP Working Group - February 7, 2023 IAC meeting

#### Proposal

#### **NSTC Sustainable Business Model**

**Lesson from Act 1**

**Recommendation 4-2**: The NSTC should develop a sustainable business model, with increased funding by industry over time. Government funding should provide risk capital to facilitate broad participation of firms and research institutions of all sizes and means

Industry and Government must co-invest for the long term to ensure sustainability and ongoing success

#### Considerations:

- Successful PPPs strike a good balance between Industry and Government investment

- Sustained government investment ensures broad access (start-ups, universities, small businesses) and increased risk tolerance

- Sustained Industry investment ensures relevance and evergreen capabilities

- · Compared organizational models IMEC, SRC, SEMATECH, etc.

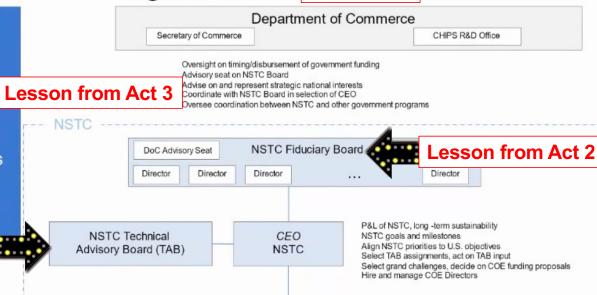

## NSTC PPP Organization

#### Proposal

Recommendation 4-1: The NSTC should be a leading and convening public private partnership, led by an independent CEO reporting to a fiduciary board, with the advice of a Technical Advisory Board (TAB).

The CEO oversees Multiple Coalitions of Excellence (COEs), each with an **Executive Director who oversees** specific work sectors

Lesson from Act 3

#### Considerations:

- · CEO appointment process

- · CEO authority & reporting structure

- · COE specialization areas

Director Coalition of Excellence (COE)

Director Coalition of Excellence (COE)

Director Coalition of Excellence (COE)

NSTC Affiliate COE

Director

Affiliate COE

IAC Organization / PPP Working Group - February 7, 2023 IAC meeting

Actual

NSF basic research DMREF, RINGS, others

DOE basic/early-stage research

SC, NNSA, EERE, ARPA-E, others

DOD early stage ERI 2.0, NGMM, SBIR, others

Other USG Agency SBIR, NASA, NIH, others

Private capital

Commercial R&D

International programs

Microelectronics Commons

Commercial technology with defense Implications

**NSTC**

Broad support for commercial technologies

**Private** capital

+ CHIPS Incentives

Commercial fabs, foundries

USG scaling programs NSF FuSe, DOE NNSA, other

and de-risking

Prototyping, scaling,

DARPA SHIP, DOD RAMP-C, DOE NNSA, others

Transition to market

Discovery and proof of concept

#### **NSTC OPERATING STRUCTURE**

Actual

#### **Member Advisors**

#### **NSTC Consortium**

## NSTC Operator Board of Trustees & Operator CEO

Headquarters

Administration

Research

Workforce programs

Venture Fund Member Services USG Relations Convenings CHIPS R&D Office

Funding, oversight,

support

#### **Technical Centers**

Examples: Prototyping facility, affiliated university lab, specialized equipment access, etc.

Affiliated facility

Affiliated facility

Affiliated facility

Advanced packaging facility (in coordination with NAPMP)

**NTRS**

#### **TECHNICAL CENTERS: COMMUNITY INPUT**

Actual

The semiconductor community has provided extensive input to the requirements for potential technical centers. The NSTC will embark on a prioritization process to ensure that the highest priority needs are met with the funds available. Identified needs for the NSTC to consider include:

Baseline CMOS (complementary metal-oxide semiconductor): Fully functional and supported CMOS process flow at 22 nm or below with a capacity of 10,000 wafer starts per month on 300 mm wafers

- CMOS R&D process: Front-end short loops supporting < 3 nm technology R&D at a capacity of 2,000 wafers per month using extreme ultraviolet technology enabling the development of leading-edge materials, devices, and process and metrology tools

- Manufacturing test vehicles that provide low-cost patterned and functional substrates that can be

used to provide data through electrical test, to enable materials, equipment, process, and device

development and optimization, especially for CMOS+X enabled technologies

- Extended metrology capacity to enable R&D in a production environment including rapid failure analysis to shorten prototype development cycles, extensive in-line process monitoring capabilities, and off-line characterization facilities

- Space and flexibility to accommodate next-generation or prototype processing and metrology tools so that they can be demonstrated in a production environment

- Back-end short loop processing from specialized capabilities enabling "fab-to-lab"<sup>24</sup> finishing of R&D devices and high-quality processing of novel materials and devices while maintaining process and material segregation

## **Beyond CMOS**

Power electronics: Power management devices often require non-silicon substrates (e.g., silicon carbide, gallium nitride) and specialized designs, tools, and processes

Radio frequency, mixed signal, and analog: Communication and sensing applications require diverse capabilities distinct from leading-edge CMOS

Photonics: Advancements in quantum, sensing, and interconnect are all possible at the intersection of light and electronics

Bioelectronics: The convergence of microfabrication and biotechnology brings new opportunities. but also increased complexity and significant integration challenges

Mature node: The NSTC may seek to have capacity at a mature node (e.g., 130 nm), with such a facility well suited to certain research programs and workforce education

Design tools: New design tools and methodologies to accelerate the generation of circuit IP; virtualize devices, circuits, and processes; and enable co-design, simulation, and heterogeneous integration

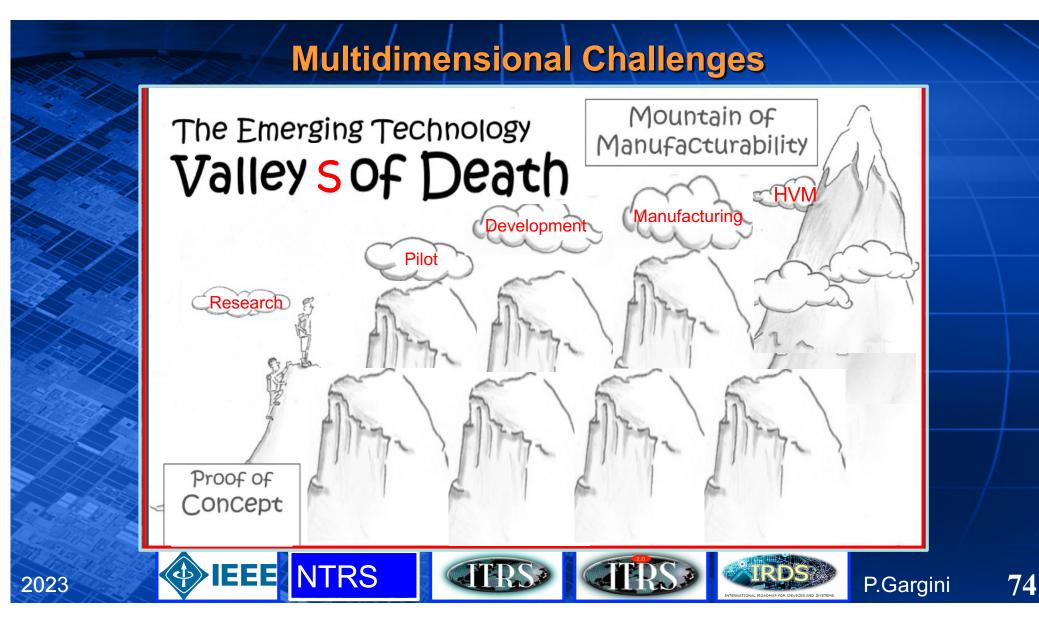

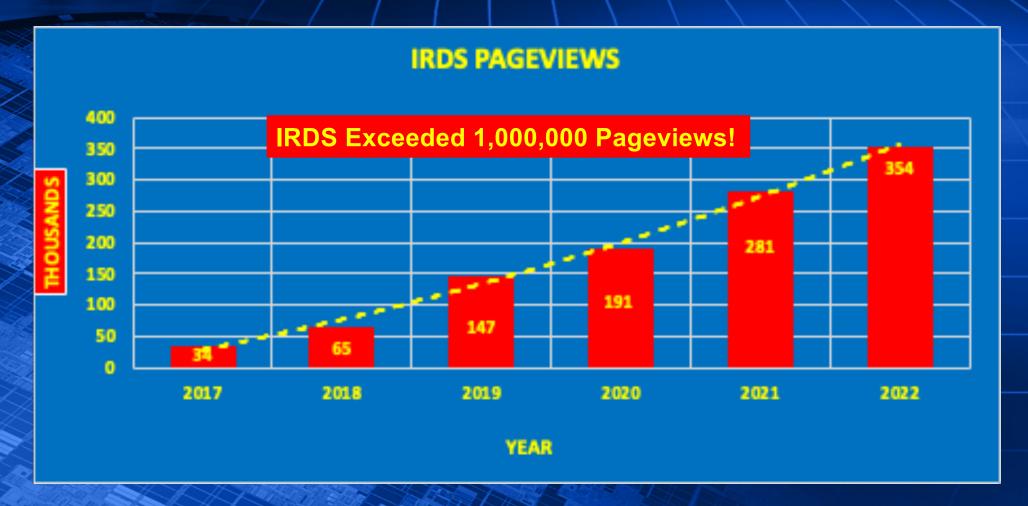

# **IRDS**

http://irds.ieee.org/

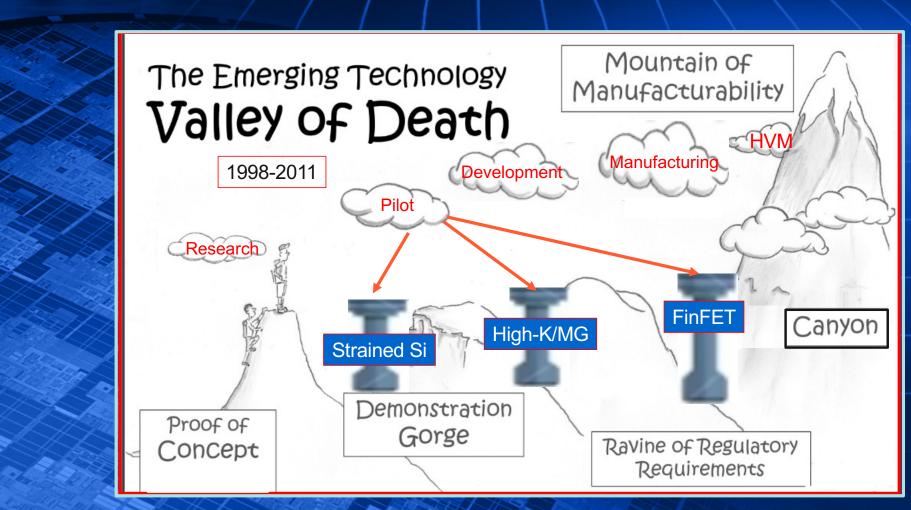

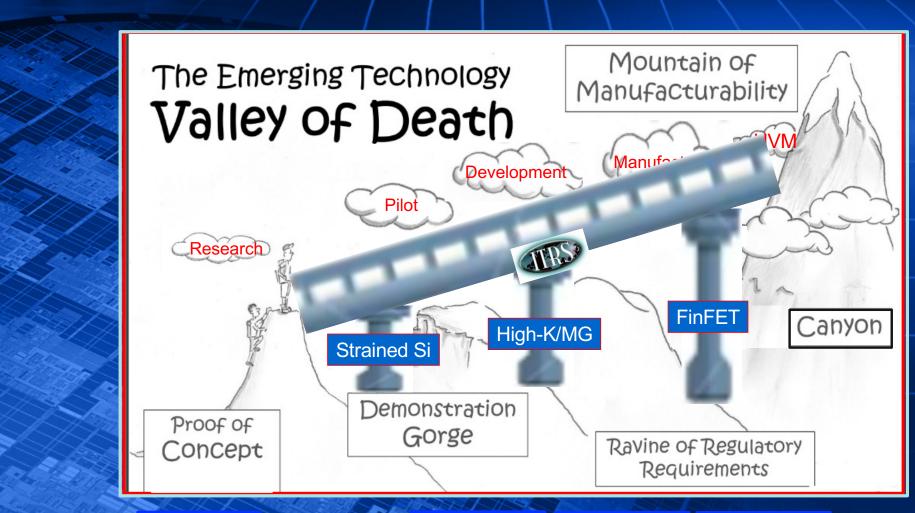

### **Multidimensional Bridges** Mountain of The Emerging Technology Manufacturability Valley sof Death HVN Manufacturing Development **Pilot** Research Proof of Concept NTRS TTRS JIPS: (A) IEEE 2023 P.Gargini

https://irds.ieee.org/editions/2023

P.Gargini