WORKSHOP – Sustainable Electronics & International Cooperation On Semiconductors

### Silicon Photonics: (a, b) current state, future evolution, and (c) trends

Dr. Abdul Rahim (Program Manager) ePIXfab – the European Silicon Photonics Alliance Ghent University, Belgium

WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors Name

#### ePIXfab - The European Silicon Photonics Alliance

#### ePIXfab's mission is to act as a catalyst for European academia and industry

to strengthen the worldwide silicon photonics ecosystem.

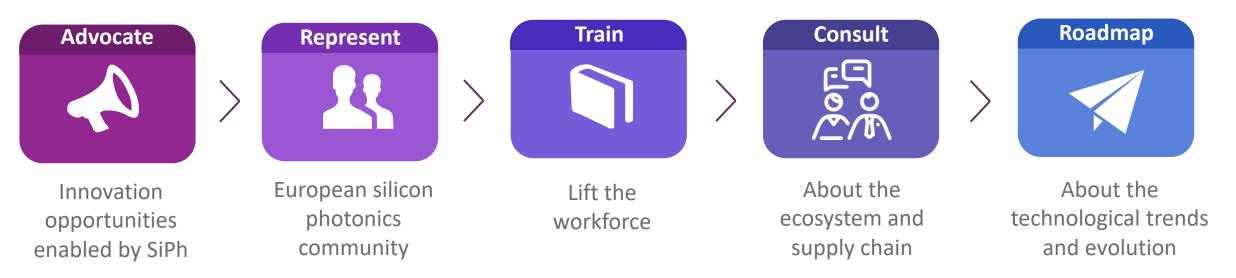

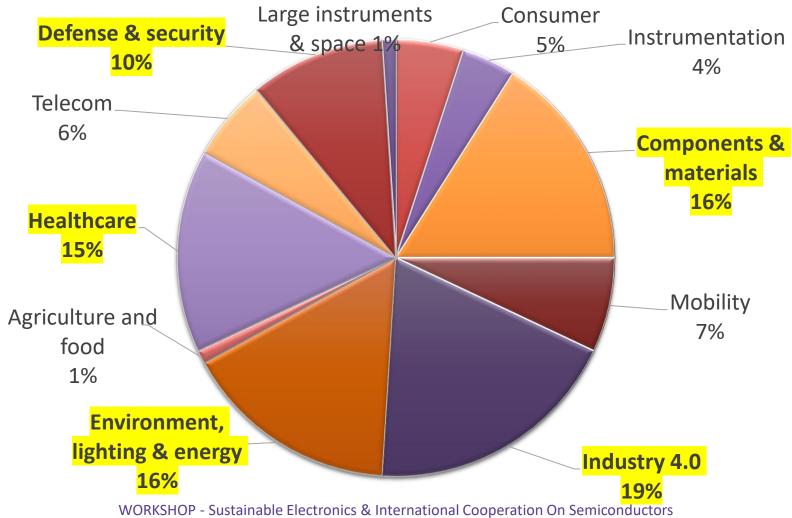

#### **Global Photonics Market**

#### Global Photonics market expected to reach €900 billion in 2025

### **Global Photonics Market**

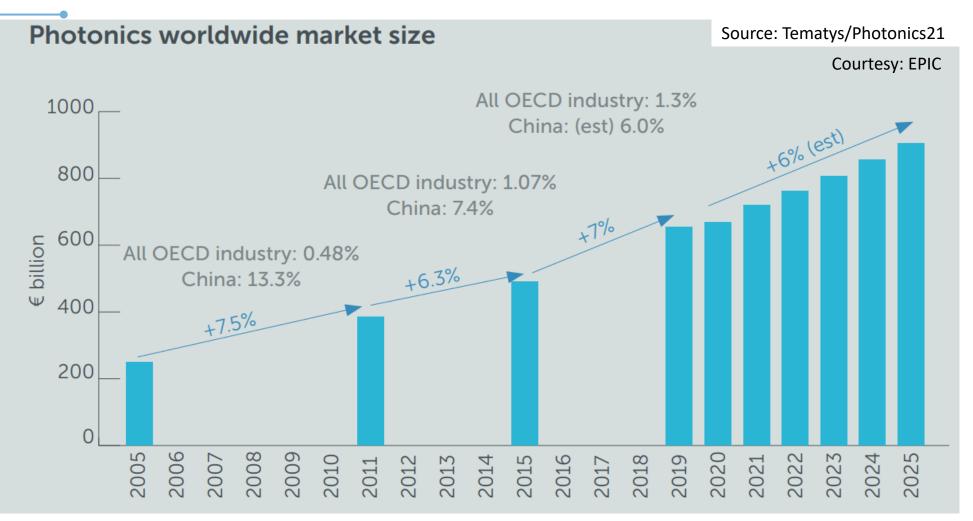

#### **Global photonics market share:**

- From 2015 to 2019, the share of the European photonics industry has been maintained at 17% of the global market thanks to the creativity of the European Research and the dynamism of companies active in "mid-size" markets.

- Asia photonics industry is mainly focus in displays, PV, and LED production

#### **Photonics in Europe**

Source: Tematys/Photonics21 Courtesy: EPIC

### Different forms of photonics

Free space optical technology

Optical fiber technology

Photonic chip technology

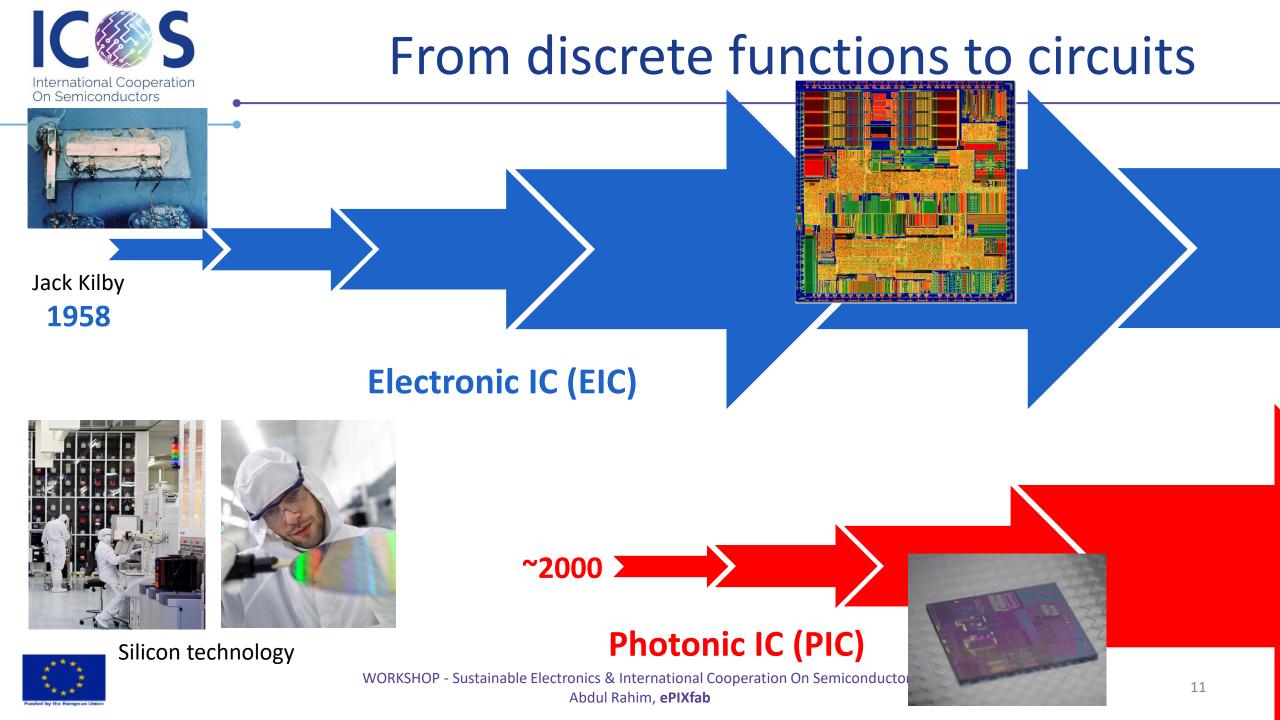

### Photonics Integrated Circuits (PICs)

International Cooperation On Semiconductors

Source: EECS Berkeley

#### PICs provide a route to commoditize photonics at larger volumes and lower costs

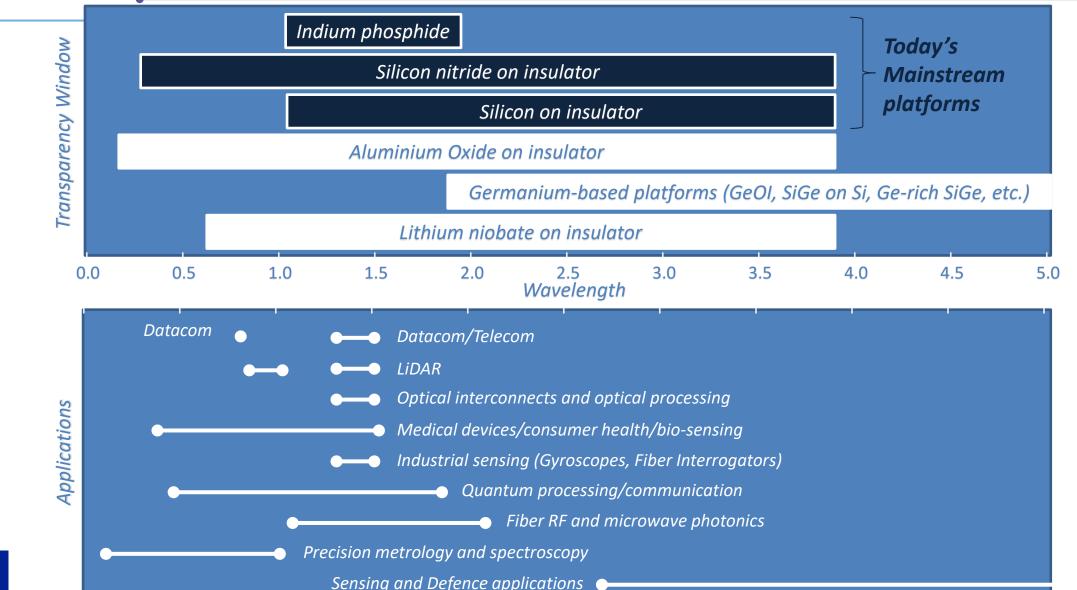

### PICs: platforms & application landscape

## PICs: platforms & application landscape

#### What else is not covered in this talk:

- X PICs based on Compound semiconductors, R&D platforms, emerging platforms

- X Imager chips

- X VCSEL Arrays

International Cooperation

### What is silicon photonics?

## The implementation of high density photonic integrated circuits by means of <u>CMOS process technology in a CMOS fab</u>

#### Enabling complex optical functionality on a compact chip at low cost

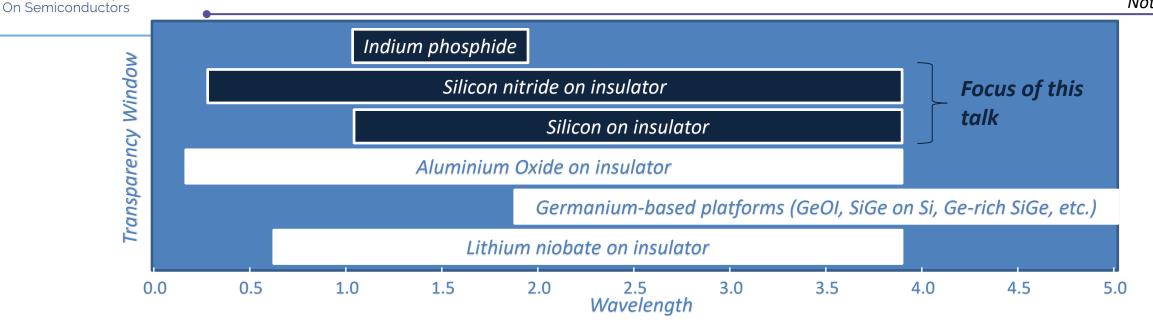

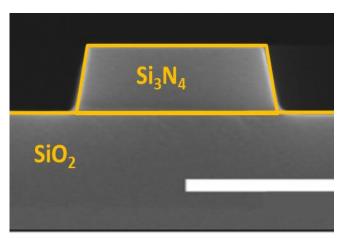

# Silicon photonics: Two CMOS –fab compatible families

#### Silicon-on-Insulator (SOI)

Silicon: n=3.5 Silicon oxide: n=1.45 Very high index contrast

Silicon nitride: n=2 Silicon oxide: n=1.45 Moderately high index contrast

Not exhaustive

### Main product today: transceivers for

#### datacom and telecom

WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors

Abdul Rahim, ePIXfab

Abdul Rahim, ePIXfab

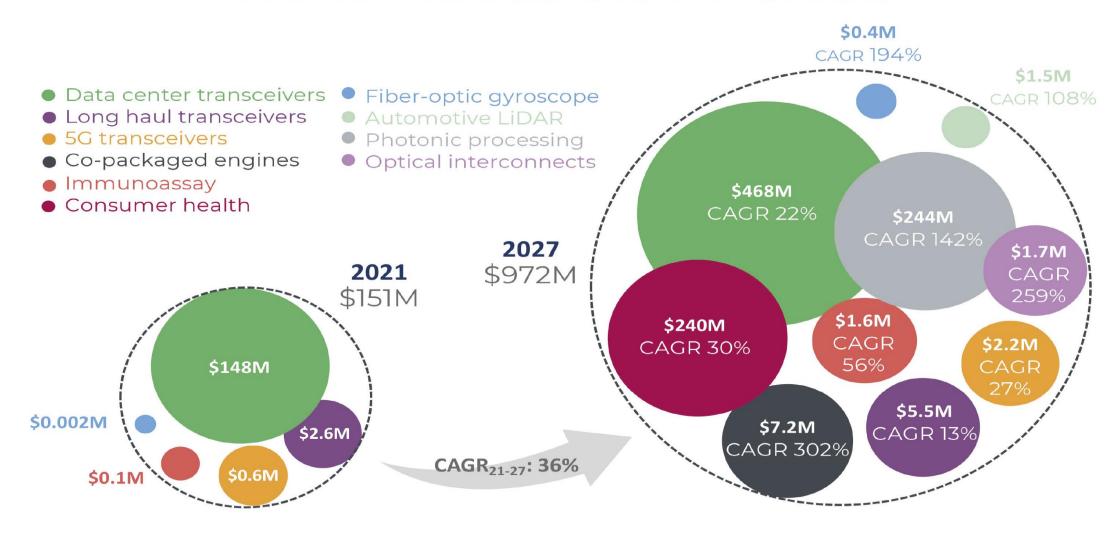

#### 2021-2027 SILICON PHOTONIC DIE FORECAST BY APPLICATION

Source: Silicon Photonics 2022 Report, Yole Intelligence, 2022

**WORKSHOP** – Sustainable Electronics & International Cooperation On Semiconductors

# Current state & future evolution of silicon photonics

- From technological lens

- From value chain lens + Europe's position

WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors Name

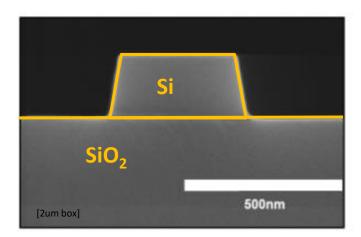

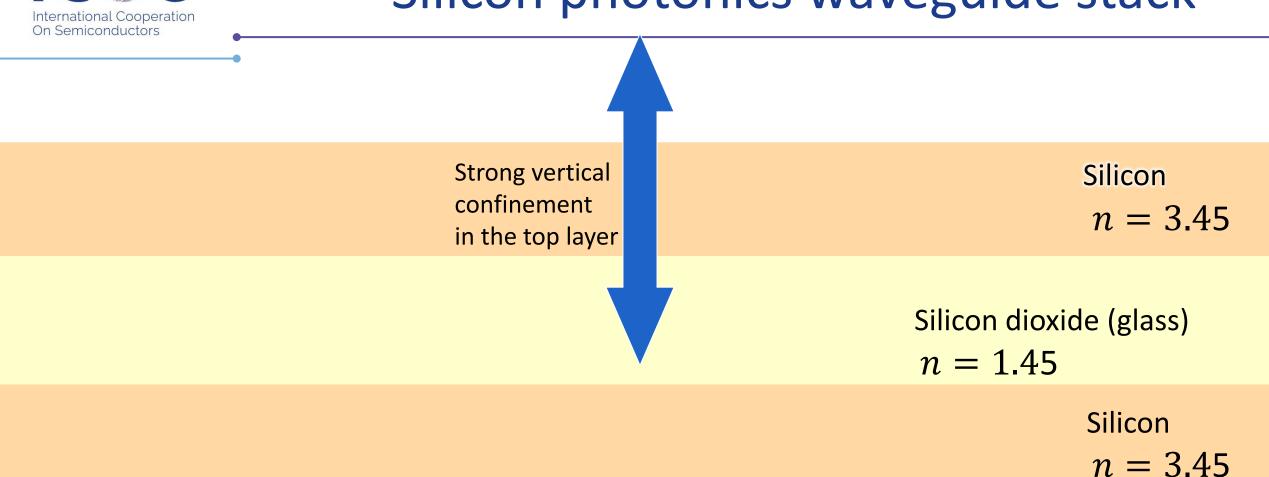

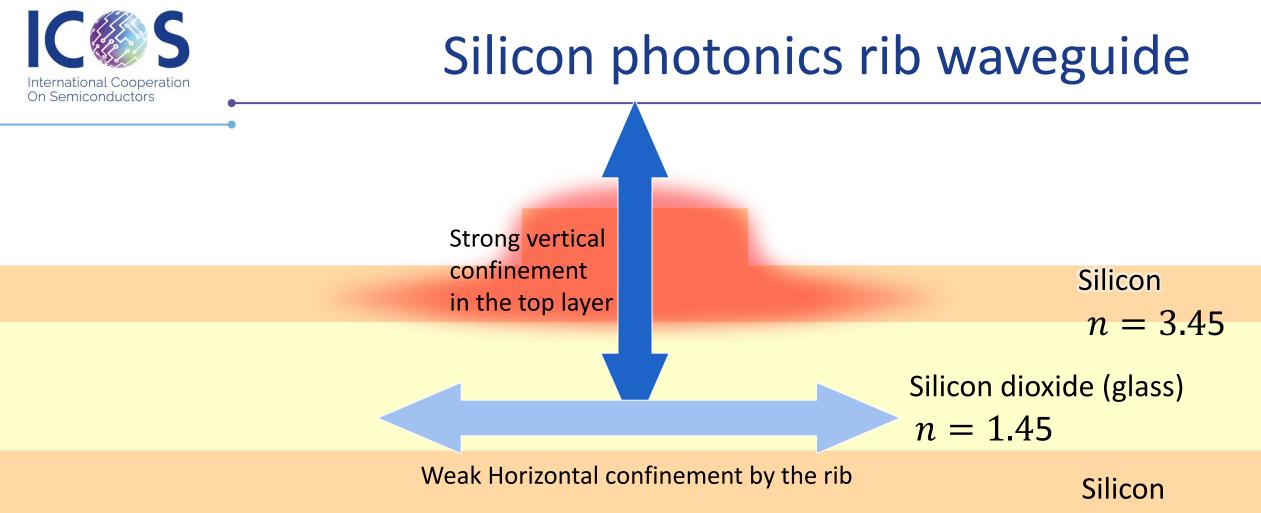

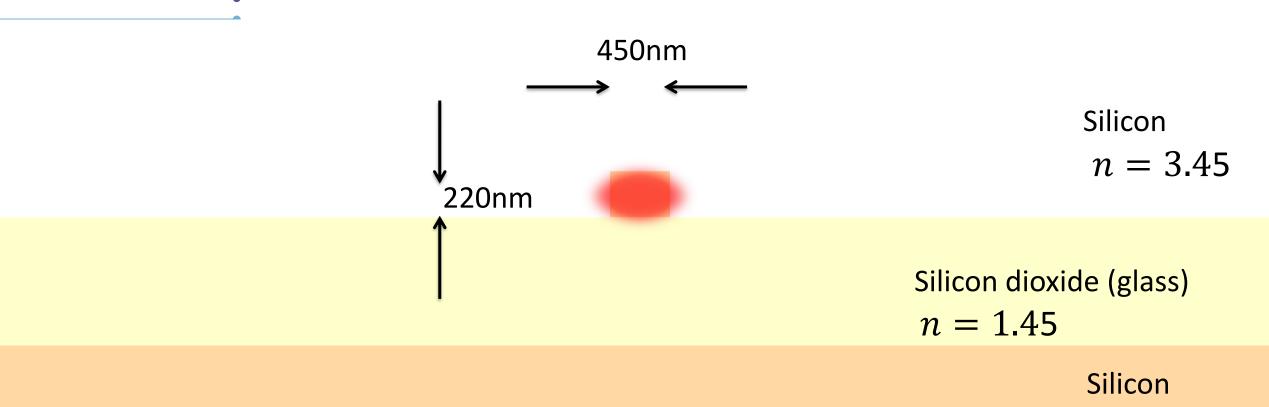

### Silicon photonics waveguide stack

*n* = 3.45

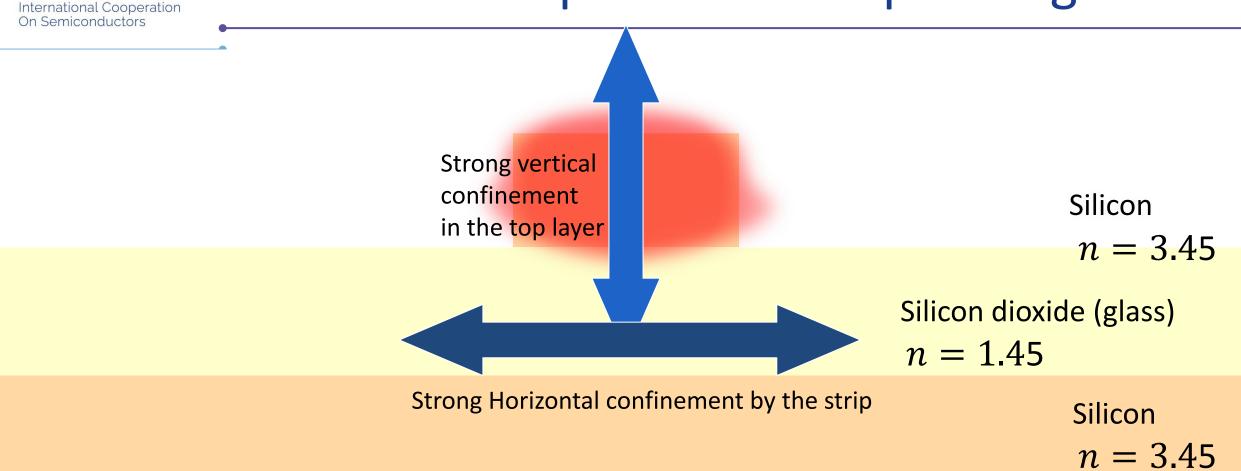

### Silicon photonics strip waveguide

#### Shrinking SOI waveguides

Siliconn = 3.45

Silicon dioxide (glass) n = 1.45

Siliconn = 3.45

#### Shrinking SOI waveguides

International Cooperation On Semiconductors

*n* = 3.45

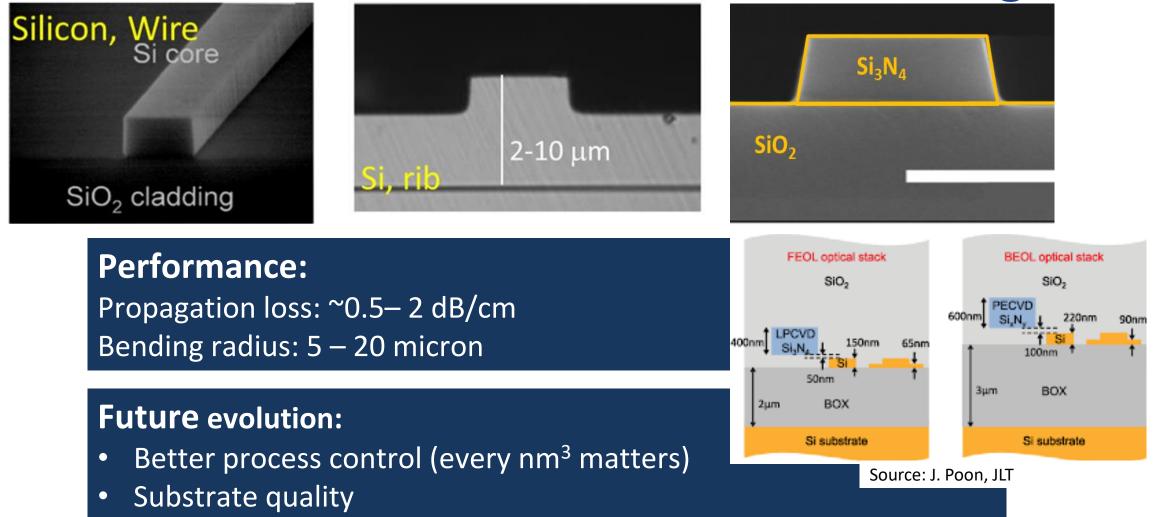

### Current state and future evolution:

#### Waveguides

• Multilayer platforms with medium index contrast guiding layers

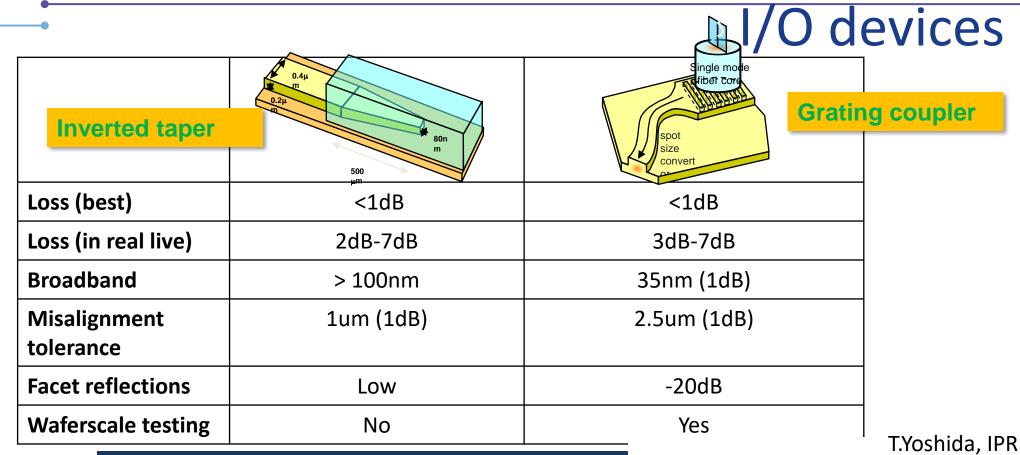

### Fiber coupling to WG

| 1µm      |

|----------|

|          |

|          |

| SOI wire |

#### Requirements

- Low loss

- Broadband

- High coupling tolerance

- No facet reflections

- Wafer-scale testability

- Easy to fabricate

#### Single-mode fiber

Vv.

### Current state and future evolution:

#### **Future evolution:**

- Better process control

- Substrate quality WiW and WtW

- New designs

International Cooperation On Semiconductors

### Current state and future evolution:

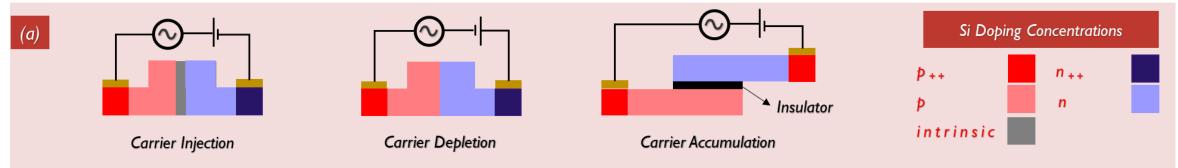

#### High-speed phase modulators

**Table 2** Typical and state-of-the-art performance matrix for the plasma dispersion high-speed phase modulators. The parentheses contain the best-reported result for a performance attribute. The matrix includes the results reported for O-band and C-band demonstrations.

| Principle                         | Modulation<br>efficiency<br>$V_{\pi} \cdot L$ (V $\cdot$ cm) | Loss (dB/cm)                  | Length <sup>a</sup> of<br>phase shifter<br>(mm) | Data rate <sup>b</sup><br>(Gb/s) | Energy/bit (fJ/bit)                                                   |

|-----------------------------------|--------------------------------------------------------------|-------------------------------|-------------------------------------------------|----------------------------------|-----------------------------------------------------------------------|

| Carrier injection <sup>c</sup>    | <0.5 (0.0588)                                                | ~70 (287)                     | ≥0.1 to <0.3                                    | <40 (70 <sup>7</sup> )           | ~1000 for MZMs and RMs (0.1 <sup>f,98</sup> )                         |

| Carrier accumulation <sup>d</sup> | <0.3 (0.16 <sup>69</sup> )                                   | 50 to 80 (~3569)              | ≤0.5                                            | ~40 (405)                        | >200 for MZMs, <200 (3 <sup>105</sup> ) for SLMs <sup>g</sup>         |

| Carrier depletion <sup>e</sup>    | ~2 (0.52 <sup>9</sup> )                                      | 10 to 30 (2.6 <sup>10</sup> ) | >1                                              | >40 (100 <sup>122,123</sup> )    | ~200 for MZMs (32.4 <sup>19</sup> ), <40 for RMs (0.9 <sup>18</sup> ) |

#### **Future evolution:**

Integration of novel materials (Ferroelectrics, 2D, Polymers, SiGe, III-Vs, etc.) for low Vpi, low loss, high bandwidth, and low energy pure phase shift

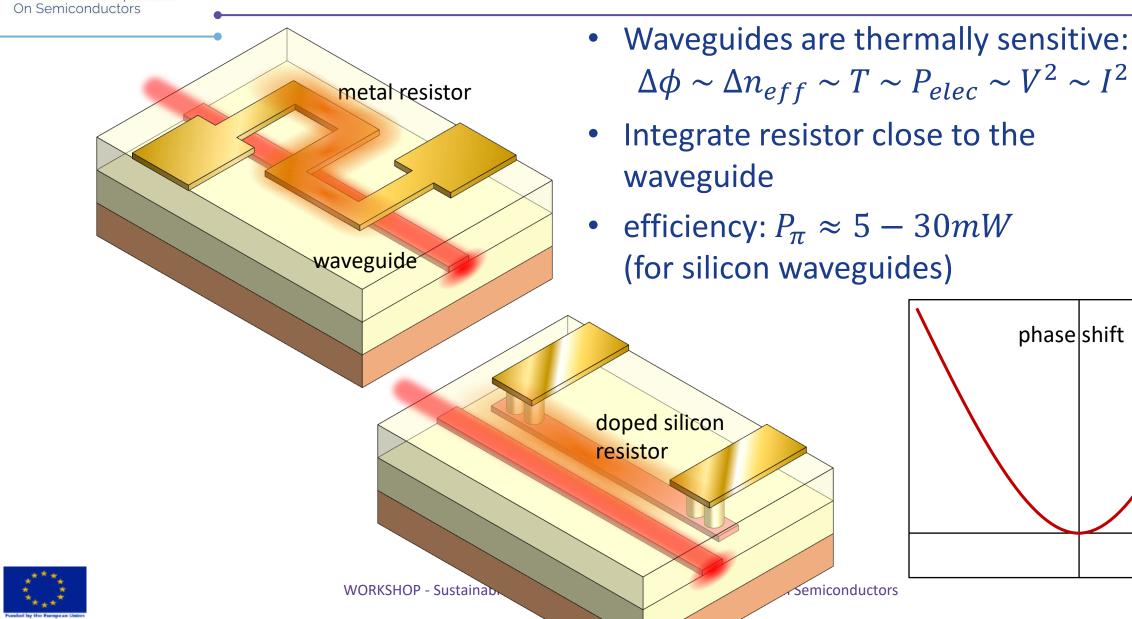

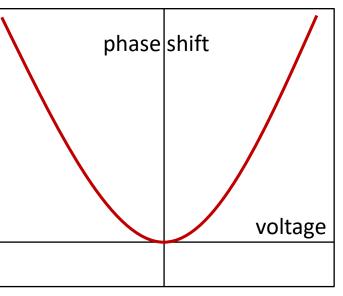

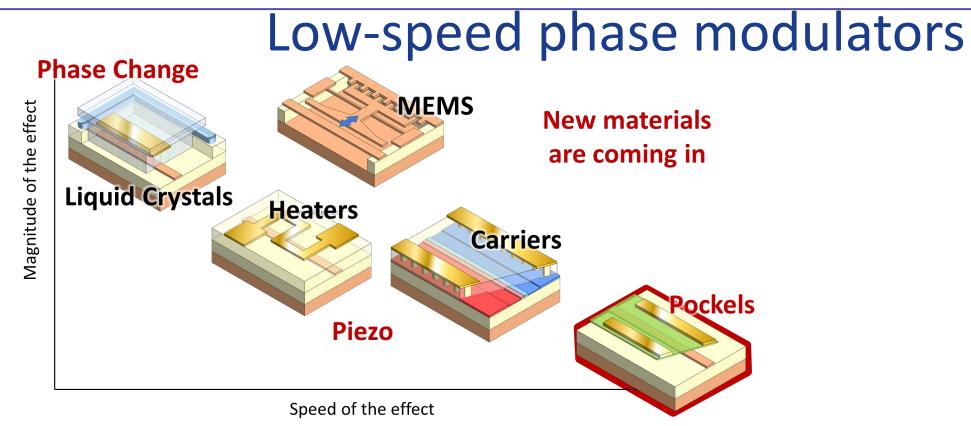

### Low-speed phase shifter by heaters

International Cooperation

28

#### **Future evolution:**

Integration of novel materials for more efficient (power, loss, crosstalk) low-speed phase shifters

International Cooperation

| Photodetectors         | [unit]   |                 |

|------------------------|----------|-----------------|

| Absorption             | α (cm⁻¹) | 10 <sup>3</sup> |

| Dark Current           | l (nA)   | 0.2             |

| Responsivity (p-i-n)   | R (A/W)  | 1               |

| Bandwidth (p-i-n)      | B (GHz)  | >100            |

| Gain x Bandwidth (APD) | GB (GHz) | 300             |

| Guided Power*          | mW       | 30              |

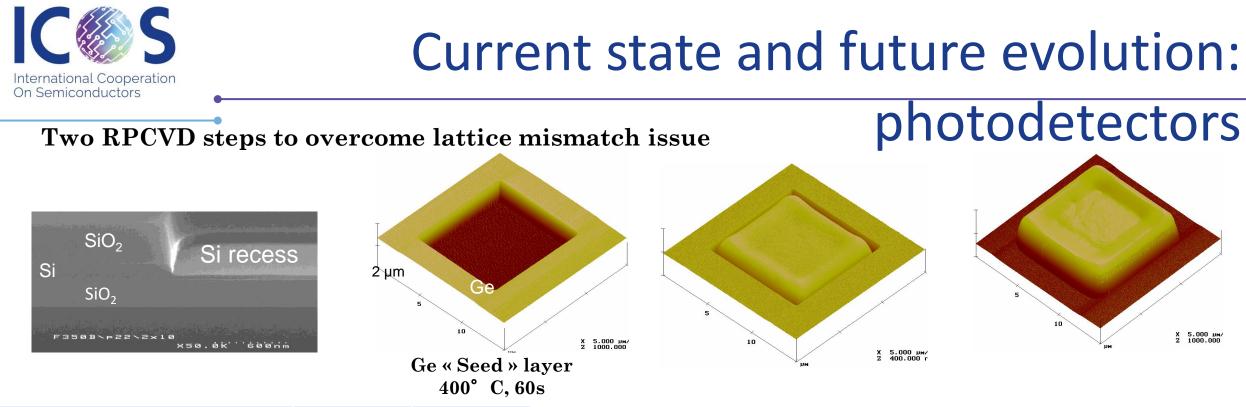

#### **Future evolution:**

- Better process control for narrower intrinsic regions

- Lower defect density for lower dark currents

S. Lischke, Nat. Photonics

### Current state and future evolution:

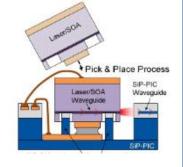

#### Light sources

#### LaMP

- ✓ Use mature III-V technology

- ✓ Wafer level test on source

- ✓ Known good die

- No waveguide-in / waveguide-out devices

- Sequential population of SiPhwafer

#### **Flip-chip Integration**

- ✓ Use mature III-V technology

- ✓ Wafer-level test on source

- ✓ Known good die

- ✓ Fairly efficient optical coupling

- Sequential population of SiPhwafer

- Requires local back-end removal

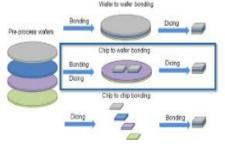

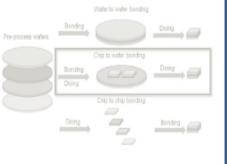

#### **Die-to-wafer bonding**

- ✓ Efficient optical coupling

- ✓ Parallel processing of devices

- ✓ Wafer-level test on target wafer

- III-V processing on target wafer

- No known good III-V die

31

WORKSHOP Sustainable Electronics & Ir ternational Cooperation On Semiconductors

Abdul Rahim, ePIXfab

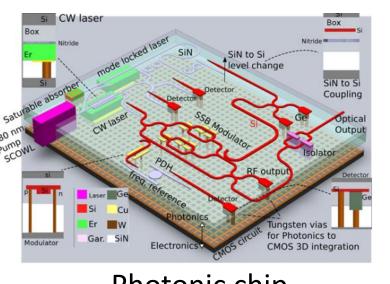

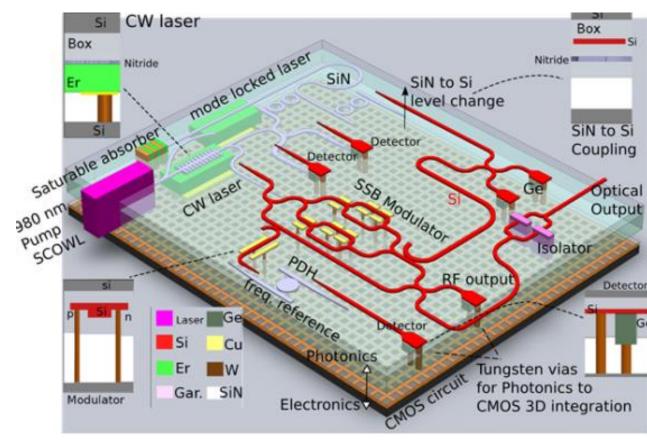

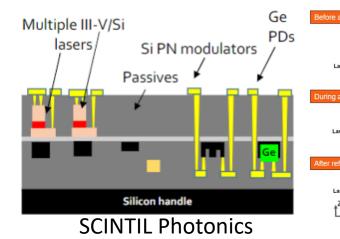

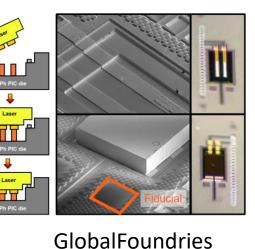

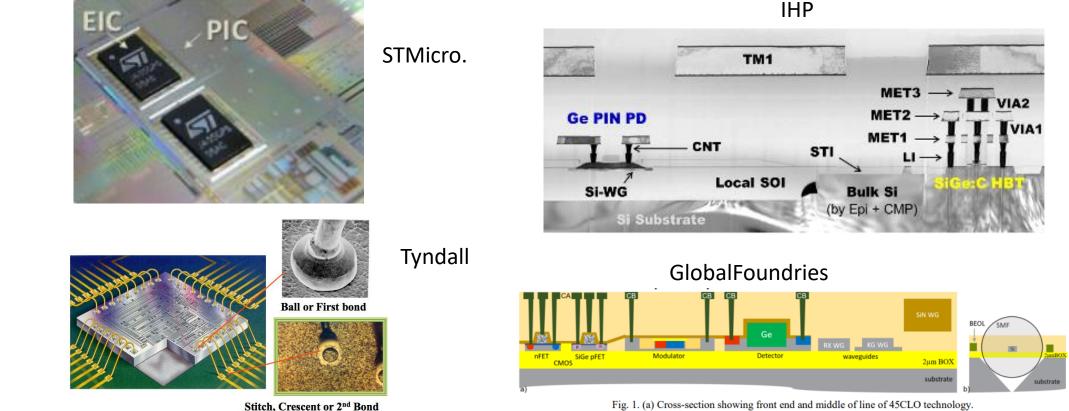

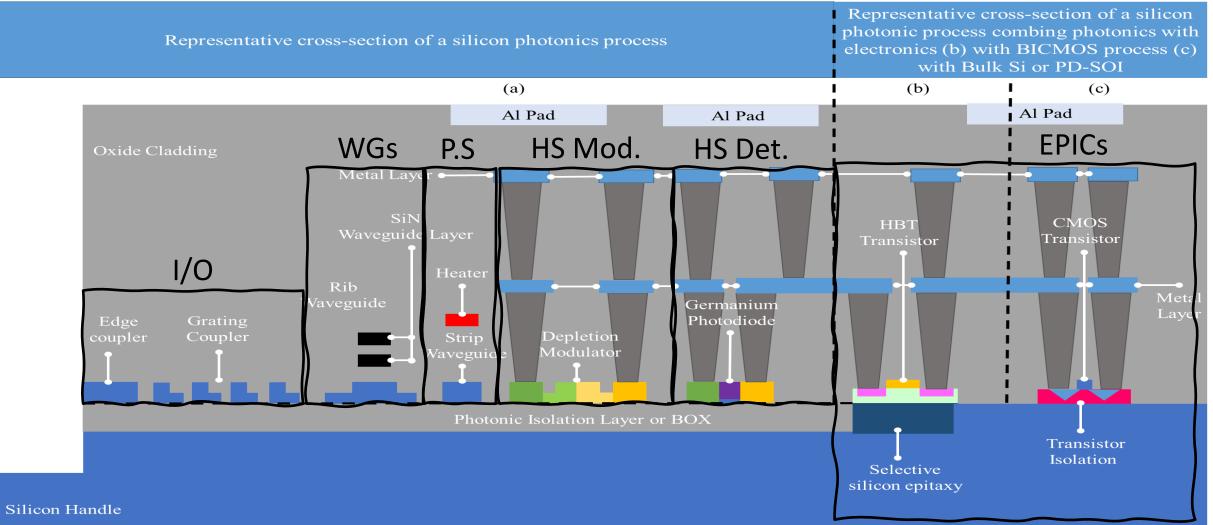

## Current state and future evolution :

#### electronic-photonic integration

Fig. 1. (a) Cross-section showing front end and middle of line of 45CLO technology. (b) Cross-section diagram of the IOSMF with v-groove and the attached fiber.

**Future Evolution:** Higher intimacy between electronics and photonics becoming more important

### A generic cross-section of a silicon

#### photonics platform

International Cooperation On Semiconductors

# Current state & future evolution of silicon photonics

- From technological lens

- From value chain lens + Europe's position

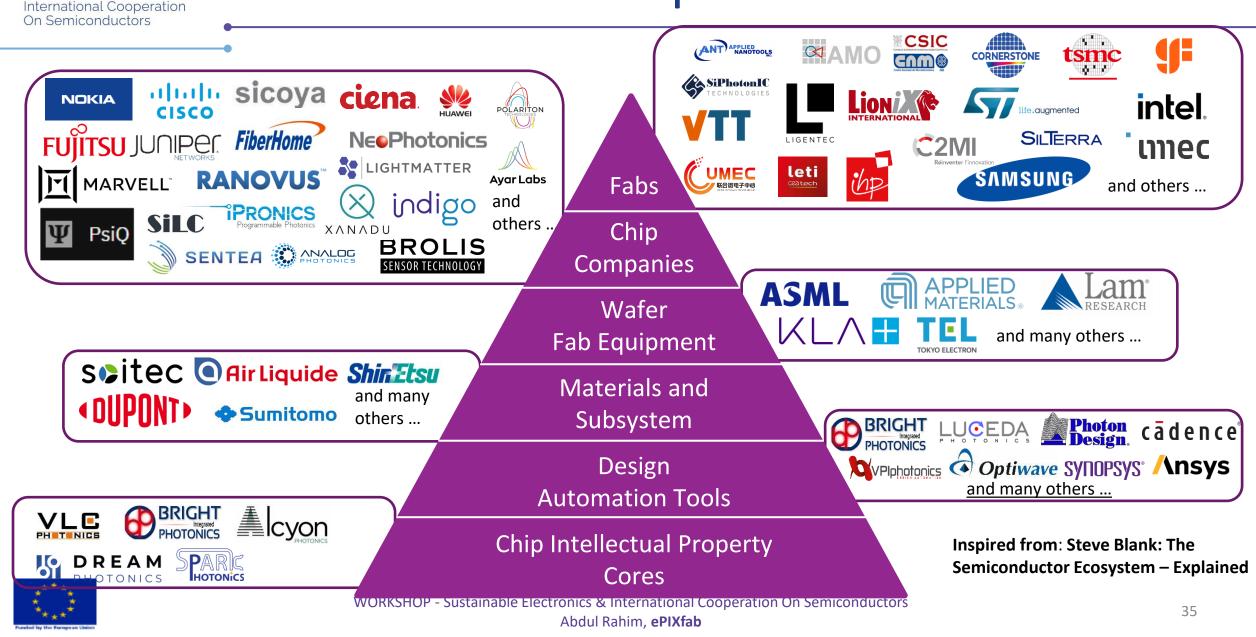

### Silicon photonics value chain

#### White Paper on Integrated Photonics

and

#### Photonics21

Michael Scholles, Michael J. Wale, Timo Aalto, Mohand Achouche, Luc Augustin, David Bitauld, Sonia Garcia Blanco, Patrick Cogez, Marcus Dahlem, Paul van Dijk, Gerhard Domann, Amir Ghadimi, Martijn Heck, Thomas Hessler, Andreas Klug, Renaud de Langlade, Martin Martens, Christian Meyne, Clifford Murray, Sybille Niemeier, Ruud Oldenbeuving, Mehmet Cengiz Onbaşlı, Joseph Pankert, Ryszard Piramidowicz, Abdul Rahim, Graham Reed, Jelmer Renema, Ewit Roos, Martin Schell, Elisabeth Steinmetz, Martin Strassburg, Bertrand Szelag, Tolga Tekin, Dao Thang Duy, Dries van Thourhout, Marija Trajkovic, Gintaras Valusis, Lennart de Vreede, Markus Wilkens, Martina Wisniewski, Benjamin Wohlfeil, Lars Zimmermann

April 2023

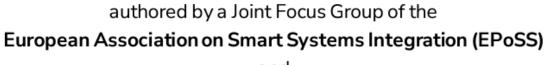

### Ecosystem status: materials and substrates

International Cooperation On Semiconductors

SOI TECHNOLOGY FOR DATACENTER AND CONSUMER SENSING APPLICATIONS - C. SCIANCALEPORE

spitec

ssitec

### **Europe's position**

- ✓ One of the largest SOI wafer manufacturer is based in Europe (SOITEC)

- ✓ Close collaboration of EU fabs and substrate manufactures to meet future substrate demands (wafer sizes, uniformity)

- Diversity of material systems makes it difficult for substrate manufactures to make a bet (a lot of parallel R&D)

- Access to novel material likes TFLN and EUs push to include

novel materials with SiPh.

### design automation

- Large EDA vendors (that are mostly US-centric organizations) offer integrated photonics design frameworks

- The fab PDKs are getting rich but still lack compact models and not at-par with electronic PDKs

- Lack of unified process flow for electronic-photonic co-design

- Lack of standardization and no incentive in doing that

- Limited number of design houses and IP vendors

# Ecosystem status: electronic photonic

### design automation

### **Europe's position**

- ✓ A number of smaller but collaborative companies offering bestin-class for various aspects of photonic design flow

- Close relationship of the stakeholders with EU and non-EU foundries to support various PIC platforms

- -Challenges in attracting and retaining talented HR, limited scale-up funding, limited business in EU

- -Asia and US driving the narrative and winning the business

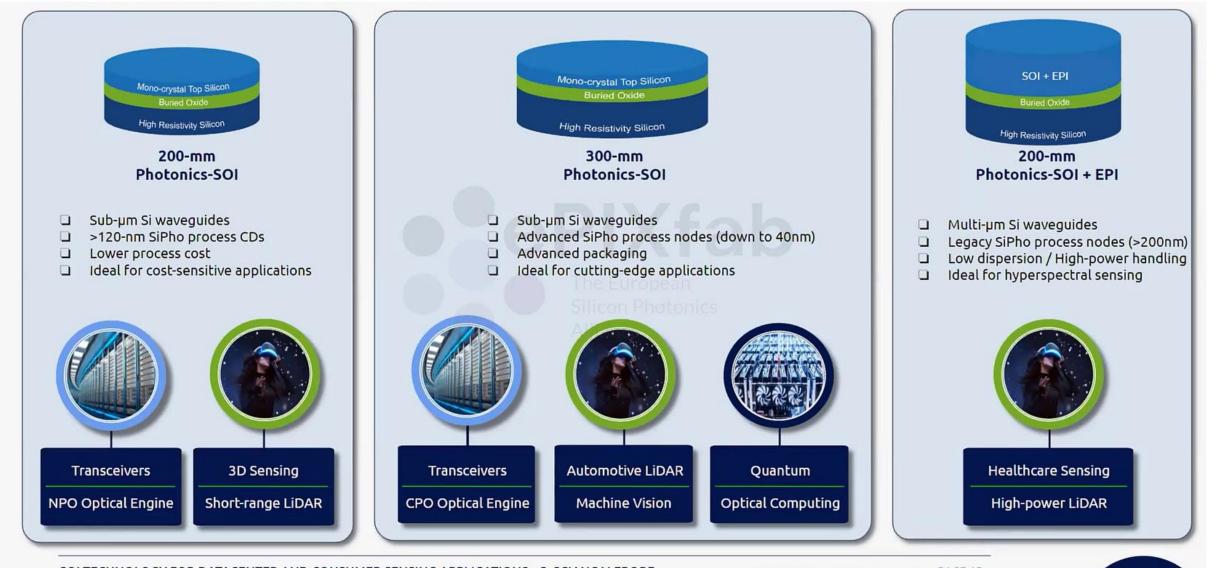

### Ecosystem status: manufacturing

International Cooperation

### **Europe's position**

- Renowned R&D institutes with a an established track record in integrated photonics offering open-access pilot-scale manufacturing of silicon photonics

- ✓ Rich portfolio of platforms with their complementary strengths

- ✓ Full value chain in EU: electronics, photonics, packaging

- —No pure-play high-volume and high-end silicon photonics fab today

- 70% of the costs associated with silicon photonic device production arise during this packaging process

- Rapid evolution of technologies and solutions

- Toolmakers have emerged

- Less investment and lack of standardization

**Photonics Spectra**

Ficontec PIC Assembly Tool

Abdul Rahim, ePI)

### **Europe's position**

- ✓ Know-how, expertise both a pilot-scale and beyond

- $\checkmark$  EU equipment providers for assembly and packaging

- Lack of co-design tools and lack of experts

- -Dominance of outsourcing to Asian suppliers

PIXAPP Photonic Packaging *ticontec* 🗾 Fraunhofer IZM vang PHOTONICS bright connections 44

# **Future trends in silicon photonics**

WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors Abdul Rahim, **ePIXfab**

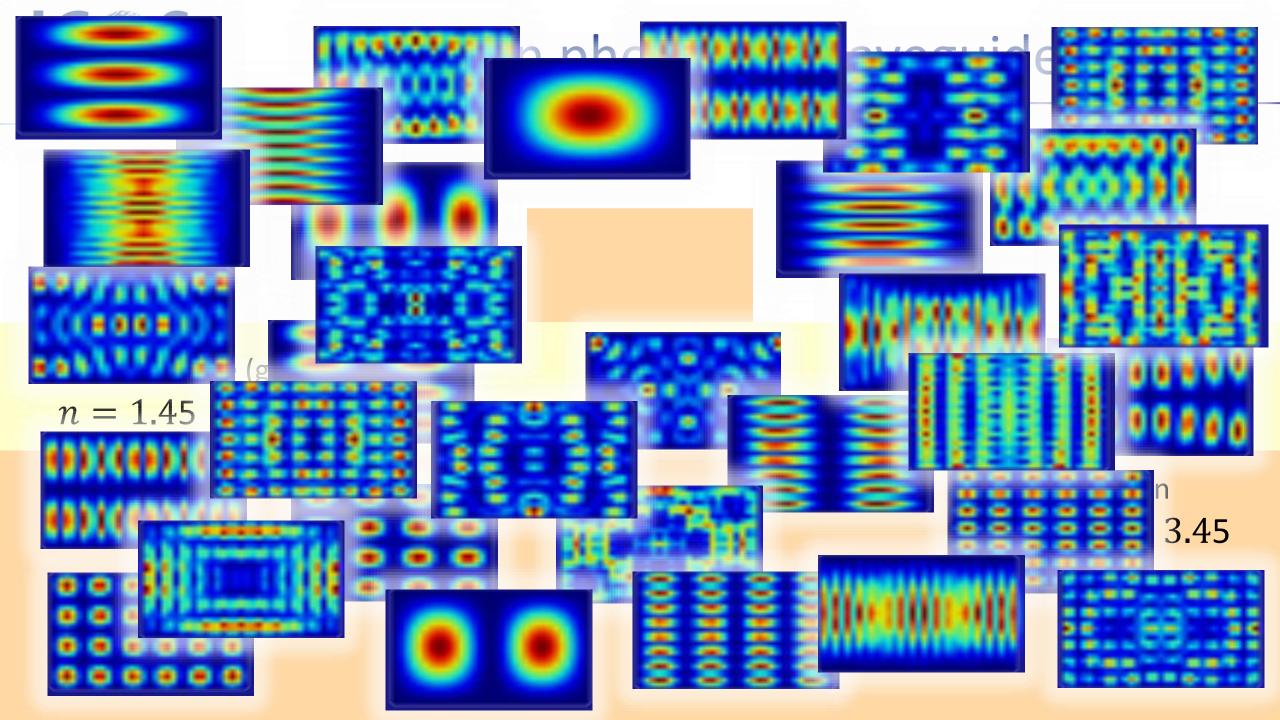

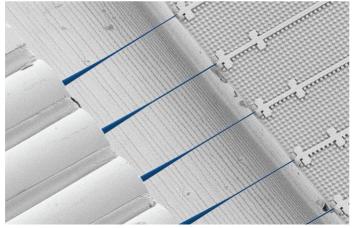

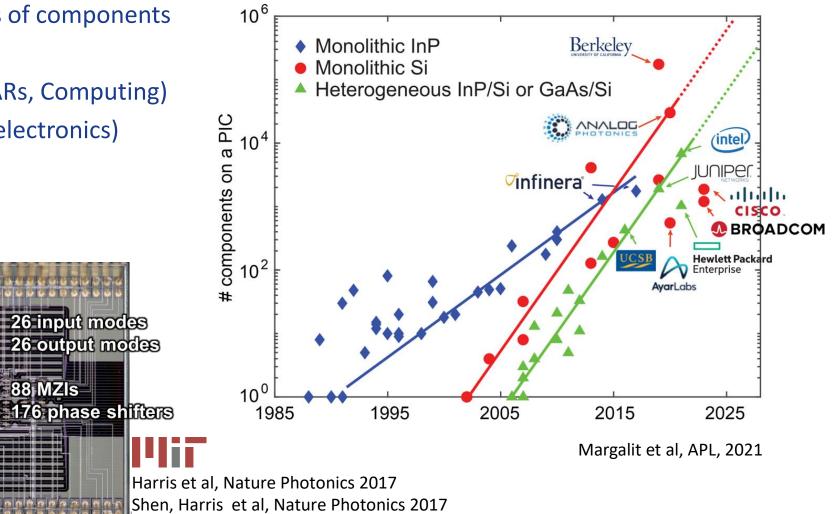

# Future Trends - Large-scale photonic

integration

- Growing order of integration; 10Ks of components

- photonics + electronic drivers

- different applications (AI, ML, LiDARs, Computing)

- Small chip volumes (compared to electronics)

Harris et al, Optica 2018

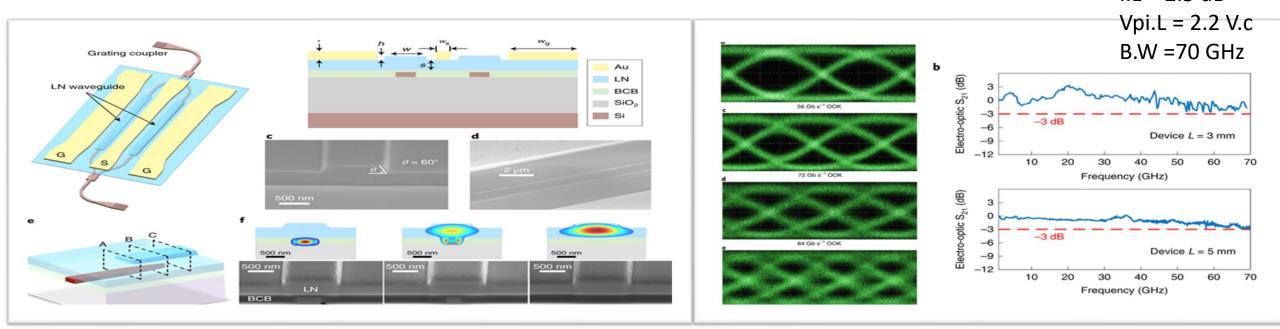

# Future Trends - Heterogenous silicon

photonics

$I.L = 2.5 \, dB$

- Wafer-scale integration of novel materials to boost the performance of silicon photonics building blocks

- Example: high-speed phase modulator

https://www.nature.com/articles/s41566-019-0378-6

WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors Abdul Rahim, **ePIXfab**

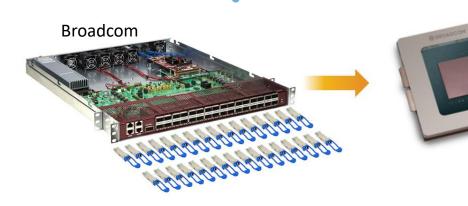

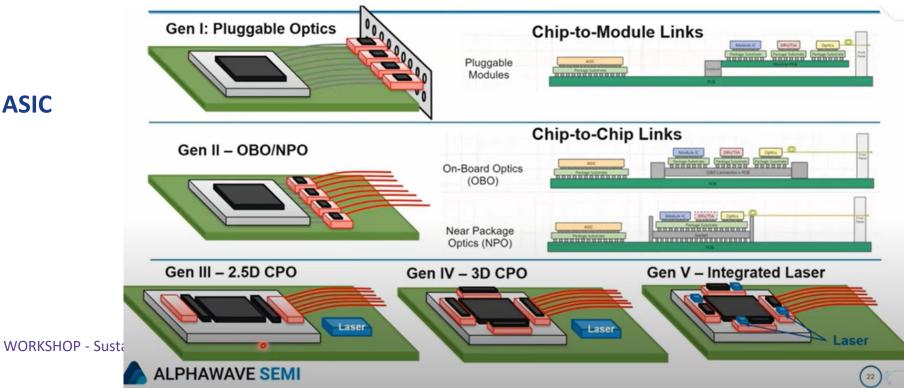

# Future Trends - Enhanced intimacy b/w

#### electronics and photonics Co-Packaged Optics

- Integration of optical engines

- on a common package substrate

- Objective: alleviate the "interconnect density bottleneck"

- Low power

- Low cost

- Low latency

- Higher IO bandwidth

**Challenges:**

- Power heat management in ASIC

- Complex assembly

- Difficult field service

- Restricts competition with concentrated R&D to a few companies

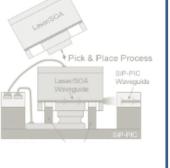

# Future Trends - Light source integration

#### LaMP

- ✓ Use mature III-V technolo

- ✓ Wafer level test on source

- ✓ Known good die

- Fairly efficient optical coul

- No waveguide-in / waveg

- Sequential population of

- Can be integrated on back

#### Flip-chip Integration

#### **III-V integration using hetero-epitaxy**

- Front end monolithic integration

- Efficient evanescent coupling

- Develop completely new process flow

- Demonstrate yield and reliability

#### oupling of SiPhwafer es difficult removal

#### **Die-to-wafer bonding**

- ✓ Efficient optical coupling

- ✓ Waveguide in-out devices

- ✓ Parallel processing of devices

- ✓ Wafer-level test on target wafer

- III-V processing on target wafer

- No known good III-V die

- Front-end / back-end NRE

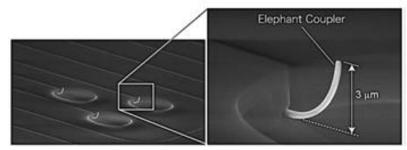

#### **Micro-transfer printing**

- ✓ III-V process & test prior to integration

- ✓ Back-end integration

- ✓ High throughput integration

- Efficient evanescent coupling

- Supply chain being established state source out

- To demonstrate yield and reliability

HOP Sustainable Electronics & Irlterrlational Cooperation On Semicor

- There is a diversity of platforms available in silicon photonics

- Heterogeneous integration provide routes to boost the performance of silicon PIC building blocks

- Datacom/telecom is the major driver today. Other applications are on the horizon

- European silicon photonics eco-system is in a decent shape but has limited design houses, and also lacks an open-access high-volume commercial foundry service.

### THANK YOU

This project has received funding from the European Union's Horizon Europe research and innovation programme under GA N° 101092562

**WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors**

www.icos-semiconductors.eu