**WORKSHOP** – Sustainable Electronics & International Cooperation On Semiconductors

### Augmented FDSOI platforms for improved sustainability

**Roberto GONELLA**

**R&D Executive Director**

**STMicroelectronics**

WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors Roberto GONELLA

life.auamente

### We are creators and makers of technology

### Where you find us

Making **driving** safer, greener, and more connected

Enabling the evolution of **industry** towards smarter, safer, and more efficient factories & workplaces

Making **homes & cities** smarter, for better living, higher security, and to get more from available resources

Making everyday **things** smarter, connected, and more aware of their surroundings

# ICOS Differentiated technologies are our foundation

MEMS **Smart Power: BCD** for sensors & micro-actuators (Bipolar - CMOS - Power DMOS) **FD-SOI CMOS Discrete, Power MOSFET, IGBT FinFET** through Foundry Silicon Carbide, Gallium Nitride Analog & RF CMOS **Vertical Intelligent Power Optical sensing solutions eNVM CMOS** -**Packaging technologies** Leadframe – Laminate – Sensor module – wafer level

# ICOS Differentiated technologies are our foundation

**MEMS** FD-S<del>C</del>I **Discrete, Power MOSFET, IGBT** Silicon Carbide, Gallium Nitride Analog & RF CMOS **Optical sensing solutions**

# **IC** S Our strategy stems from key long-term enablers

On Semiconductors

Helping car manufacturers make driving safer, greener, and more connected for everyone

**Power & Energy**

Enabling industries to increase energy efficiency everywhere and the use of renewable energy

**Internet of Things & Connectivity**

Supporting the proliferation of smart, connected IoT devices with products, solutions & ecosystems

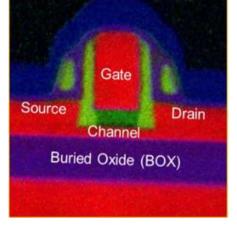

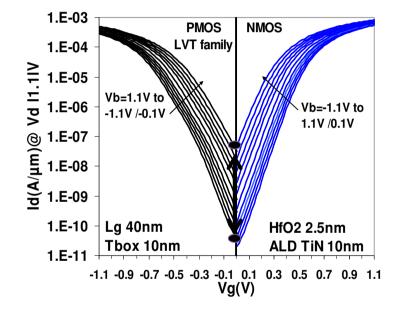

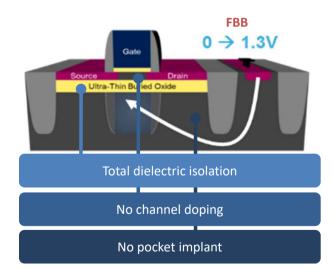

### What's FDSOI?

FDSOI is a cost-effective planar technology that relies on

- sub-threshold slope reduction

- DIBL lowering

-

- FBB techniques

To boost performances especially at low and ultra low voltage

The presence of the buried oxide allows the application of backbiasing voltages, resulting in breakthrough dynamic control of the transistor

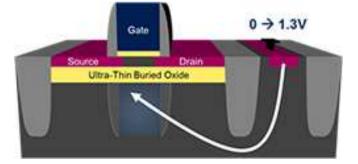

### **FD-S**- the body bias advantage

Forward Body Biasing is a unique and effective knob available in FD-SOI for getting maximum leverage on the device operating range

Forward Body Biasing: An extremely powerful and flexible concept in FD-SOI

Performance boost

Reduce power consumption at a given performance requirement

Process compensation reducing the margins to be taken at design

Seamless inclusion in the EDA flow

#### A very reasonable effort for extremely worthwhile benefits

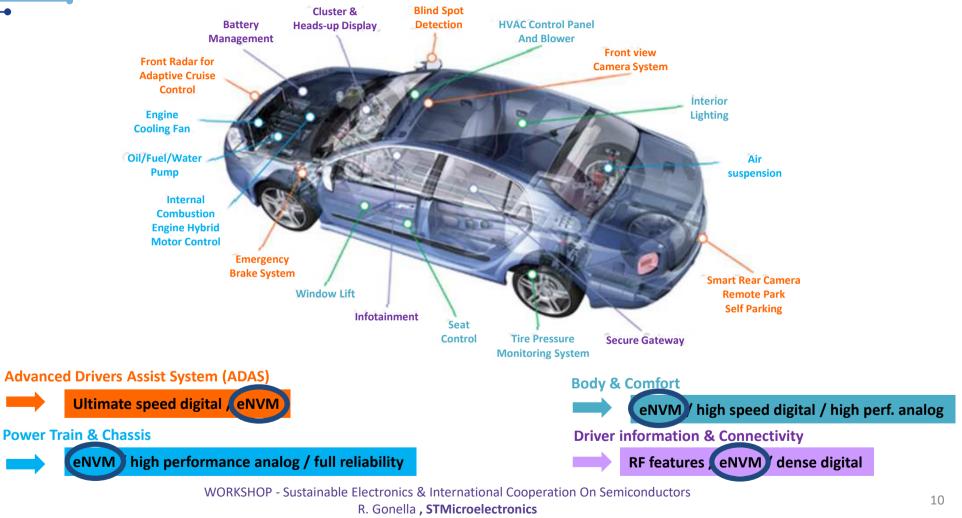

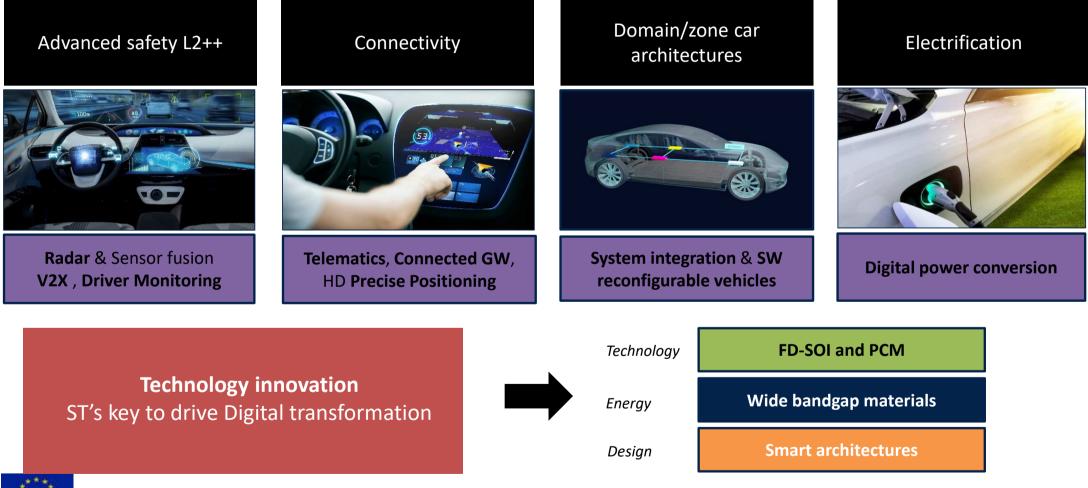

### Smart Mobility – FDSOI Inside

Helping car manufacturers make driving safer, greener, and more connected for everyone

### Automotive MCUs & eNVM Usages

# ICES MCUs Dissemination in Automotive

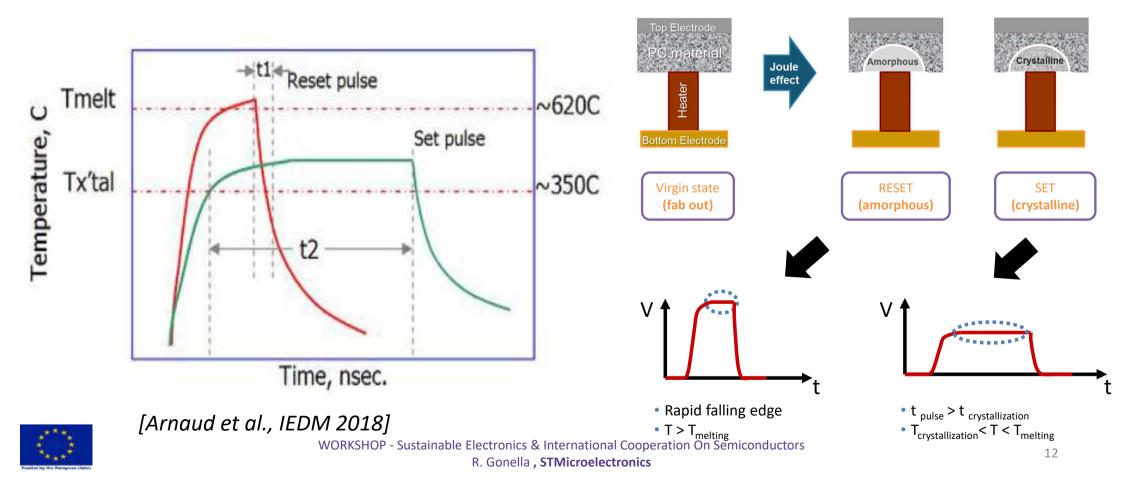

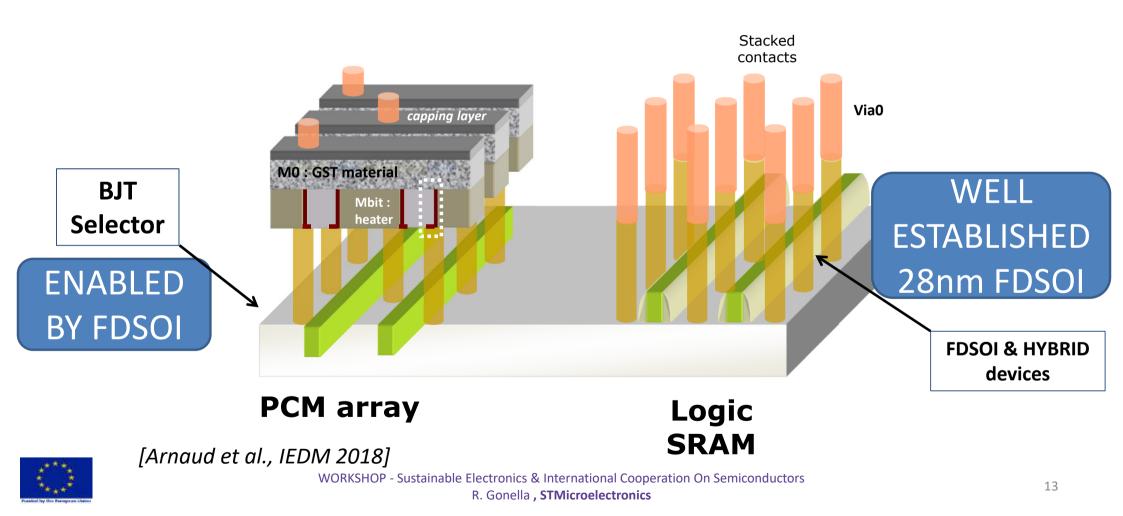

### ePCM-FDSOI Co-Integration

ctronics & International Cooperation On Semiconductors R. Gonella , **STMicroelectronics**

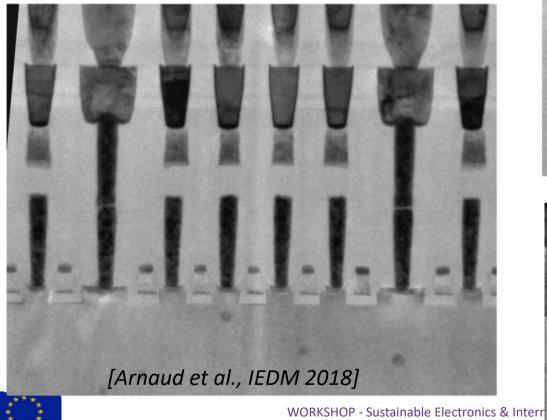

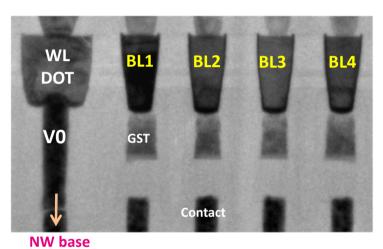

### PCM Morphology (Storage element & heater)

#### General view of the structure

Section along WL

Section along BL

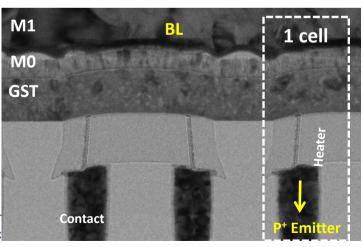

### 16MB ePCM Reliability for Grade-0 Automotive MCUs

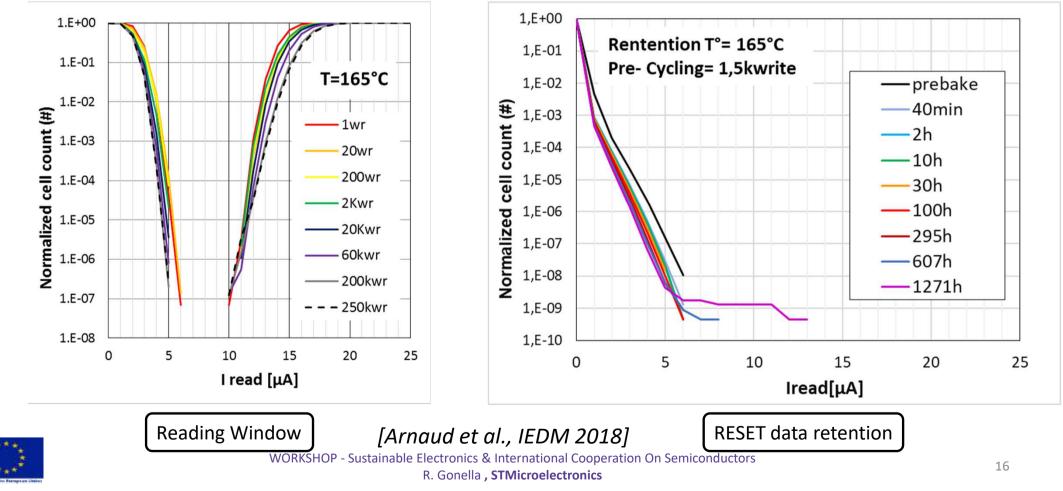

### UNIQUE AND KEY ADVANTAGE OF PCM

### Power & Energy – FDSOI Inside

Enabling industries to increase energy efficiency everywhere and the use of renewable energy

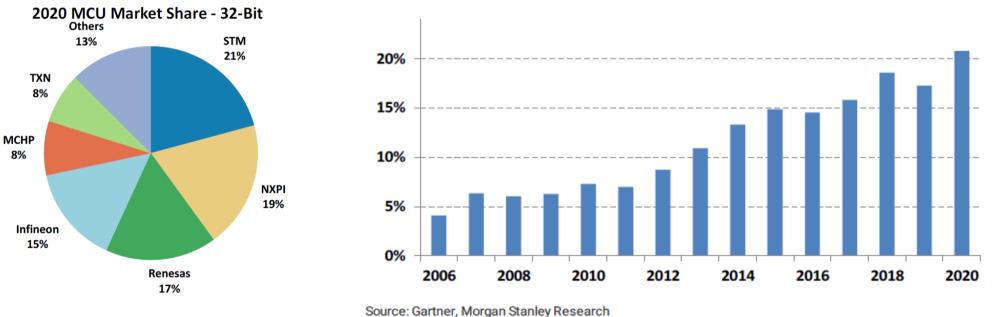

### STMicroelectronics 32-bit MCUs growth

STM 32-Bit Market Share

- Continuous growth of market share in MCUs, especially 32-bit

- Main business for ST is about general purpose and ULP MCUs

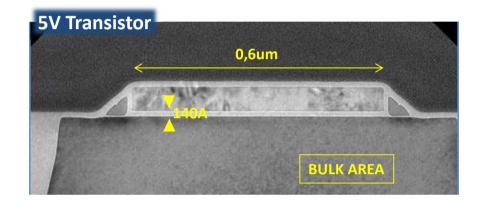

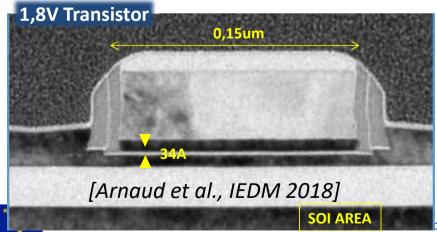

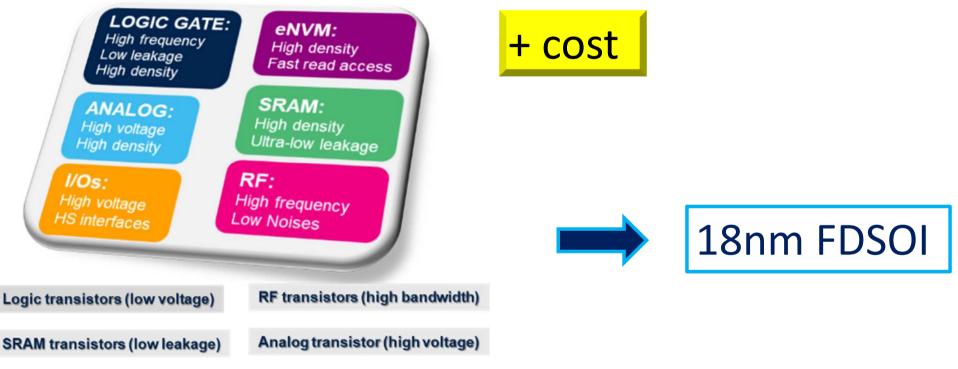

### ULP MCUs wide range needs : birth of 18nm FDSOI

Key ULP MCUs features

#### Need performance at low voltage, low leakage, density and low process cost

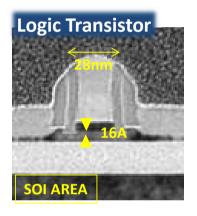

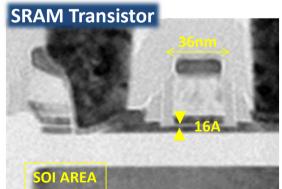

### 18nm FDSOI: global features

- Triple gate oxide: SG (0.9V), EG (1.8V), eZG (3.3V)

- 4 VTs, full flipwell

- Mx pitch: 64nm

- CPP: 100/108nm

- SRAM: 0.102µm<sup>2</sup>

- CSiGe continuous active (CNRX) standard cells scheme

- RF dedicated offer

- ePCM for eNVM

[Doohong Min et al., IEDM 2021]

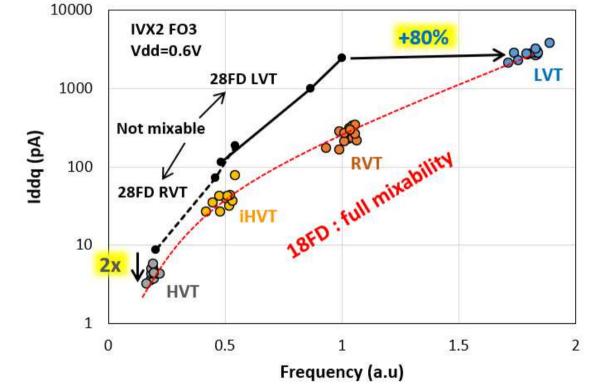

### Wide range of speed/leakage

- 4 VTs mixability

- +80% perf. at 0.6V wrt 28FDSOI, 2X leakage reduction

WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors R. Gonella , **STMicroelectronics**  [Weber et al., IEDM 2022]

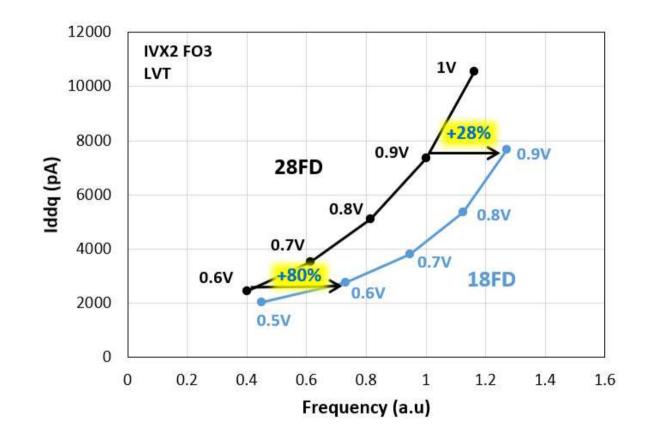

### High performance at low voltage

### From +28% speed at 0.9V up to +80% at 0.6V wrt 28FDSOI

<sup>[</sup>Weber et al., IEDM 2022]

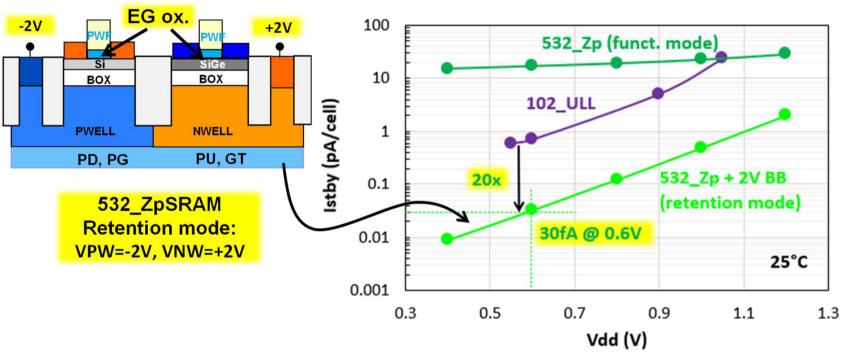

### **ZpSRAM retention leakage**

[Weber et al., IEDM 2022]

### Extremely low retention leakage of 30fA/cell at 0.6V, 25°C is demonstrated, 20x lower than for the 102ULL bitcell !

### IoT & Connectivity – FDSOI Inside

Supporting the proliferation of smart, connected IoT devices with products, solutions & ecosystems

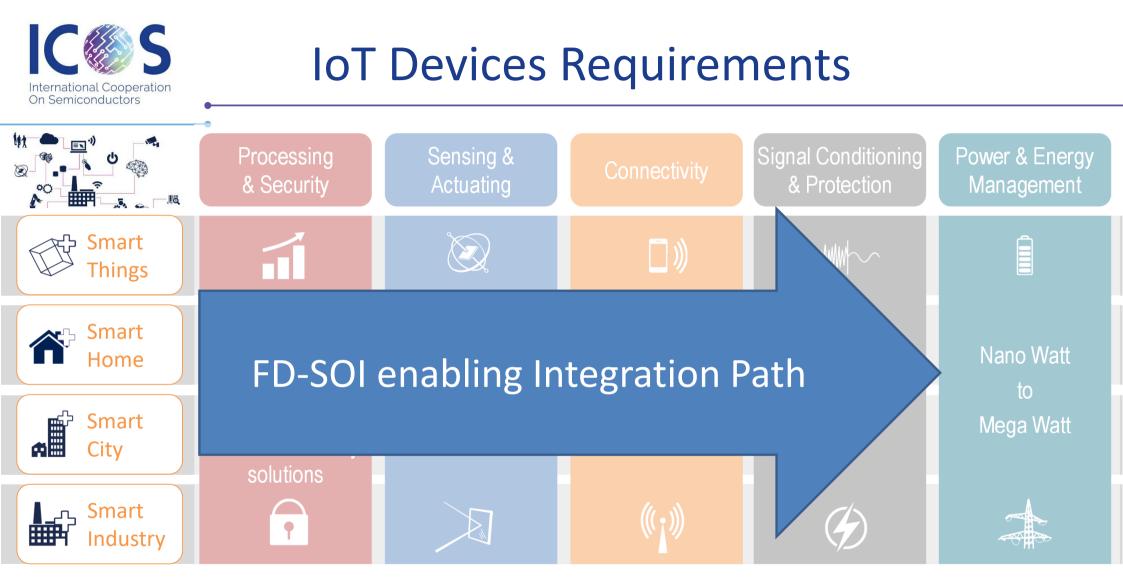

#### **IoT Devices Requirements** International Cooperation On Semiconductors Signal Conditioning Power & Energy Sensing & Processing Connectivity & Security Actuating & Protection Management Smart ₩₩/ Things Ultra-Low Power Smart Full range of to 10 cm Nano Amps Nano Watt Home **High Performance** sensors to to to and Smart Kilo Amps Mega Watt 10 km actuators **Scalable Security** City solutions \_\_\_\_ Smart (((†))) • ⊞₽ Industry

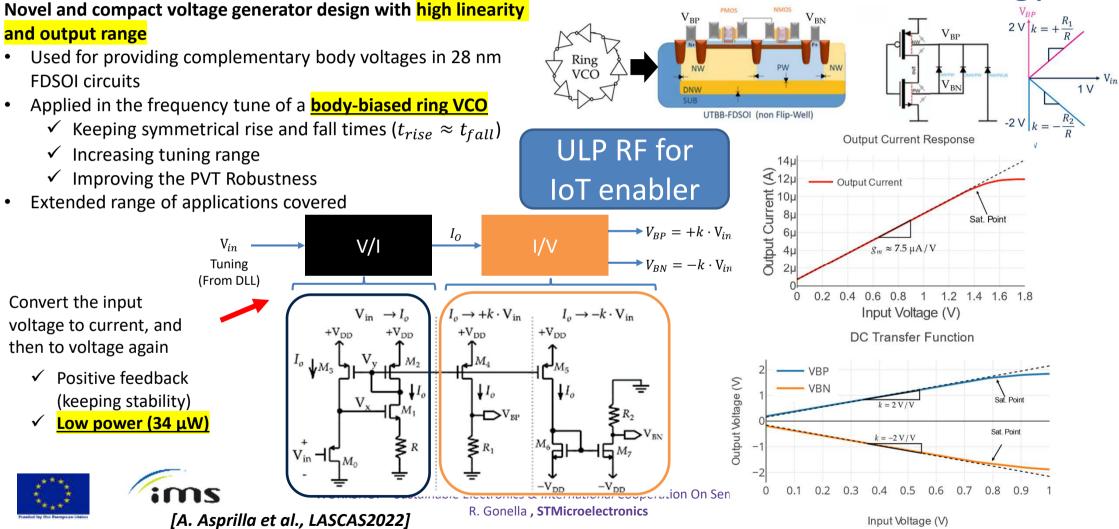

### Highly Linear Large Signal Compact Voltage-to-Current Converter in 28 nm FD-SOI Technology

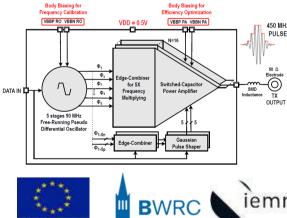

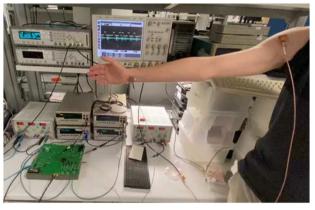

### Ultra-Low Power Transmitter for The Human Intranet in 28 nm FD-SOI

- Energy efficient transmitter to interconnect sensors and actuators on the human body. Medical • and wellness IoT applications

- Capacitive Body-Coupled Communication in the 400-500 MHz band with dominant surface wave propagation

- Highly duty-cycled transmitter with pulse-based communication in 28 nm FD-SOI

- Body-biasing optimization and calibration

- FBB on power amplifier (+/- 2.2) V for improved power efficiency

- FBB on ring oscillator for frequency tuning

- Ultra-low voltage operation (0.5V)

- Unlocked frequency reference

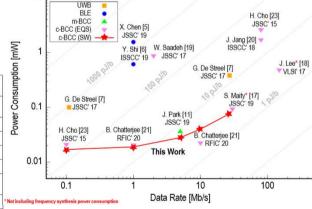

#### **Energy efficient** TX at the state of the art

Flexible data rate (100kb/s to 27 Mb/s) with 17 to 76 µW power consumption (170 to 2.8 pJ/b)

|                                                                                          | This             | Work      | 1               | Cho<br>23]<br>SC'15     | J. Lee<br>[18]<br>VLSI' 17           | W. Saadeh<br>[19]<br>JSSC <sup>*</sup> 17 | J. Jang<br>[20]<br>JSSC' 19 | S. Maity<br>[17]<br>JSSC'19 | [<br>RFI | atterjee<br>21]<br>C' 20 | J. Park<br>[11]<br>JSSC'19 |              | e Streel<br>[7]<br>SC'17 | X. Chen<br>[5]<br>JSSC' 19 | Y. Shi<br>[6]<br>ISSCC' 1 |

|------------------------------------------------------------------------------------------|------------------|-----------|-----------------|-------------------------|--------------------------------------|-------------------------------------------|-----------------------------|-----------------------------|----------|--------------------------|----------------------------|--------------|--------------------------|----------------------------|---------------------------|

| Radio<br>Technology                                                                      | C-I<br>(S        | BCC<br>W) |                 | BCC<br>QS)              | C-BCC<br>(EQS)                       | C-BCC<br>(EQS)                            | C-BCC<br>(EQS)              | C-BCC<br>(EQS)              | (E       | BCC<br>QS)<br>802.15.6   | M-BCC                      |              | WB<br>802.15.4a          | BLE                        | BLE                       |

| Process 28nm<br>Technology FD-SOI                                                        |                  | 6         | 5nm             | 65nm                    | 65nm                                 | 65nm                                      | 65nm                        | 6                           | 5nm      | 65nm                     |                            | 8nm<br>D-SOI | 40nm                     | 65nm                       |                           |

| Carrier<br>Frequency [MHz]<br>Supply<br>Voltage [V]<br>Data rate<br>[Mb/s]<br>Modulation | 350 - 550<br>0.5 |           | 13.56           | 56 20 - 60<br>140 - 180 | Baseband<br><100MHz                  | 20 - 120                                  | 20 - 60<br>100 - 180        | Baseband<br><100MHz         | 22.27    |                          | 40                         | 3500 - 4500  |                          | 2400                       | 2400                      |

|                                                                                          |                  |           | 1.2 1           | Not<br>Reported         | 1.1                                  | 1                                         | 1                           | 0.7                         |          | 0.6                      | 0.55                       |              | 0.6                      | 1.2                        |                           |

|                                                                                          | 0.1              | 27        | 0.1             | 80                      | 100                                  | 2                                         | 80                          | 30                          | 1        | 10                       | 5                          | 0.11         | 27                       | 1                          | 1                         |

|                                                                                          | 0                | эк        | оок             | BPSK                    | Decision<br>Feedback<br>Equalization | P-OFDM<br>BPSK                            | QPSK<br>BPSK                | NRZ                         | 0        | OK                       | оок                        | BPM          | I/BPSK                   | GFSK                       | GFSK                      |

| TX Power<br>Consumption [µW]                                                             | 17               | 76        | 21              | 2600                    | 0.35*                                | 870                                       | 1700                        | 93*                         | 20.6     | 22.4                     | 37                         | 100          | 380                      | 490                        | 610                       |

| TX Energy<br>per bit [pJ/b]                                                              | 170              | 2.8       | 210             | 32.5                    | 3.5                                  | 435                                       | 22                          | 3.1                         | 20.6     | 2.24                     | 7.2                        | 950          | 14                       | 490                        | 610                       |

| Output<br>Power [dBm]                                                                    | -33.8            | -19.7     | Not<br>Reported |                         | Not<br>Reported                      | Not<br>Reported                           | Not<br>Reported             | Not<br>Reported             |          | Not                      | -24.8                      | -20          |                          | -19                        | -8.4                      |

| TX System<br>Efficiency [%]                                                              | 2.44             | 14        |                 | Not                     | Not<br>Reported                      | Not<br>Reported                           | Not<br>Reported             | Not<br>Reported             |          | Not                      | 17.8                       |              | 2.6                      | 2.6                        | 23.6                      |

| Area [mm <sup>2</sup> ]                                                                  | 0.0              | 418       | 0.1672          | 5.76                    | 0.00348                              | 0.54                                      | 1.3                         | 0.02                        | 0        | 117                      | 0.0204                     | 0            | .095                     | 0.0166                     | 0.494                     |

[G. Tochou et al., RFIC 2021 29 and JSSC, May 2022]

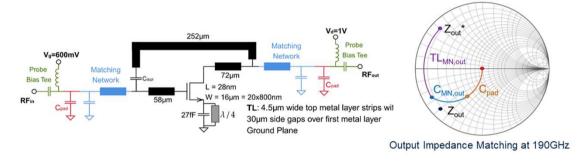

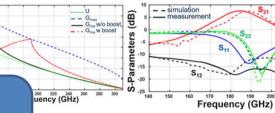

# One stage gain boosted power driver at 184 GHz in 28 nm FD-SOI CMOS

- Investigation for 28nm FD-SOI potential for next generations of standards (66)

- Carrier frequencies above 100GHz; High data rates

- Power amplifier with positive feedback to enhance the limited available gain

- One stage amplifier with gain boosting embedding

- Analytical methodology to design the required embedding

- Meticulous layout and electromagnetic simulations of passive elements

- State of the art performances:

- Best in class trade-off for gain/power consumption

- For the same technology

- 3.6dB extra gain

- Power consumption reduced by 35%

- Demonstration of mm-Wave/THz potentialities for 28nm FD-SOI technology

[S. Sadlo et al., RFIC 2021] WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors

**Towards 200GHz**

integration in

**FD-SOI**

R. Gonella , STMicroelectronics

[12] [13]

[14]

|            | f <sub>max</sub><br>(GHz) | Operation<br>Freq. (GHz) | Gain<br>Boosting | Structure | Gain<br>(dB) | Gain/Stage<br>(dB) | P <sub>sat</sub><br>(dBm) | BW<br>(GHz) | peak PAE<br>(%) | P <sub>DC</sub> /Stage<br>(mW) | FOM       | Area<br>(mm <sup>2</sup> ) |

|------------|---------------------------|--------------------------|------------------|-----------|--------------|--------------------|---------------------------|-------------|-----------------|--------------------------------|-----------|----------------------------|

| I          | 390                       | 184                      | Yes              | 1 CS      | 7.6          | 7.6                | -3.7                      | 20          | 4.2             | 5.1                            | 1.30      | 0.12                       |

|            | 280                       | 173                      | Yes              | 3 CE      | 18.5         | 6.2                | 0.9                       | 8.2         | -               | 14                             | 1.65      | 0.40                       |

|            | 280                       | 183                      | Yes              | 1 Case.   | 9.5          | 9.5                | -2.8                      | 8.5         | -               | 30                             | 1.27      | 0.16                       |

|            | 395                       | 242                      | Yes              | 4 CS      | 13.9         | 3.48               | -3.3                      | 29.7        | 1.6             | 6                              | 0.85      | 0.142                      |

|            | 352                       | 257                      | Yes              | 4 CS      | 9.2          | 2.3                | -3.9                      | 12.2        | 0.8             | 6.9                            | 0.91      | 0.14                       |

| JS         | 395                       | 247/272                  | Yes              | 2 CS      | 18/15        | 9/7.5              | 0.09/-2.36                | 5           | 4.4/2.4         | 10.8                           | 3.11/2.64 | 0.28                       |

| 5nm CMOS   | 395                       | 280/300                  | Yes              | 3 CS      | 12/9         | 4/3                | -4.7/-5.3                 |             | 1.6/1.4         | 6                              | 1.26/1.15 |                            |

| 0nm CMOS   | 275                       | 213                      | No               | 9 CS      | 10.5         | 1.17               | -3.2                      | 13          | 0.75            | 4.7                            | 0.79      | 0.12                       |

| 30nm SiGe  | 450                       | 200                      | No               | 2 Casc.   | 17           | 8.5                | -3.5                      | 44          |                 | 9                              | 1.40      | 0.24                       |

| anm FD-SOI | 390                       | 160                      | No               | 4 CS      | 15.7         | 3.93               | 1.3                       | 23          | -               | 8                              | 0.42      | 0.34                       |

$*FOM = \frac{\sqrt[n]{Gain}}{U(f)}$ : where n is the number of stages and U(f) is the unilateral power gain of the device at the frequency of operation.

30

### AI – FDSOI (and we did not ask ChatGPT!)

### AI computing at the edge

#### **Edge AI poses significant restrictions:**

- Amount of on-chip storage (for activations, and weights)

- Die size (cost)

- Energy consumption (e.g. for battery operation)

#### What we are looking for:

- Ease of reconfigurability/programmability (to support for different types of networks and products)

- Computation at reduced precision to save cost and power (neural networks often work well with reduced)

- Processing performance in the TOPs range.

- High efficiency in terms of TOPs/Watt and TOPs/mm2

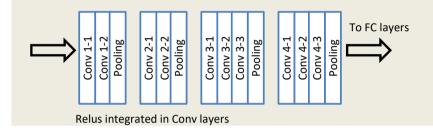

Desoli et al., ISSCC 2023

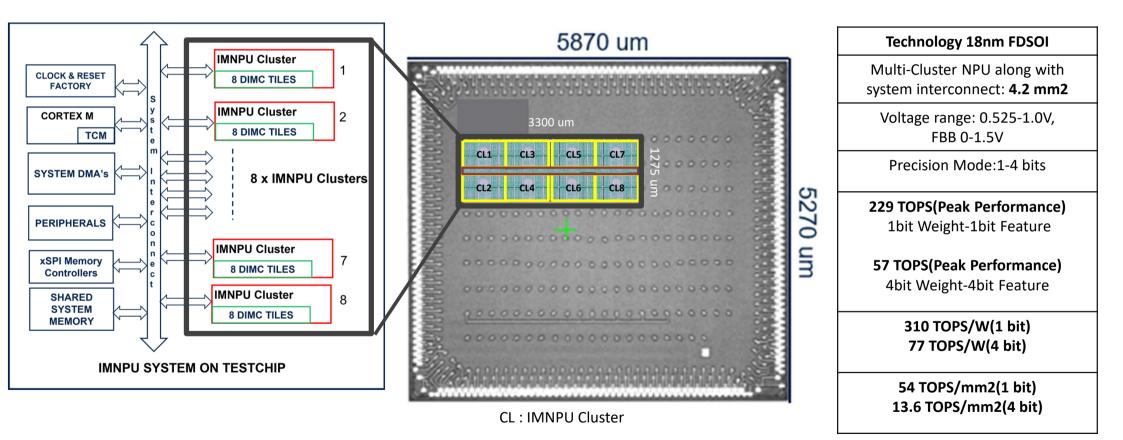

### **IMNPU** integration in 18nm FDSOI

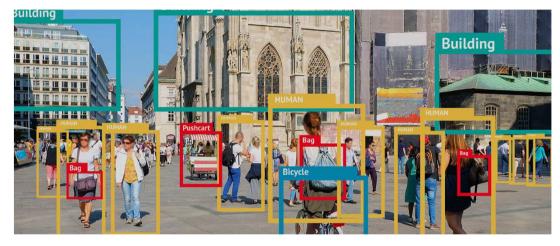

### Real world performance evaluation

**Object detection with VGG16**

International Cooperation On Semiconductors

(scaled down version @ 112x112 pixel resolution)

#### Measured at 0.525V and 600MHz with 1.5v FBB

| configuration | # of<br>MACS | # of<br>cycles/inf | Inf/sec | TOPS/W |

|---------------|--------------|--------------------|---------|--------|

| 1 cluster     | 8.15E+08     | 602513             | 996     | 46.8   |

| max clusters  | 0.15E+00     | 87719              | 6840    | 40.0   |

Very slow system frequency for battery powered always-on applications

Example: always on inference running on a dynamic partition\*\*

~1.6 GOPs/inf image object detection @ 10FPS -> 300 350uW @ 6 MHz + I/O power + Camera sensor (e.g. Sensor consumption: 200-300uW\*) -> 1-1.5 years on 2 AA batteries

\* e.g. <u>https://www.himax.com.tw/products/cmos-image-sensor/always-on-vision-sensors/hm01b0/</u> \*\* Assumption: with embedded ePCM for weights

Desoli et al., ISSCC 2023

### Al in FDSOI – Take-away

- Al applications in edge devices require a specific focus on cost and energy efficiency.

- A dataflow orient architecture has been used to integrate DIMC tiles into a Neural processing Unit (NPU).

- Our 18nm FDSOI SoC integration demonstrates the potential of in-memory computing tiles integrated in a NPU architecture for AI processing in edge devices.

| System                   | NVIDEA Titan X                  | ST ORLANDO                 | ST STM32N6                                        | This work<br>4-bit mode   | This work<br>1-bit mode |

|--------------------------|---------------------------------|----------------------------|---------------------------------------------------|---------------------------|-------------------------|

| Technology               | 16FF                            | 28nm FDSOI                 | 16FF                                              | 18nm FDSOI                | 18nm FDSOI              |

| Calc precision           | floating point single precision | 16-bit signed fixed point  | 8-bit signed fixed point/<br>integer scale offset | 4-bit signed, fixed point | 1-bit                   |

| Power efficiency         | 0.0439 FLOPS/W                  | 2.9 TOPS/W                 | up to 5 TOPS/W                                    | 77 TOPS/W                 | 310 TOPS/W              |

| Peak calculation density | 0.023 FLOPS/mm <sup>2</sup>     | 0.188 TOPS/mm <sup>2</sup> | 0.72 TOPS/mm <sup>2</sup>                         | 13.6 TOPS/mm <sup>2</sup> | 54 TOPS/mm <sup>2</sup> |

#### Desoli et al., ISSCC 2023

## FDSOI Augmented platform – take aways

- Augmented FDSOI platform enable ST and his partner to address multiple domain of today semiconductor applications

- Versatile, with the extra knob brought by the *fourth terminal*, enable extremely low-power application, to implement **sustainable** and eco-friendly devices

- Simple, hence highly manufacturable technologies, enabling a wide range of scalable applications

- FDSOI derivative embedded-non-volatile and RF evolutions offers ST and his partners an **economically sustainable** roadmap

### Aknowledgements

- The authors would like to warmly thanks all ST colleagues who contributed to the development of FDSOI, his derivative technologies solutions and the numerous R&D and commercial implementations from Crolles, Agrate, Grenoble, Rousset, Greater Noida,... ST premises without whom many of these foils wouldn't have been materialized

- Special thanks to ST Fellows Franck Arnaud, Andreia Cathelin, Andrea Redaelli, Nitin Chawla, Giuseppe Desoli

- A last word for our partners from CEA-LETI in Grenoble for their instrumental contribution to the FDSOI birth and growth

### THANK YOU

This project has received funding from the European Union's Horizon Europe research and innovation programme under GA N° 101092562

www.icos-semiconductors.eu

WORKSHOP - Sustainable Electronics & International Cooperation On Semiconductors